Устройство для обработки цифровых данных

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке универсальных систем обработки цифровой информации, в частности при моделировании работы систем управления подвижными звеньями специализированных роботов-манипуляторов . Цель изобретения - расширение функш1ональных возможностей за счет подсуммирования переноса из предьщущего разряда. С целью реализации функций полного сумматора устройство содержит с пятого по восьмой элементы памяти (ЭП) 5-8 соответственно и третий переключатель 11, причем пятый, шестой и седьмой ЭП образуют вторую цепь обратной связи , вход которой подключен к выходу четвертого ЭП 4, а выход - к первому информационному входу устройства. Кроме того, вход 48 записи, тактовый 49 и запрещающий 50 входы восьмого ЭП 8 соединены соответственно с первым 13, вторым 14 и вспомогательным 41 актовыми входами устройства, а размыкающий 51 и переключающий 51 контакты переключателя 11 подключены соответственно к запрещающему входу 53 первого ЭП 1 и выходу 54 восьмого ЭП 8. 1 ип. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1424008 А1 (51) 4 G 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMV СВИДЕТЕЛЬСТВУ и (щ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4046532/24-24 (22) 03,04.86 (46) 15.09.88. Бюл. М 34 (71) Уфимский авиационный институт им.Серго Орджоникидзе (72) З.М.Гафаров, P М.Галиулин, К.Ф.Тагирова и Ш.Ф.Гафуров (53) 681.325.5 (088.8) (56) Авторское свидетельство СССР

Р 197281, кл. С 06 F 7/50, 1966.

Авторское свидетельство СССР

В 1200431, кл. Н 03 М 7/16, 1985. (54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ЦИФРОВЫХ ДАННЫХ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке универсальных систем обработки цифровой информации, в частности при моделировании работы систем управления подвижными звеньями специализированных роботов-манипуляторов. Цель изобретения — расширение функциональных возможностей эа счет подсуммнрования переноса из предыдущего разряда. С целью реализации функций полного сумматора устройство содержит с пятого по восьмой элементы памяти (ЭП) 5-8 соответственно и третий переключатель

11, причем пятый, шестой и седьмой

ЭП образуют вторую цепь обратной связи, вход которой подключен к выходу четвертого ЭП 4, а выход — к первому информационному входу устройства.

Кроме того, вход 48 записи, тактовый

49 и эапрещающий 50 входы восьмого

ЭП 8 соединены соответственно с первым 13, вторым 14 и вспомогательным

41 тактовыми входами устройства, а размыкающий 51 и переключающий 51 контакты переключателя 11 подключены соответственно к запрещающему входу 53 первого ЭП 1 и выходу 54 восьмого ЭП

8. 1 ип.

1424008

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке универсалъньrx систем обработки цифровой информации, в частности при моделирова5 нии работы системы управления подвижными звеньями специализированных роботов-манипуляторов.

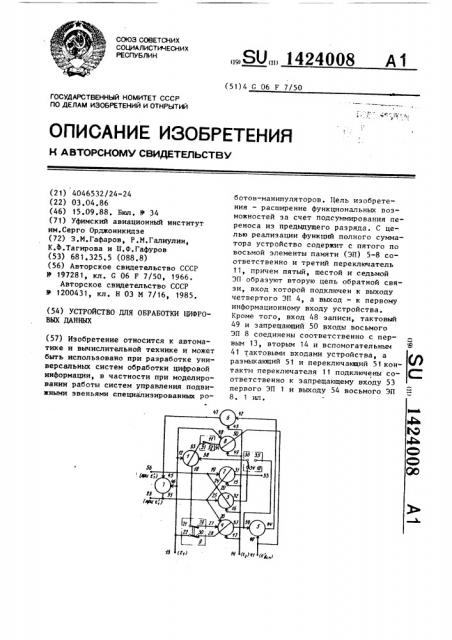

Цель изобретения — расширение функ10 циональных воэможностей путем подсуммирокания переноса из предьщущегоразряда, Па чертеже представлена структурная схема устройства для обработки цифровых дан»»ых.

Устройство для обработки цифровых данных содержит восемь элементов 1-8 и".bëò:» и трп переключателя 9-11. Тактовий вход 12 первого элемента 1 памяти =оедпнен с первым тактовым входом 13 устройства, второй тактовый кход 14 которого подключен к тактоlib входам 15-17 соответственно второго 2. третьего 3 и четвертого 4 эле-25 ментов памяти, выход 18 первого элеманта 1 памяти соединен с входом 19 з,пп»сп второго элемента 2 памяти, с запращающпм входом 20 третьего элемента 3 памяти и переключающим контактом ? 1 первого переключателя 9, 30 игор и псрекгпочающпй Izo»ITQi ò 22 которого подклю.-»а к парному тактовому входу I 3 устройства перкььй»»нформацпоп ый кход 23 I.îòîðîãî соединен с запращ»пощпм входом -4 гторого элемен- 35 та и: — мят»», с входом 25 записи третьего элема 3 памяти и первым входом

26 записи чатвертого элемента 4 памяти, второй вход 27 записи и запрещающий вход 28 которого подключены 40 сооткетсткенпо к первому 29 и второму

30 раз»пгка щцм контактам первого переключателя 9„выходы 31 и 32 соотвеlcтванно кторого 2, третьего 3 элементов памяти соединены с выходом 33 устройства и размыкающим контактом

34 э,орого переключателя 10, замыкающий 35 и переключающий 36 контакты которого подключены соответственно к вью оду 37 четвертого 4 и входу 38 50 записи первого элемента 1 памяти.

Вход 39 записи и тактовый вход 40 пятого элемента 5 памяти подключены соответственно к выходу 37 четвертого э,пемента 4 памяти и вспомогательному тактовому входу 41 устройства, вход 42 записи и тактовый вход 43 шестого элемента 6 памяти соединены соответственно с выходом 44 пятого элемента 5 памяти и вторым тактовым входом 14 устройства, вход 45 записи и тактовый вход 46 седьмого элемента

7 памяти подключены соответственно к выходу 47 шестого элемента 6 памяти и к первому тактовому входу 13 устройства, вход 48 записи, тактовый 49 и запрещающий 50 входы восьмого эпемента 8 соединены соответственно с первым 13, вторым 14 и вспомогательным 41 тактовыми входами устройства, размыкающий 51 и переключающий 52 контакты третьего переключателя 11 подключены соответственно к запрещающему входу 53 первого 1 и выходу 54 восьмого 8 элементов памяти, а выходы 18 z» 55 первого 1 и седьмого 7 соответственно элементов памяти соединены с вторым 56 и первым 23 соответственно информационными входами устройства, Элементь» 1-8 памяти служат для приема, хранения и выдачи в определенные моменты времени единицы (1 бита) информации. Если на вход записи поступает сигнал " 1", элемент памяти запоминает информацию путем перехода в новое (единичное) состояние. Длинная информация может бьггь считана с элемента памяти путем подачи сигнала счи,ывания на тактовый вход элемента памяти. При этом на его выходе появляется сигнал "1", а элемент памяти возвращается в исходное (нулевое) состояние.

Если же в момент записи информации на запрещающ»»й вход элемента памяти также подан сигнал, запись "1" в элемснт памяти не производится.

При наличии двух входов записи и запрещающего входа элемент памяти может быть использован для реализации (на входе) логической операции И, при этом входные переменные на входы sanucu и тактовый импульс на запрещающий вход элемента памяти подаются одновременно.

При объединении выходов двух элементов памяти на их общем выходе реализуется логическая операция ИЛИ.

Операция ИЛИ в устройстве реализована также на одном элементе (элементе 5) памяти. Входные переменные подаются на один и тот же вход 39 элемента, но в разные моменты вреь»ени. При считывании информации с данного элемента на его выходе 44 появ1474008

I где С вЂ” частичная сумма, образу»оща/

4 яся при сложении двух разрядов Х и У, слагаемых, ляется сигнал, соответствующий логической сумме входных переменных, Устройство для обработки цифровых даннь»х работает следующим образом.

В режиме работы "Полный сумматор" замыкаются контакты 21,29 и 22,30 пе- / реключателя 9, контакты 34,36 переключателя 10 и контакты 51,52 перекл»очателя 1 1 . 10

Перед суммированием в момент времени все элементы 1-8 памяти устанавливаются в исходное (нулевое) состояние (для простоты схема установки

"0" не показана).

В момент времени t на тактовый вход 13 устройства подается импульс первого такта, на тактовый вход 41 импульс вспомогательного такта, а на информационные входы 23 и 56 устрой20 ства — сигналы, соответствующие разрядам Х„и V слагаемых (i=1 2,3...n) (в устройстве "1" представляется наличием, а "0" — отсутствием сигнала).

Если Х„ =1, то в элемент 3 памяти записывается "1" и запрещается запись информации в элемент 2 памяти. Если

Y„" =1, то в элемент 2 памяти записы// // вается 1, а запись информации в элемент 3 запрещается. Если Х =У =1 то ь с э 30 запись и»»форл»ации в элементы 2,3 памяти не происходит.

Действие каждого сигнала Х; =1 и

У; =1 в;отдельности на входах 26,27 элемента 4 памяти выбрано меньпп»м действия тактового с»»гнала на его входе 28, поэтому запись информации в данный элемент производится лишь при

Х =У„ =1 (происходит превышение порога,устанавливаемого сигналом запрета).

Записи "1" в элемент 8 памяти по его входу 48 при t не происходит

1 вследствие того, что на его запрещающем входе 50 присутствует импульс такта t» . Кроме того, так как ис- 45 ходкое состояние элементов 1,5>7 памяти соответствует "0", при t, сигналы на их выходах отсутствуют.

В момент времени t, на вход 14 устройства подается импульс второго 50 такта, считывающий информац»»»о с элементов 2-4, 6,8 памяти, при этом на общем выходе элементов 2,3 памяти реализуется логическая операция

/ /, Значение С/ записывается при ti в элемент 1 памяти по его входу 38.

На выходе 37 элемента 4 памяти появляется сигнал, соответствующий

П = где П, — частичный перенос, образующийся при сложении двух разрядов Х; и Y слагаемых.

/ в

Значение П, записывается при t в элемент 5 памяти по его входу 39.

При этом сигналы на выходах 47,54 эле. ментов 6 8 памяти отсутствуют, В новом такте (такте t ) с пода// чей импульса на вход 13 устройства (на входе 41 тактовый импульс при этом отсутствует) происходит считывание инд/ормации с элемента 17 памяти и запись " 1" в элемент 8 памяти.

При этом на выходе 18 элемента 1 па/ мяти появляется сигнал С», поступающий на входы 19,20,27 элементов 2-4 памяти, а на выходе 55 элемента 7 памяти появляется сигнал П»-» переноса от сложения предыдущих разрядов Х, < и У;„, поступающий на входы 24-26 элементов 2-4 памяти (в данном случае

Х;, =У,, =П,, =0).

//

В новом такте (такте t ) с подачей импульса на вход 14 устройства происходит считывание информации с элементов 2-4, 6, 8 памяти, при этом на общем выходе элементов 2,3 памяти реализуется логическая операция

l где С, — результат сложения (сумма) разрядов Х; и У, слагаемых.

Значение С, поступает в момент на выход 33 устройства, но запись его в элемент 1 памяти при этом не происходит, так как на его входе 53 присутствует запрещающий сигнал, считанньп» с элемента 8 памяти.

При " на выходе 37 элемента 4 памяти появляется также сигнал, соот-" ветствующий и,= С, 1,—.

// где П; — частичньп» перенос, образованньп» при сложен»п» значения частичной суммь» со зна-.е:»,»eì переноса из предыдущего (i-1)-го разряда.

I/ //

Значение Д, записывается при в элемент 5 памяти по его «ходу 39, при этом сигнал на выходе 47 элемента 6 памяти отсутствует.

В следующем такте (такте t< ) вновь происхо;тит подача тактовых импульсов на входы 13,41 устройства и подача

5 значений Х, +, и У;, Hà входы 23,56 устройства. В результате значение

Х > поступает на входы 24-26 элементов 2-4, значение Y;ff — на входы 20, 19,27 элементов 2-4, а на выходе 44 элемента 5 появляется сигнал, соответствующий

П, =11, г;те П вЂ” значение переноса в следующий (1+1)-й (старший) разряд, появля(ощийся в результат» сложения разрядов Х; и Y, c.тагаемь.х, / чпэчеrrtie п1 записывается при в эле:..ент 6 памяти по его входу 42, ттр» этом ttttc! "1" в элемент 8 памя"т» отсут(..тттует пследствтте наличия за- 25 преп /11(!щего пмттульса па его входе 50. (В (:птедуюп;см такте (t> ) происходит

1>эр;пг;э/1 Titite (!!»гнала С . =Х, т .;,< + 11< (f <

+Х, <„ Г, (Iiл 0(tt!(0 ..1 пьпээде элементов л,lм!.тTI 1,11(.1»te ко п(.рогo записы30 пает э и эл(".к вт 1 памяти форыироваГ

;и(- <.1 г(:;;(i Г =Х, (t„(Ite(выходе 37

Ъ Г!(1(е TTЛ (I! Iятт! 3 11с1 1(111!в KOTOpOI O э/»(;1".1 .плетс:T в эт!емент 5 п(амяти и

TeI1 з тпттсь э1(а<1е1»тя /?/Г . з элеменп а 6 в .::.". ..Iettò 7 па(!ятт! (и/и 1 шкоде 54 эле- "5 меттта 8 пам(тт11 сттг1(пл оп сут("..тпует), !

Г

В .Tte:Iyюп(с;1 i а т(тс (t, ) тат(топьпt импулт с подается толь!(о на вход 13 уст(эГ(й(тп», п результате чего происходит с 1т(тывантте ин(1(ормацтпт с элемен- 10 топ 1,7 памяти » запись " 1" в элемент

8 памяти, ll(I выходе 18 элемента 1 появляется сигнал С... поступающий на входы 19,20,27 элементов . .-4> на выходе 55 элемента 7 поятзляется сит »ал

tl/> Ttnc1.;TTaIom»tI на входы 2 -26 элеме1(тон 2-4.

II

В следую(пий момент (такт tg ) с пода те(! ттмпульс;1 на вход 14 устройства про!!сход!тт счтттт(ванне информации с 50 элементов 2-4,6,8 памяти ° Р результате на общем выходе элементов 2,3 паГ мяти реализуется сигнал С. > =С; <Л, +

+С„<<П„, записываемый в элемент 1 памяти на выходе 37 элемента 4 памяти 55

> и / реализуется сигнал П,,„=C.. t П„ > эаписываемътй в элемент 5 памяти, на выходе 14 элемента 8 памяти появляется

-!<гнал "1", запрещающий запись значе1424008 ния С;+, в элемент 1 памяти, на выходе 47 элемента 6 памяти при этом присутствует сигнал "0".

В новом такте (такте и ) с поступлением тактовых импульсов на входы

13,41 происходит считывание значения

/ II

П;«. =П1>< + (1, f с элемента 5 памяти и подача значений Х,>q Y „на информационные входы 23,56 устройства. В дальнейшем работа устройства аналогична описанной вьппе.

Если после появления на выходе 33 устройства сигнала С„ на элементе 5

15 памяти с((тормировалось значеIтие 1(>т =1 > то оно последующими тактовыми импульсами продвигается через элементы 6,7, 8 памяти и с выхода 32 элемента 3 памяти поступает на выход 33 устройства в качестве старшегоразряда С„,„ 1 суммы, т. е. устройство правильно работает при любых значениях Х,, Y>,Ï;-<

При работе устройства в режиме

"Полусумматор" замыкаются контакты

21,29 и 22,30 переключателя 9, контакты 35,36 переключателя 10 и раэмыка(отся контакты 51,52 переключателя

11> ocуществляет сложение двоичного кода с "1" младщего разряда. Последняя подается на вход 56 устройства в момент tf одновременно с первым разрядом двоичного кода„ поступающим на вход 23 устройства. В такте t, на выходе 33 устройства появляется сигнал, представляющий собой результат сложения двух разрядов,, с выхода 37 элемента 4 памяти на вход 38 элемента 1 памяти поступает сигнал переноса от сложения указан!тык разрядов, который в последующих тактах складывается с очередным разрядом двоичного кода, и т,д.

Тактопьп! вход 41 устройства при работе его в режиме Полусумматор на испо;тьэуется.

Дтт>т работы устройства в режиме Двоичный код ->код Грея достаточно замкнуть контакты 35,36 переключателя 10 и разо.!кнуть контакты 21,29 и

2?>30 переключателя 9 и контакты 51, 52 перекл1очателя 11, при этом входы

41,56 у(тройства не используются, а на вход 23 при каждом такте t подаются разряды преобразуемого двоичного кода (старшими разрядами вперед).

Каждый разряд двоичного кода запоминается в элементе 4 памяти, затем в такте tz переписывается в элемент 1 памяти для последующего сложения с

1424008

Составитель. M.Есенина

Техред М.Ходанич 1 орректор С.Шекмар

Редактор А.Маковская

Заказ 4688/51 Тираж 704 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 1К-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 очередным разрядом двоичного кода, поступающим на вход 23 устройства. Разряды кода Грея (старшим разрядом вперед) снимаются при каждом такте с выхода 33 устройства.

Для обратного преобразования кода

Грея в двоичный код достаточно замкнуть контакты 34,36 переключателя

10 и разомкнуть контакты 21,29 и 22, 30 переключателя 9 и контакты 51,52 переключателя 11. При этом входы 4 1

56 устройства также не используются, а на вход 23 при каждом такте t no1 даются разряды преобразуемого кода

Грея (старшим разрядом вперед) ° При каждом такте t с вьмода 33 устройства снимается очередной разряд двоичного кода, который благодаря обратной связи также запоминается в элементе

1 памяти. В следующем такте ty осуществляется сложение его со следующим разрядом кода Грея на элементах 2,3 памяти и т.д.

Формула изобретения

Устройство для обработки цифровых данньм, содержащее четыре элемента памяти и первый и второй переключатели, причем тактовый вход первого элемента памяти соединен с первым тактовым входом устройства, второй тактовый вход которого подключен к тактовым входам второго, третьего и четвертого элементов памяти, выход пер- 35 вого элемента памяти соединен с входом записи второго элемента памяти, с запрещающим входом третьего элемента памяти и первым переключающим контактом первого переключателя, второй 40 переключающий контакт которого подключен к первому тактовому входу устройства, первый информационный вход которого соединен с запрещающим входом второго элемента памяти, с входом 45 записи третьего элемента памяти и первым входом записи четвертого элемента памяти, второй вход записи и запрещающий вход которого подключены соответственно к первому и второму размыкающим контактам первого переключателя, выходы второго и третьего элементов памяти соединены с выходом устройства и раэмьпсающим контактом второго переключателя, замыкающий и переключающий контакты которого подключены соответственно к выходу четвертого и входу записи первого элементов памяти, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет возможности подсуммирования переноса из предыдущего разряда, оно содержит пятый элемент памяти, вход записи и тактовый вход которого подключены соответственно к выходу четвертого элемента памяти и вспомогательному тактовому входу устройства, шестой элемент памяти, вход записи и тактовый вход которого соединены соответственно с выходом пятого элемента памяти и вторым тактовым входом устройства, седьмой элемент памяти, вход записи и тактовый вход которого подключены соответственно к выходу шестого элемента памяти и первому тактовому входу устройства, восьмой элемент памяти, вход записи, тактовый и запрещающий входы которого соединены соответственно с первым, вторым и вспомогательным тактовым входами устройства, и третий переключатель, размыкающий и переключающий контакты которого подключены соответственно к запрещающему входу первого и выходу восьмого элементов памяти, а вьмоды первого и седьмого элементов памяти соединены соответственно с вторым и первым информационными входами уст1 ройства.