Последовательный сумматор-вычитатель

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ и устройствах обработки цифровой информации. Цель изобретения - расширение области применения. Сумматор-вычитатель содержит элементы И 1-6, элементы ШШ 7-9, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ Ю, 11, триггеры 12, 13, входы и выходы устройства. Пос;;едовательный сумматор-вычитатель реализован по структуре синхронного автомата Мура (последовательностной схемы). 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 4 G 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АBTOPCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4125127/24-24 (22) 29.09,86 (46) 15.09.88. Бюл. М- 34 (72) С.Л. Титов, Ю.Ф. Рощинский и Е.Н. Титова (53) 68 1,325.5(088.8) (56) Каган Б.М., Каневский М.M. Цифровые вычислительные машины и системы, М.: Энергия, 1974, с. 237, рис. 2-78.

Авторское свидетельство СССР

Ф 1363 191, кл. G 06 F 7/50, 1986. (54) ПОСЛЕДОВАТЕЛЬНЪ|И СУММАТОР-ВЪ|ЧИТАТЕЛЬ

„„SU„, 1424009 А1 (57) Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ и устройствах обработки цифровой информации. Цель изобретения — расширение области применения.

Сумматор-вычитатель содержит элементы И 1-6, элементы ИЛИ 7-9, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 10, 11, триггеры

12, 13, входы и выходы устройства.

Последовательный сумматор-вычитатель реализован по структуре синхронного автомата Мура (последовательностной схемы) . 1 ил .

1424009 1-->следе>»а г> «tt>ttt tt« су >ма t о1 -вь! |||та- 35 тель реализован по с руктуре синхронпcго ;«Uòî;.t»òë 11ура (пocледoваTåë«>нсстной схемы), Первьй — шестой элемснгы И 1 — 6, первый 7 и второй 8 элементы ИЛ11 образуют коыб««««ац««о«!«|ую 40 схему, которая Формирует текущую

1>ункцию возбуждения для элементов памят«-, когUptì««являются первьй 12 и второй 13 три.-гер|,, определяющих текущее внутреннее состояние после- 45 дс вательностной схемы. Первьй 10 и

» opo«t 11 элементы ИСКЛ101й0ЦЕЕ ИЛИ и третий элемент ИЛИ 9 образуют комб||нац«to«t«tpю схему, формирующую Teê щ >е значение выходного бита в завпс««у«ости от значений теку«««их бит первс>го и второго операндов, поступающ«|х на прямые и инверсные входы первого 14, 15 и второго 16,17 операндов соответственно и текущего внутреннего состояния схемы, определяем >го первым 12 и вторым 13 триггерами. Седьмой-десятый элементы И 2730 служат г«>«я формирования в начале

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах

ЭВ11 и устройствах обработки цифро««ой

5 информации.

Цель изобретения — расширение области применения.

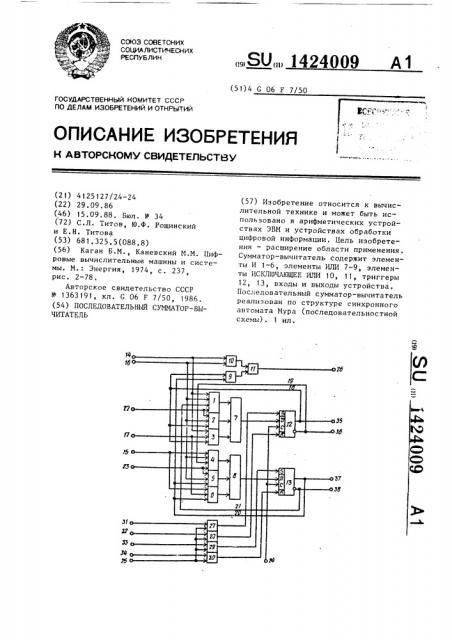

На чертеже изображена схема последовательного сумматора-вычитателя. 1<

Последовательный сумматор-вычитатель содержит первый — шестой элементы И 1-6, первьй — третий элементы

ИЛИ 7-9, первый 10 и второй 11 элемепть! ИСКЛ10Ч««10ЩЕЕ ИЛИ, первый 12 и »торой 13 триггеры, прямой 14 и ин-. версный 15 входы первого операнда, прямой 16 и ||нверсный 17 входы ВТо рого операнда, прямой 18 и инверсный

19 входы переноса иэ предыдущего ра>p«ttjà, прямой 20 и инверсный 21 входы заема иэ предыдущего разряда, управляющий вход 22 сложения, управляющий вход 23 вычитания, вход 24 такт||ров анп««, вход 25 установки, выход 26 сумматора-вычитателя, седьмой — де>-.ятый элементы И 27-30, пря t>эй 3! «|нверсный 32»ходы переноса иэ пр дь«дущего устройства, прямой 33 и

«|«!»ерсный 34 входы э,! су«с! иэ предыду30 ще"о устройст»а, прямой 35 и инверс««ьв! 36 в-яхсды перенос» в следующее устр»йс гво, ttp>tt to«l 37 «! ««««вс рсный 38

» ь! ходы ас. M в с:! clip t>>tttcе уc pойство . каждого цикла вычисления стимулирующих сигналов для принудительной предустановки триггеров 12,13 в зависимости от состояния сигналов переноса и заема из предыдущего каскада (предыдущего сумматора-вычитателя).

Последовательный сумматор-вычитатель работает следующим образом.

В начале каждого цикла вычисления на вход 25 установки поступает единичный импульс. В зависимости от состояния сигналов переноса и заема, которые поступают из предыдущего каскада соответственно на пары входов

31, 32 и 33, 34 (причем присутствие единичного потенциала сразу на двух прямых входах переноса и заема является запрещенной комбинацией), триггеры 12 и 13 устанавливаются в соответствующее (нулевое или единичное) состояние.

Затем по прямому 14 и инверсному

15 входам первого операнда и прямому

16 и инверсному 17 входам второго операнда начинают последователъно поступать биты чисел соответственно первого (уменьшаемого) и второго (вычитаемого) слагаемых. Поступление каждого бита операндов сопровождается тактовыми сигналами, поступающими по входу 24 тактирования, при этом число тактовых импульсов, поступающих по входу 24 тактирования, равняется разрядности операндов.

Для наглядности описания положим, что в начале цикла вычисления выполняется операция сложен!«я. В этом случае по управ««я«!»««еыу входу 22 сложения поступает единич«п и потенциал, а по управляющему входу 23 вычитания — нулевой потенциал. После прихода очередных бит операндов в зависимости от их з««аче««ия и значе!«ия с«|гнала на прямом входе 18 переноса, который поступает с прямого выхода первого триггера 12, на выходе второго элемента ИСКЛ10ЧА10ЩЕЕ ИЛИ 11 формируется выходной бит суммы. Комбинационная схема, образованная первым— третьим элементами И 1-3 и первым элементом ИЛИ 7, формирует функцию возбуждения (сигнал лог. "0" или лог. "1 ) для первого триггера 12.

С приходом тактового импульса по входу 24 тактирования значение сигнала с выхода первого элемента ИЛИ 7 переписывается в первый триггер 12. Им будет определяться внутреннее состояние устройства в следующем такте

1424009 вычисления. Нл выходе второго элемента ИЛИ 8 ня нсе время ныполнения оперлции сложения будет пригуTl.-òâîвать сигнал лаг. О, тлк клк четвертый 4 и пятый 5 элемен гы И блокируются сигналом лаг. О с упрлнляющего входа 23 вычитания, а шестой элемент

И 6 закрыт нулевым потенциалом с прямого выхода второго триггера 13.

После смены выполняемой оперлции, что определяется появлением сигнала лог. "О на управляющем входе 22 сложения и сигнлла лог. 1" на управляющем входе 23 вычитания, на выходе первого элемента ИЛИ 7 генерируется

Ii сигнал лог. 1 функции возбуждения первого триггера 12 до тех пор, пока по прямому входу 14 первого операнда поступают единичные биты уменьшаемо20 го, а первый триггер 12 находится в единичном состоянии. Если же хотя бы

15 одно из указанных выше услоний не выполняется или поступает единичный бит вычитаемого по прямому входу 16 второго операнда, то нл ныходе первого элемента ИЛИ 7 до канцл цикла вычисления будет генерироваться сигнал

t l 11 лог. 0 . На выходе второго элемента

ИЛИ 8 сигнал функции возбуждения вто30 рого триггера 13 ряз примет единичное значение н случае единичного бита на прямом входе 16 второго операнда при нулевых значениях на прямом входе 14 первого операнда и прямом выходе первого триггера 12.

После этого цикл вычисления продолжается с генерацией сигналов на входе 20 заема. ственно первого и второго элементов

ИЛИ, входы первого элемента ИЛИ соединены с выходами первого, второго и третьего элементов И, входы второго элемента ИЛИ соединены с выходами четвертого, пятого и шестого элементов И, прямой вход первого операнда сумматора-вычитателя подключен к первым входам пернсго элемента ИСКЛ10ЧАЮЩЕЕ ИЛИ и первого и третьего элементов И, инверсный вход первого операнда сумматора-нычитателя соединен с первыми входами четвертого

55

Ф о р м у л а и з о б р е т е н и я 40

Последовательный сумматор-вычитятель, содержащий шесть элементов И, три элемента ИЛИ, два элемента !ICY:ÉÎЧАЮЩЕЕ HJIH H T H e, D-входы которых подключены к выходам соотнет- 45 и шестого элементов И, прямаи вход второ г.о оперл яда с умма та рл -нычитлте— ля подключен к вторым нхадлм перногc) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первого, второго, четнертого и пятого элементов И, инверсный вход второго операнда сумматора-нычитлтеля соединен с вторыми входами третьего и шестого элементов И, прямой выход первого триггера соединен с первым входом третьего элемента ИЛИ и третьими нходами втсрого и третьего элементон

И, инверсный выход первого триггера подключен к третьему входу четвертого элемента И, прямой ныход второго триггера соединен с вторым входом третьего элемента ИЛИ и третьими входлми пятого и шестого элементов

И, инверсный выход второго триггера подключен к третьему входу первого элемента И, управляющий вход сложения сумматор l-âí÷èòàтpëÿ подключеH к четнертому входу первого элемента

И и первому входу второго элемента

И, управляющий вход нычитлния сумматора-нычитлтеля подключен к четвертому входу четвертого элемента И и перному входу пятога элементл И, входы второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ соединены с выхадлми первого элемента ИСКЛ1ОЧА1ОЩЕr; 1УП1 и третьеro элемента ИЛИ, а выход является выходом результата сумматора-нычитлтеля, тактовый вход кат р го соединен с тактовыми входами триггеров, о тл и ч л ю щ и и с я тем, что, с целью расширения области применения, н него введены седьмой, несытой, девятый и десятый элементы И, первые входы которых подключены к входу установки сумматора-вычитателя, а нтсрые входы подключены соответстненно к прямому и инверсному входам переноса и прямому и инверсному входам заема сумматора †вычитате, выхо. ы седьмого и восьмого элементов И подключены соответственно к S u

R-входам первого триггера, прямой и инверсный выходы которого являются соответственно прямым и инверсным выходами переноса сумматора †нычитлте, а выходы девятого и десятого элементов И подключены соответственно к

S- u R-входам второго триггсрл, прямой и инверсный выходы которого являются соответственно прямым и инверсным выходами заема суммлтара-вычитателя.