Одноразрядный сумматор-вычитатель

Иллюстрации

Показать всеРеферат

Изобретение относятся к вычислительной технике и предназгитчоно для реализации в составе БИС с И1гаекционным питанием. Целью изобретения является упрощение суьгматора-вычитателя. В одноразрядный сумт атор-вычитатехгь, содержащий три входных транзистора 1, 2, 3 и четыре выходных транзистора 7, 8, 9, 12, введен дополнительный транзистор 13 и орга)Н1 зованы новые связи согласно вьфажениям реализуемых функций, представленных в арифметическоь Г)лзисе,1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИ Х

РЕСПУБЛИК

А1

ÄÄSUÄÄ 1424013 (5ц 4 G 06 F 7!50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (2 1) 4187293/24-24 (22) 28.01.87 (46) 15.09.88. Бюл. Му 34 (71) Таганрогский радиотехнический институт им. В.Д. Калмыкова (72) Ю.И. Рогозов, А.В. Ерохин и Н.И. Чернов (53) 681.325.5(088.8) (56) Авторское свидетельство СССР

9 1137462, кл. G 06 F 7/50, 1985.

Авторское свидетельство СССР

В 1335892, кл. G 06 Г 7/50, 1986. (54) ОДНОРАЗРЯДНЬЙ СУМ".1АТОР-В1.1 1ИТАТЕЛЬ (57) Изобретение относится к вычислительной технике и предназначено для реализации в составе ВНС с инжекционным питанием. Целью изобретения является упрощение сумм-.)тора-вычитателя. В одноразрядный сумматор-иычитатель, содержащий три вхоцгн,ж транзистора 1, 2, 3 i четыре выходных транзистора 7, 8> 9, 12 введен дополвительный транзистор 13 и организованы новые связи согласно выражениям реализуемых функций, представленных B арифметическом базисе,1 и I, 1424013

40

S P„(7, +Ь„+Р, )1) 45

ПзOбpeTеlflfе «TIIOCIITeff K Bf.f flп.JIH тельной тгхникб и может быть использовано при построении арифметических устройств с инжекционным питанием на основе 77ebff НТоВ многоуровнеffoH Io гики.

Пень изобретения — упрощение сумматора-вычитателя.

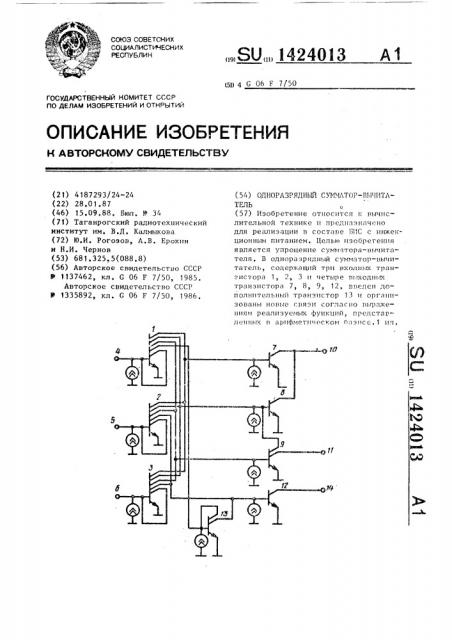

На чертеже представлена функциональная схема одноразрядного сумматора-вычитателя, Одноразрядный сумматор-вычитатель содержит три входных транзистора 1, 2, 3, базы которых соединены соответственно с входами первого 4 и второго 5 операндов и входом 6 переноса, первые, вторые и третьи коллекторы тра гнсторов 1-3 соединены соответств еll ll о с ба з lи!1 выходных Tра н 3 ис торов 20

7-Ч, коллекторы транзисторов 7 и 8 соединены с выходом 10 результата, два коллек гора транзистора 9 соединены соответственно с базой транзистора 8 и выходом 11 переноса, база тран-25 зисторон 2 ll 3 — с коллектором транзистора 13, база которого соединена с .етнертым коллектором транзистора

1, а коллектор транзистора 12 соединеll с выходной шиной 14 заема, тран- 30 зисторы 1, 2, 3, 13 включены по схеме зеркальногo отражения, что достигаетс» соединением одного из коллекторов с базой, в результате чего токи выходных коллекторов этих транзисторов

35 раfff«их входным токаи.

Фу» кции суммы, разности, переноса и заема однораз рядного сумматора-вычитателя имеют следующий ff«д:

-P,(;l,+ b + Р; ) 2)+Р, (а,+Ь,+Р, .)3);

F-,„= P (а„+ Р„ + Ь, )2);

U,,I= Р,(a, + Ь, + Р„ 2).

Как видно из приведенных соотношений, для реализации функций Р, Р, Р» Р4 используются одни и те же аргументы Ilo различным порогBM (одни H же мна околлекторные транзисторы для образования суммы). Причем в базы транзисторов 1, 2, 3, 13 инжектор задает один квант тока Т, а в базы транзисторов 7, 8, 9, 12, выполняющих55 функции порогового детектора, задаются токи, значения которых указаны в арифиетическом представлении реализуемых функций и их предикатов Р,, Р» Р,, Р„, Для надежности срабатыв7ния пороговых детекторов токи берутся на 0,5 кванта меньше, чем указано в выражениях. В базу транзисторов 7 инжектор задает ток 0,5 I,, в базу транзистора 8 — 2,5 I, а в базы транзисторов 9,12 — 1,5 I . Указанные соотношения токов обеспечиваются соотношением геометрических размеров эмиттера и коллектора инжекционного транзистора, Одноразрядный сумматор-вычитатель работает следующим образом.

Предположим, на входы устройства подается следующая комбинация входных сигналов: а, = Ь, = P, = 1. В этом случае транзисторы 1, 2, 3 открыты и отводят через свои коллекторы по одному кванту тока. С баз транзисторов 7-9 будет отбираться три дискрета тока, с базы транзистора 12 два дискрета тока, а так как их базовые токи меньше указанных значений, то эти транзисторы закрыты. Закрыт и транзистор 13, так как его базовый ток отводит транзистор 1. Таким образом, все пороговые детекторы будут закрыты, т,е. и S 19 рч 1 U бб 1

Предположим, что а„= Ь = 1, Р„= О. В этом случае транзисторы

7, 9, 13 закрыты, так как их базовые токи меньше отводимых входными транзисторами. Транзисторы 8 и 12 открыты, так как с их баз отводятся токи соо ветственно 2 I< и I, которые меньше задаваемых токов (2,5 Т, и

1,5 1).

Это приводит к появлению на выходах сигнала

W=S=0;U;„=0;P«=1.

При a; = Р, = О, Ь, = 1. транзистор 1 закрыт, транзистор 9 насыщен и шунтирует транзистор 8, последний закрыт, транзистор 13 открыт и отводит I с базы транзистора 12, транзистор 2 отводит I с базы транзистора 12, т.е. с его базы отводится ток, равный двум дискретам, поэтому транзистор 12 закрыт. На выходных шинах формируются сигналы

S = W = 1; Р;б = О, У;бб= 1.

142 013 формула изобретения

Составитель M. Есенина

Техред M,Õîäàíè÷ Корректор С. Черни

Редактор А. Маковская

Заказ 4688/51 Тираж 704 Подписное

ВНИИПИ Грсударственного комитета С CP по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

При Ь, Р„0, л 1 rрлн«ис тор 7 закрыт, транзистор 9 нлсыщен и шунтирует транзистор 8. Транзистор

13 закрыт, я транзистор 12 открыт.

На выходных ип нах формируются сигналы

S = W = 1 P „= 0, Б,„= 0.

Одноразрядный сумматор-вычитатель, содержащий три входных многоколлекторных транзистора, включенных по схеме зеркального отражателя, и четыре выходных транзистора, включенных по схеме порогового детектора, причем первые, вторые и третьи коллекторы входных транзисторов соединены соответственно с базами первого, второго и третьего выходных транзисторов, 20 четвертые коллекторы второго и третьего входных транзисторов соедин» ьн I с базой четвертого выходного транзистора, коллекторы первого и второго вывыходных транзисторов соединены с выходом результата суммлтора-n»r итлтеля, первый и второй коллекторы третьего выходного транзисторл соединены соответственно с базой второго выходного транзистора и выходом перенося сумматора-вычитателя, я коллектор четвертого выходного транзистора — с BMxojIQM заема сумматора-вычитателя, о т л и ч а ю шийся тем, что, с целью упрощения сумматора-вычитателя, введен дополнительный транзистор, включенш и по схеме токового отражателя, блз» которого соединена с четверTblM коллектором первого входного трлнзисторл, а коллектор — с базой четвертого выходного транзистора.