Устройство для установки микропроцессоров в исходное состояние

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в микропроцессорных системах с параллельной обработкой информации , а также в мультипроцессорных системах повышенной надежности и устройствах для проведения входного контроля БИС в условиях серийного производства. Цель изобретения - расширение класса решаемых задач устройства путем обеспечения установки в исходное состояние микропроцессорной системы с параллельной обработкой информации, состоящей из п-микропроцессоров . Устройство содержит тактовый генератор 1, соединенный с п микропроцессорами 2, узел 3 счета времени и элемент ИЛИ-НЕ. Устройство обеспечивает установку в исходное состояние и взаимную синхронизацию работы с точностью до машинного такта п микропроцессоров, а также возможность синхронизации работы микропроцессоров одновременно с медленно действующими внешними устройствами. 3 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

re 4 С 06 1 11/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4086841/24-24 (22) 09.07.86 (46) 15.09.88. Бюл. М 34 (72) В.К. Антуфьев (53) 681.326.7(088.8) (56) Авторское свидетельство СССР

Ф 1061147, кл. С 06 Р 11/22, 1982.

8080 Microprocomputer Systems

User s Manual. Фирменный материал фирмы Intel. СИА, 1975, с. 5-3. (54) УСТРОЙСТВО ДЛЯ УСТАНОВКИ МИКРОПРОЦЕССОРОВ В ИСХОДНОЕ СОСТОЯНИЕ (57) Изобретение относится к вычисЛительной технике и может быть использовано в микропроцессорных сис— темах с параллельной обработкой информации, а также в мультипроцессорных системах повышенной надежности ьSU„„1424018 А1 и устройствах для проведения входного контроля БИС в условиях серийного производства. Цель изобретения — расширение класса решаемых задач устройства путем обеспечения установки в исходное состояние микропроцессорной системы с параллельной обработкой информации, состоящей из и --микропроцессоров. Устройство содержит тактовый генератор 1, соединенный с и микропроцессорами 2, узел 3 счета времени и элемент ИЛИ-НЕ. Устройство обеспечивает установку в исходное состояние и взаимную синхронизацию работы с точностью до машинного такта п микропроцессоров, а также возможность синхронизации работы микропроцессоров одновременно с медленно действующими внешними устройствами. 3 ил.

1424018

Изобретение относится к вычислительной технике и может быть исполь25 зовано, например, в многопроцессорных системах с параллельной абработ5 кой информации, построенных на базе микропроцессоров серии 580.

Цель изобретения — расширение класса решаемых задач путем обеспечения одновременной установки группы микропроцессоров.

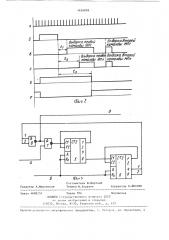

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — временная диаграмма ега работы, на фиг. 3— функциональная. схема узла счета времени.

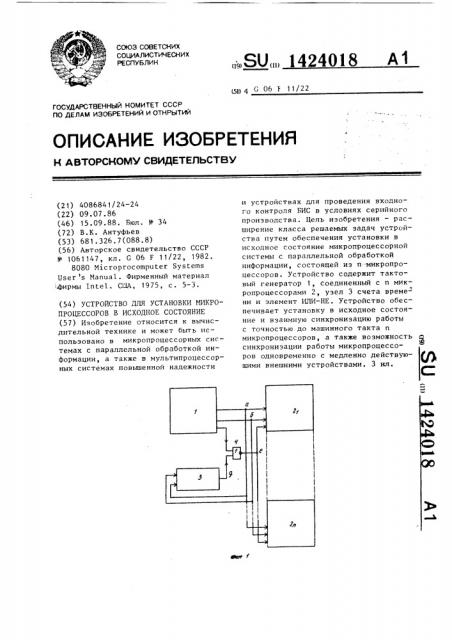

Устройство (фиг. 1) содержит тактовый генератор 1, выполненный, например, на БИС 580 ГФ 24, соединенный с входами микропроцессоров 2 (например, типа 580 ВМ 80) и узла 3 счета времени, и элемент ИЛИ-НЕ 4.

Узел 3 счета времени (фиг. 3) содержит двоичные счетчики 5 и 6, элемент И-НЕ 7 и дешифратор 8.

Устройство для установки микропроцессоров в исходное состояние работает следующим образом.

Тактовые импульсы с выхода генератора 1 (фиг. 2а) поступают на тактовые входы микропроцессоров 2 и узла 3. Импульс сброса, вырабатываемый генератором 1 (фиг. 2б) и синхронизированный с тактовыми импульсами, поступает на микропроцессоры 2 и сбрасывает их. Одновременна импульсом сброса на выходе узла 3 (фиг. 2д) устанавливается сигнал высокого уровня, а на выходе элемента ИЛИ-НЕ 4 (фиг. 2е) — сигнал готовности низко° I го уровня. По заднему франту импуль- 40 са сброса происходит запуск счетчиков 5 и 6 узла 3. Па истечении временного интервала t синхронно с тактовыми импульсами на выходе дешифратора 8 узла 3 устанавливается напря- 45 жение низкого уровня (фиг. 2д), а на входах готовности микропроцессоров 2 — напряжение высокого уровня (фиг. 2е). По истечении временного интервала и после окончания сигнала 59 сброса первый микропроцессор 2 начинает выборку первой команды (фиг. 2в), и-й микропроцессор 2 начинает выборку первой команды по истечении временного интервала t< (фиг. 2г). Лля 55 обеспечения работоспособности устройства должно выполняться условие

t, t (. Как следует из временных диаграмм, микропроцессоры 2 начинают выборку первей команды асинхронно.

В связи с тем, чта на входах микропроцессоров 2 поддерживается сиг-, нал готовности низкого уровня, происходит удлинение циклов выборки всех микропроцессоров 2 до момента установления высокого уровня сигнала готовности. Этим обеспечивается синхронное завершение цикла выборки первой команды. Выборка и выполнение второй и всех последующих команд микропроцессорами 2 происходит синхронно с точностью до такта импульсов синхронизации.

При необходимости синхронизации работы микропроцессоров 2 с медленно действующими внешними устройствами сигнал готовности с выхода генератора 1 поступает на вход элемента ИЛИ-НЕ 4 и далее — на входы микропроцессоров 2. Обработка сигнала готовности каждым микропроцессором происходит аналогично прототипу.

Предлагаемое устройство обеспечивает синхронизацию и микропроцессоров с точностью до машинного такта в системе с параллельной обработкой информации.

Ф а р м у л а и з о б р е т е н и,я

Устройство для установки микропроцессоров в исходное состояние, содержащее тактовый генератор, первый и второй выходы которого являются соответствующими выходами устройства для подключения к входам тактовых импульсов и сброса микропроцессоров соответственно, о т л и ч а— ю щ е е с я тем, что, с целью расширения класса решаемых задач устройства, в него введены элемент ИЛИ-НЕ и узел счета времени, причем первый и второй выходы тактового генератора подключены соответственно к тактовому входу и входу сброса узла счета времени, выход которого и третий выход тактового генератора соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ, выход которого является выходам устройства для подключения к входам готовности микропроцессоров.

1424018

Составитель В.Вертлиб

Техред М.Ходанич Корректор С.Шекмар

Редактор А.Маковская

Заказ 4688/51

Тираж 704 Подписное

В11И111И Государственного комитета СССР

Ilo делам изобретений и открытий

113035, Москва, Ж-35, Раушгкая наб., д. 4/5

Производственно-п лиграфическое предприятие, г. у :город, ул. Проектная, 4