Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть испольэовано в качестве внешнего оперативного запоминаютего устройства для мини- ЭВМ, а также в системах многоканального сбора, хранения и последуинвей обработки данных, построенных на базе миниЭБМ или микроэвм. Целью изобретения является повьшение быстродействия устройства при циклическом обратении к одноименным элементам нескольких массивов данных. Устройство содержит блок 3 оперативной памяти, счетчик 2 относительного адреса, регистр 4 числа массивов, регистр 5 номеров массивов, блок 6, включакяций блок постоянной памяти, счетчик базопого адреса, элемент НЕ, два элемента И и элементы ИЛИ. В блоке постоянной памяти хранятся базовые адреса массивов данных. Перед вводом или выводом данных в регистр 4 вводится число массивов, к которым может быть проведено обращение, в регистр 5 - номера активных массивов, к которым будет проводиться обращение, а на входы счетчика 2 - относительный адрес элемента массива. В соответствии с кодом числа массивов, номером активного массива и состоянием счетчика базового адреса последовательно выбираются из блока постоянной памяти базовые адреса, которые вместе с относительным адресом из счетчика 2 образуют действительный адрес, по которому вьтолняется ввод или вывод одноименных данных из блока 3. Таким образом, обеспечивается циклическое обращение к одноименным элементам нескольких массивов данных без необходимости вводить действительный адрес перед каждым обращением , что повьппает быстродействие устройства . 2 ил. (Л tsD СЛ

СОЮЗ С ЭВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 4 G 11 С 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ с

1 ° 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4198137/24-24 (22) 20.02.87 (46) 15.09.88. Бюл. М 34 (72) А.А.Абрамов, В.А.Иванов, В.А,Кондалев и В.А.Степанов (53) 681.327(088.8) (56) Авторское свидетельство СССР

11 1179429, кл. G ll С 11/00, 1984.

Микропроцессорные средства и системы, 1986, У 2, с. 62-65. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть исполь- . зовано в качестве внешнего оперативного запоминающего устройства для миниЭВМ, а также в системах многоканального сбора, хранения и последующей обработки данных, построенных на базе миниЭВМ или микроЭВМ. Целью изобретения является повышение быстродействия устройства при циклическом обрашеиии к одноименным элементам нескольких массивов данных, Устройство содержит блок 3 оперативной памяти, счетчик 2 относительного адреса, регистр 4 числа массивов, регистр 5 номеров массивов, блок 6, включающий

„„SU„„1424054 А1 блок постоянной памяти, счетчик базового адреса, элемент HF. два элемента И и элементы ИЛИ, В блоке постоянной памяти хранятся базовые адреса массивов данных. Перед вводом илн выводом данных в регистр 4 вводится число массивов, к которым может быть проведено обрашение, в регистр

5 — номера активных массивов, к которым будет проводиться обрашение, а на входы счетчика 2 — относительный адрес элемента массива, В соответствии с кодом числа массивов, номером активного массива и состоянием счетчика базового адреса последовательно выбираются из блока постоянной IlBMHTH базовые адреса, которые вместе с относительным адресом иэ счетчика 2 образуют действительный адрес, по которому выполняется ввод или вывод одноименных данных иэ блока 3. Таким образом, обеспечивается циклическое обращение к одноименным элементам нескольких массивов данных без необходимости вводить действительный адрес перед каждым обрашением, что повышает быстродействие устройства. 2 нл.

14 24054

Изобретение относится к вычислительной технике и может быть использовано и качестве внешнего оперативного запоминающего устройства для миниЭВМ, а также в системах многока5 нального сбора, хранения и последующей обработки данных, построенных на базе миниЭВМ или микроЭВМ.

Белью изобретения является повышение быстродействия устройства при циклическом обращении к одноименным элементам нескольких массивов данных.

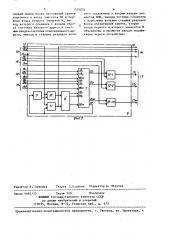

На фиг. и 2 представлена структурная схема предлагаемого устрой- 15 ства.

На фиг. 1 показан также блок сопряжения миниЭВМ, предназначенный для подключения устройства к миниЭВМ. 20

Устройство содержит (фиг. 1) счетчик 2 относительного адреса, блок 3 оперативной памяти, регистр 4 числа массивов, регистр 5 номеров масс ивов, блок 6, который с одержит 25 (фиг. 2) блок 7 постоянной памяти, счетчик 8 базового адреса, элемент

НЕ 9, перный 10 и второй 1 элементы И и элементы ИЛИ 12, На фиг. 1 и 2 обозначены: 13 вход модификации адреса устройства;

14 — ныходы младших разрядов; 15 выходы старших раэрядон; 16 — счетный вход счетчика относительного адреса;

17 — выходы базового адреса блока 3 оперативной памяти; !8i -18,„, 19 -19<>

20,-20„, — входы блока 7; 21, -21„„, 22 - выходы блока 7.

Регистр 4 предназначен для приема, хранения и выдачи значения количества массивов, к которым может быть

40 проведено обращение при выполнении операций ввода-вывода. Значение количества массивон заносится в регистр

4 в двоичном коде и может принимать значение 2" 2, где k 0,1, ° ФЭ 45

2"...; m О, 1, 2... - число разрядов регистра 4; 2 — максимальное число

1Ъ массивов, к которым может приводиться обращение.

Регистр 5 предназначен для приема, 50 хранения и вциачи номеров активных массивов, т. е. массивов, к которым будет проводиться обращение при выполнении операций ввода-вывода. Номера активных массивов заносятся в регистр 5 в позиционном коде. Каждый разряд позиционного кода представляет самостоятельное значение и определяет номер активного массива. Номера активных массивов могут принимать значения 1,2,3..., но не более значения, занесенного в регистр 4. Количество разрядов регистра 5 равно 2 т.е. равно максимальному числу массивов, к которым может проводиться обращение.

При информационной емкости устройства 2" слов количество суммы" выходов 14 и 15 равно и, число выходов 15 равно n — щ.

При максимальном количестве массивов, к которым может быть проведено обращение, равном 2, количестно входов регистра 5 равно m число выходов регистра 5 равно 2, число выходов счетчика 8 равно m.

Устройство работает следующим образом.

Рассмотрим работу устройства при выполнении операций ввода-вывода.

Перед началом ввода-вывода информации выполняется операция нвода в устройство следующих исходных данных: количества массивов, к которым может быть проведено обращение, номеров активных массивов, к которым будет проводиться обращение, относительного адреса первого элемента, с которого начинается ввод или вывод, т.е. адреса элемента относительно на вла массивов. Все эти данные поступают соответственно на входу регистра 4, регистра 5 и счетчика 2.

Формирование действительного адреса осуществляется следующим образом.

В соответствии с кодом количества массивов, кодом номеров активных массивов и текущим состоянием счетчика

8 из блока 7 выбирается базовый адрес одного из заданных активных массивов (при нулевом начальном состоянии счетчика 8 вырабатывается адрес массива с наименьшим номером), который определяет массив, к которому будет проводиться обращение. Базовый адрес приформировывается к относительному адресу, поступающему по входам 14 посредством соответствующих им элементов ИЛИ 12. В результате на входы блока 3 выдается действительный адрес, состоящий из п — m разрядов относительного адреса на входах 14 и m разрядов базового адреса на входах 17.

Если выполняется операция ввода, то на входы блока 3 поступает вводи4 4 ветствуюшим нулевому состоянию счетчика 8.

Таким образом, устройство обеспечивает циклическое обрашение к одноименным элементам нескольких массивов данных без необходимости пе ред каждым обрашением вводить в устройство действительный адрес элемента, состояший из базового адреса массива и относительного адреса элемента внутри массива, за счет чего достигается высокая скорость ввода-вывода информации, и, следовательно, повышается быстродействие устройства.

Запоминаюшее устройство, содержашее блок оперативной памяти и счетчик относительного адреса, входы которого являются адресными входами устройства, причем выходы (п — m) младших разрядов (где п 0,1,2... число адресных входов блока оперативной памяти и ш = 0,1,2... п — число старших разрядов адресных входов блока оперативной памяти) счетчика относительного адреса подключены к адресным входам младших разрядов блока оперативной памяти, выходы, информационные входы, вход обрашения и вход записи-чтения блока оперативной памяти являются информационными выходами и соответстнукшими нходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства при циклическом обрашении к одноименным элементам нескольких массивов данных, в устройство введены регистр числа массивов, регистр номеров массивов, счетчик ,базового адреса, первый и второй элементы И, элемент HE, m элементов ИЛИ и блок постоянной памяти, адресные входы первой и второй групп которого подключены соотнетственно к выходам регистра числа массивов и выходам регистра номеров массивов, входы которых являются входами задания номеров массивов устройства, причем выход элемента НЕ соединен с первым нходом первого элемента И, выход которого подключен к счетному входу счетчика базового адреса, выходы которого соединены с адресными входами третьей группы блока постоянной памяти, выходы группы которого подключены к первым входам элементов ИЛИ, управ3 142405 мая н устройство информация. Блок 3 по управляюшим сигналам осушествляет ввод и запоминание информации по действительному адресу, поступаюшему на его входы 14 и 17.

Если выполняется операция вывода, то блок 3 осушествляет считывание информации по адресу, поступающему на

его нходы 14 и 17, и выдает эту информацию на информационные выходы.

После формирования действительного адреса и окончания операции ввода-вывода по этому адресу на вход 13 поступает сигнал модификации адреса, в результате этого содержимое счетчика 8 увеличивается на единицу и иэ блока 7 в соответствии с новым состоянием счетчика 8 выбирается базовый адрес следуюшего по номеру ак 20 тинного массива. Новый базовый адрес аналогично описанному приформировывается к относительному адресу и по . этому действительному адресу выполняется операция ввода или вывода.

При этом обрашение будет происходить к элементу следуюшего активного массива, определяемому тем же OTHO сительным адресом, что и в предыдуВ шем обрашении. В результате выполнения, аналогично описанной выше последовательности действий по формированию действительного адреса и операций ввода-вывода обеспечивается последовательное обрашение к элементам с перным заданным относительным адресом всех активных массивов, т.е. обеспечивается последовательное обрашение к одноименным элементам, всех активных массивов.

Когда сформируется базовый адрес

40 последнего активного массива, на выходе блока 7 вырабатывается сигнал, который через элемент НЕ 9 блокирует прохождение сигнала с входа 13 через элемент И 10 на вход счетчика

8. Одновременно с этим разрешается прохождение сигнала с входа 13 через элемент И 11 на вход установки в нулевое состояние счетчика 8 и на счетный вход счетчика 2 для модификации 50 относительного адреса. После этого последовательно формируются действительные адреса аналогично описанному вьппе для нового относительного адреса. 55

При этом базовые адреса активных массивов начинают формироваться с массива с наименьшим номером, соотФормула изобретения

14 24054

Техред Л. Олийнык Корректор А. Обруча р

Редактор А. Лепнина

Заказ 469)/53 Тиразк 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Уигород, ул, Проектная, 4 ляющий выход блока постоянной памяти подключен к входу элемента HE и первому входу второго элемента И, выход которого соединен с входом. сброса счетчика базового адреса н счет а м входом счетчика относительного адреса, выходы m старших разрядов которого подключены к вторым входам элементов ИЛИ, выходы которых соединены с адресными входами старших разрядов

5 блока оперативной памяти, вторые входы первого и второго элементов И объединены и являются входом модификации адреса устройства.