Устройство для определения потери достоверности дискретной информации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - расширение функциональных возможностей. Устр-во содержит преобразователь 1 кода, формирователь 2 тактовых импульсов, эл-т ИЛИ 3, блок вццеления 8 синхросигнала, блок поиска 9 синхронизма и каналы вьщеления ошибок, каждый из которых состоит из блока выделения 4 ошибок, эл-та ИЛИ 5 и ключей 6 и 7. Цель достигается путем обеспечения вццеления ошибок различной кратности при переменной длине цикла передачи синхросигнала с помощью введенных блока выделения 8, блока поиска 9 и каналов вьделения ошибок. 2 ил.

СОЮЗ СОВЕТСжих

СОЦИАЛ "1СТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1424127 А1

1511 Н 04 В 3/46

ОПИСАНИЕ ИЗОьРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТ8У.CC

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

hO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4057932/24-09 (22 } 23. 04. 86 (46) 15.09.88. Бюл. М 34 (75) А. Н. Журавлев и А. С. Данилин (53) 621.395.664(088.8) (56) Мартынов Е. М. Синхронизация в системах передачи дискретных сообщений. М.; Связь, 1972, с. 188-190.

Авторское свидетельство СССР

У 5594011 кл. Н 04 В 3/46, 1975. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПОТЕ РИ ДОСТОВЕРНОСТИ ДИСКРЕТНОЙ ИНФОРМАЦИИ (57) Изобретение относится к электросвязи. Цель изобретения - расширение функциональных возможностей. Устр-во сод ржит преобразователь 1 кода, формирователь 2 тактовых импульсов, эл-т

KIH 3, блок выделения 8 синхросигнала, блок поиска 9 синхронизма и каналы выделения ошибок, каждый из которых состоит из блока выделения 4 ошибок, эл-та ИЛИ 5 и ключей 6 и 7 ° Цель достигается путем обеспечения выделения ошибок различной кратности при переменной длине цикла передачи синхросигнала с помощью введенных блока вью деления 8, блока поиска 9 и каналов вьщеления ошибок. 2 ил.

1424127

Изобретение относится к электросвязи и может использоваться в устройствах для оценки качества цифровых систем передачи путем измерения ошибок, 5 возникающих в каналах связи при передаче дискретной информации в виде группового цифррвого потока с синхрониэирукщими кодовыми словами, а также для цикловой синхрониэ ации цифровых /1О систем передачи.

Цель изобретения — расширение функциональных воэможностей путем выделения ошибок различной кратности при переменной длине цикла передачи син- 15 хросигнал а.

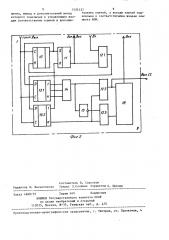

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 — пример структурной электрической схемы блока по- 20 иска синхронизма.

Устройство для определения потери достоверности дискретной информации содержит преобразователь 1 кода, формирователь 2 тактовых импульсов, эле-25 мент ИЛИ 3, блоки 4.1т41с выделения ошибок, где k †максимальн кратность выделяемой ошибки, дополнительные элементы ИЛИ 5.1 — 5k, ключи 6.1 — 6k, дополнительные ключи 7.!. — 7k блок 30

8 выделения синхросигнала и блок 9 поиска синхронизма, включающий первый счетчик 10, триггер 11, первый 12,1, второй 12.2.è третий 12.3 элементы И, первый 13.1 и второй 13.2 регистРы сдвига, элемент ИЛИ 14, инвертор 15 и второй счетчик 16.

Устройство работает следующим обра эои.

Исследуемый цифровой поток разделенЩ иа циклы, в каждом из которых содержится И двоичных символов синхросигнала (СС), представляющего собой постоянный М-иерный вектор. Этот цифровой поток (его можно рассматривать как после-45 довательный код)поступает на вход преобразователя 1 кода, в котором в каждый тактовый интервал умещается М.текущих символов потока, из которого одновреиенно формирователем 2 тактовых импульсов выделяется регулярная последовательность коротких импульсов. Полученные после преобразования параллельные коды, или текущие М-мерные век торы поступа т одновременно на входы 5 блока 8 выделения синхросигнала (CC) ,и блоков 4,1 - 4k выделения ошибок кратности 1,2,..., где k не превышает М. В случае опознания СС на выхо-I де блока 8 появляется короткий импульс длительностью в тактовый интервал, а в случае опознания ошибки любой кратности такой импульс возникает на одном из выходов одного иэ блоков 4. Сигналы сшибок одной кратности суммируются во времени соответствующим дополнительныи элементом ИЛИ 5 и подаются на соответствующий ключ 6, управлякщий сигнал для которого формирует блок 9 поиска синхронизма. Для этого тактовые импульсы подаются на вход первого счетчика

10 и на тактовые входы первого 13.1 и второго 13.2 регистров сдвига.

Первый счетчик 10 осуществляет подсчет тактовых импульсов, и при достижении заданного значения, определяемого длительностью цикла, на выходе первого счетчика 10 формируется короткий импульс, устанавливающий триггер 11 в состояние "11 и записываемый в первый регистр 13.1 сдвига. Записанный импульс с помощью тактовых импульсов продвигао ется по выходам первого 13 1 и и подается на соответствующие входы элемента ИЛИ 14. На выходе элемента

ИЛИ l4 формируется импульс, длительность которого равна времени прохождения импульса по выходам первого регистра 13.1 сдвига.

Потенциал логической "1" с выхода триггера 11 поступает на один из входов первого элемента И 12 ° 1 и разреша ет прохождение через него импульсов, поступивших на другой его вход. Импульс с выхода первого элемента Ч 12.1 записывается во второй регистр 13.2 сдвига, и с первого его выхода поступает на. установочные входы первого счетчика 10 и триггера II, устанавливая их в исходное состояние. С пос леднего выхода второго регистра 13.2 сдвига импульс поступает на одни входы второго l2.2 и третьего 12.3 элементов И, на другие входы которых поступает импульс с выхода элемента

ИЛИ 14 (на вход второго элемента

И 12.2 — непосредственно, а на вход третьего элемента И 12.3 — через инвертор 15). При совпадении по времени импульсов на входах второго элемента И 12.2 íà его выходе формируется сигнал наличия СС, являющийся импульсом для второго счетчика 16, а при несовпадении формируется импульс на выходе третьего элемента

И l2.3, которым осуществляется сброс

ыторого счетчика 16.

1424127

При отсутствии синхронизма на вь Очередной импульс с выхода первого ходе первого счетчика 10 образуются счетчика 10 формируется в нужной фазе. короткие импульсы с частотой циклов При этом происходит совпадение имс произвольной фазой относительно ис- пульсов на входах второго элемента

5 следуемого цифрового потока. Эти И 12.2, на его выходе формируются имциклоные импульсы подаются на вход пульсы, поступающие на второй счечпервого регистра 13.1 сдвига и на чик 16. После накопления заданного чиодин из входов триггера 1 и устанав- сла импульсов на выходе второго счетливают на его выходе сигнал логичес- 1р чика 16 формируется потенциал логической "1", поступающий на один из нхо- кой "1" и поступает на управляющие дов первого элемента И 12.1. входы ключей 6.1 — 61, открывая их.

Когда через вход блока 9 на другой При этом на входы элемента KIH 3 повход этого элемента поступает единич- ступают импульсы от кодовых комбинаный сигнал (который Mo_#_eT быть ныне- 15 ций с ошибками, а через дополнительленным синхросигналом или ложным сиг . ные ключи 7.1 — 7k на выходе устройналом), иа выходе перного элемента ства проходят импульсы ошибок соответИ 1 2.1 образуется импульс, поступаю- стнующей кратности . На управляющие щий на вход второго регистра 13.2 входы дополнительных ключей 7.1 - 7k сдвига. 20 поступают стробируищие импульсы с

Если это ложный импульс, то на дополнительного выхода блока 9 поиспервом выходе второго регистра 13.2 ка синхронизма. сдвига формируется импульс, задержан- Длины циклов, при которых обеспеный относительно входного на один чивает работу устройства блок 9, опретактовый интервал. Этим импульсом 25 деляются разностью между емкостью первый счетчик 10 и триггер 11 уста- первого счетчика 10 и его содержимым, навливаются н исходное состояние, при при котором формируется выходной иь этом прекращается дальнейшее прохож- пульс. дение импульсов через первый элемент

И 12.1. С последнего выхода второго 30 Ф о р м у л а и з о б р е т е н и я регистра 13.2 сдвига импульс подается на одни входы второго 12.2 и трв- Устройство для определения потери тьего 12.3 элементов И. На другие достоверности дискретной информации, их входы поступают импульсы с ныхода содержащее преобразователь кода, форэлемента ИЛИ 14. По времени импульсы 3 мирователь тактовых импульсов и элена входах второго 12.2 и третьего мент KIH о т л и ч а ю щ е е с я

12.3 элементов И не сонпадают. При тем, что, с целью расширения функциоэтом формируется импульс на выходе нальных возможностей путем выделения третьего элемента И 12.3 и сбрасыва- ошибок различной кратности при переет второй счетчик 16, с выхода кото- 4р менной длине цикла передачи синхросигрого потенциал логического "0" посту- нала, введены блок выделения синхропает на входы ключей 6.1 — 6k, запи- сигнала, блок поиска синхронизма и рая их. каналы ньщеления ошибок, число котоНа элемент KIH 3 поступают имп ль- рых равно кратности выделяемых ошибок сы только от неискаженных комбинаций 45 а каждый из которых включает последосинхросигнала, что уменьшает нероят- нательно соединенные блок выделения ность появления на выходе его ложных ошибок, дополнительный элемент ИЛИ, импульсов, а это, н свою очередь, ключ и дополнительный ключ, при этом уменьшает время вхождения н синхро- сигнальный вход преобразователя кода низм. соединен с входом формироватеЛя тактоСледующий импульс с выхода перво- ных импульсов, выход которого подго счетчика 10 поступает на входы ключен к тактовым входам блока поиспервого регистра 13.1 сдвига и триг- ка синхронизма и преобразователя когера 11, и цикл повторяется, При этом да, выходы которого подключены к обьот цикла к циклу происходит постепен- единенным соответствующим входам блоное смещение но времени импульсов на кон выделения ошибок и блока выделевыходе первого счетчика 10 к концу . ния синхросигнала, выход которого цикла цифрового потока, который да- через элемент ИЛИ подключен к сиглее фазируется синхроимпульсом. нальному входу блока поиска синхро5 1424127 6 низма, выход и дополнительный выход тельных ключей, а выходы ключей подкоторого подключен к управляющим вхо- ключены к соответствующим входам эледам соответственно ключей и дополниюг 2

Составитель В. Слепаков

Редактор Л. Веселовская Техред Л.Олийнык Корректор С. щекмар

Заказ 4698!57 Тираж 660 Под пи с но е

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4