Синхрогенератор

Иллюстрации

Показать всеРеферат

Изобретение относится к телевидению . Цель изобретения - упрощение устр-ва. Синхрогенератор содержит задаюишй г-р 1, счетчики 2 и 3, блоки 4 и 5 постоянной памяти (КПП), буферные регистры 6 и 7 и триггер 8 с установочным входом 9. Цель достигается путем сокращения объема памяти БПП 4 и 5. Это обеспечивается установкой такого режима работы, при котором считывание информации возможно только на время действия кадровых гасящих импульсов. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИА! 1ИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1424136 А1

t5D 4 " 04 N 5/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPGKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4093600/24-09 (22) 22 ° 07 ° 86 (46) l5 ° 09.88ь Бил. Р 34 (72) P.Ñ,Ëà÷èíîâ, Н.В.Белянина и Д.Д.Тупицын (53) 621.397.3 (088.8) (56) Техника средств связи. Серия

Техника телевидения, вып. 6, 1985 с. 77. (54) СННХРОГЕНЕРАТОР (57) Изобретение относится к телевидении. Цель изобретения - упрощение устр-ва. Синхрогенератор содержит за даищий г-р l, счетчики 2 и 3, блоки

4 и 5 постоянной памяти (БПП), буфер ные регистры 6 и 7 и триггер 8 с установочным входом 9, Цель достигает ся путем сокращения обьема памяти

БПП 4 и 5. Это обеспечивается уста новкой такого режима работы, при котором считывание информации возможно только на время действия кадровых гасящих импульсов. 2 ил.

1424136

Изобретение относится к технике телевидения и может быть использовано для формирования телевизионных синхросигналов.

Цель изобретения - упрощение устройства путем сокращения объема па мяти блоков постоянной памяти.

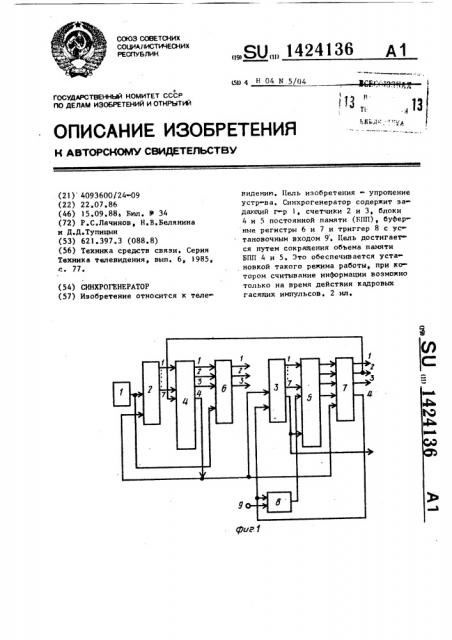

На Фиг.1 представлена электрическая структурная схема предлагаемого синхрогенератора; на фиг.2 - времен ные диаграммы, поясняищие его работу.

Синхрогенератор (фиг.))содержит задающий генератор l, первый и вто. рой счетчики 2 и 3, первый и второй блоки 4 и 5 постоянной памяти, первый и второй буферные регистры 6 и 7, триггер 8, установочный вход 9 °

Синхрогенератор работает следуищим образом. 20

Первый и второй блоки 4 и 5 постоянной памяти с органиэацией 256w4 бит содержат по дне области памяти. В первом блоке 4 в первой области памяти хранится информация, соотнетствуи25 щая режиму раэнертки строки (фиг ° 2аг), a во второй - режиму развертки полустроки (фиг.2д - э). В первом случае при считывании информации формируится соответственно временные иитерна3п лы, эквивапентные длительности строчного гасящего импульса (СГИ), строчного синхроимпульса (ССП), развертки строки, а во втором случае формируится соответственно временные интервалы, эквивалентные длительности уравниваи щего импульса для образования врезок, развертки половины строки.

Режим считывания содержимого пер ного блока 4 задается одним из выход40 ных сигналов первого буферного регистра 4, предварительно формируемым на выходе второго блока 5 ° Этот сигнал модифицирует адрес первого блока 4 памяти, обеспечивая доступ ко второму 45 в области памяти.

Во втором блоке 5 памяти имевтся две области дпя четного (фиг.2п †.н) и нечетного (Фиг.2о - с) полукадрон.

Для каждого из полукадров на выходах второго блока 7 при считывании инфор-., мации Формируются соответственно нремениые интерналы для кодирования цве товой синхронизации, временные интервалы, эквивалентные длительности

55 уравиинаищих H JIscos и врезок кад рового синхроимпульса, а также импульс установки и "0" второго счетчика 3.

Посредством импульса установки в

"0" второго счетчика 3, формируемого на одном иэ выходов второго буферного регистра 7, осуществляется также изменение состояния триггера 8 ° если по era установочному входу 9 paspemeна чересстрочная развертка.

Во втором блоке 5 памяти области четного и нечетного полукадров хранятся соответственно в ячейках адреса 0-127 и 128-255; старшим разрядом адреса можно обеспечить доступ к одному иэ них. Перекличение осущестнляется посредством изменения выходного сигнала триггера 8, являищегося Т триггером. Изменение состояния триг гера 8 и выбор поочередно четных и нечетных полукадрон возможны только тогда, когда по установочному входу

9 триггера 8 разрешена чересстрочная развертка. В противном случае т.е. когда по установочному входу 9 и триггера 8 задан режим прогрессивной развертки, состояние триггера 8 фиксировано и не зависит от входных сигналон, поступаищих на счетный вход, В зависимости от значения фиксированного выходного напряжения триггера 8 ("0" или ")") в режиме прогрессивной развертки Формируится сннхросигналы, соответствуищие либо только четным, либо только нечетным полукадрам.

Кадровые гасяшие импульсы (КГИ) генерирувтся на выходе старшего (9-го разряда) второго счетчика 3. Их воз действие на вход второго блока 5 обеспечивает такой режим работы, когда счить)ванне информации возможно только на время действия ГКИ. Тем самым осуществляется экономия объема памяти второго блока памяти.

Первый счетчик является семиразрядным. Установка в "0" первого и вто рого счетчиков 2 и 3 происходит с по мощьи импульсов, поступающих с ныко да первого блока 4 постоянной памяти или с выхода первого буферного регист ра 6 соответственно. Первый и второй буферный регистры 6 и 7 испольэувтся с целью устранения динамических пог решностей, обусловленнъ1х переходными процессами в первом и втором блоках б и 7 и временными задержками сиг налон в схеме. Вапись информации с их выходов в первый и второй буферные регистры 6 и 7 производится по заднему Фронту синхронизируиших им пульсон, B то время как счет н перз 1424136 вом и втором счетчиках 2 и 3 осу» При достижении вторым счетчиком 3

I ществляется по переднему фронту соот- значения 322 на выходе второго блока ветствующих тактовых импульсов. Зяда- 5 и соответствующем выходе второго ющий генератор 1 с кварцевой стабили буферного регистра 7 Формируется снг5

11 11 з ацией частоты вырабатывает импульсы нал, устанавливающий в 0 в торой с периодом, и е пре вешающим минимал ь счетчик 3 . ный интервал, определяемым телеви зионным стандартом . Тактовая частота Формула изобретения задающего генератора l может быть 10 Синхрогенератор, содержащий после выбрана кратной строчной, например довательно соединенные задающий гене2 МГц. ратор, первый счетчик, первый блок

Тактовые импульсы с выхода эада- постоянной памяти н 11ервый буферный ющего генератора 1 поступают на счет- регистр, первый, второй и третий вьгный вход семиразрядиого первого счет- 15 ходы которого являются первыми выхода чика 2 ° Первый счетчик 2 считывает ми синхрогенератора, последовательно содержимое первого блока 4. При от- соединенные второй счетчик, второй сутствии управляющего сигнала с вы блок постоянной памяти и второй бухода второго буферного регистра 7, Ферный регистр, первый, второй и тре что соответствует режиму развертки 20 тий восходы котороао являются вторыстроки, на выходах первого блока 4 ми выходами синхрогенератора, при фориируются временные интервапы, эк- этом второй выход второго буферного вивалентные СГИ и ССИ. При этом на регистра соединен с вторым входом пер» его соответствующем выходе через вре- вого блока постоянной памяти, выход иенной интервал, соответствующий 25 управления которого соединен с вхоительности строки (64 мкс), форин- дом установки в "0" первого счетчируется сигнал, устанавливающий первый ка, а выход задающего генератора сое счетчик 2 в исходное (нулевое) сос- динен с входом управления первого тояние. Последний адресует первому буферного регистра, о т л и ч а ю блоку 4 нулевой адрес и на его выхо- З0 шийся тем, что ° с целью упроще де вновь восстанавливается исходныи ния устройства путем сокращ ем сок ащения объе уровень. Сигнал с выхода первого бло- иа памяти блоков постоянной памяти, ка 4 является одновреиенно тактовым введен триггер, устан в становочный вход ко импульсом для второго счетчика 3. торого является входом задания вида

Только после подсчета вторым счетчи- развертки, а счетный в д а четный вхо обьединен с ком 3 первых 256 тактовых импульсов в "0" вто ого счет входои установки " " p (четных или нечетных строк) на выхо-i чика и соединен с етв р ч е тыи выходои де старшего разряда формируются КГИ, второго буферного регистра, а выход аэ ешающие считывание содержимого соединен с вторым вх д о ым вхо ои втового бло второго блока 5. Сгенерированный на 4< ка постоянной п мяти, д у р

40 его выходе сигнал обеспечивает дос- ния первого ло и вого блока постоянной памяти туп ко второй области памяти первого соединен со счетны д м вхо ом второго блока 4, т.е. разрешает формирование счетчика, второй выход которого яв временных интервалов полустроки (урав- ляется тр т етьим выходом синхрогенера» нивающих импульсов и врезок). На этом тора, с д у р вхо ом п авления второго бу интервале тактирование второго счет- ферног р р но о егист а и с третьии входои чика 3 происходит с периодом 32 мкс. второго л о ого блока постоянной паияти.

1424136

О 1ZS т2

0 1 у

Г 2

Корректор С.Шекмар

Редактор Т.Парфенова

Заказ 4698/57

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

g F

Составитель Э БоРисов

Техред Л. Олийнык

Тираж бб0 Подписное

ВПИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5