Устройство для деления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть применено в быстродействующих арифметических, устройствах для выполнения операции деления чисел. Целью изобретения является сокращение количества оборудования . Устройство содержит регистры 1, 2 остатка, регистр 3 делителя, сумматор 4 частного, сут матор 7 принудительного округления делителя, узел 8 вычисления обратной величины, блоки 5, 10 умножения, вычитатель 9, элемент НЕ 11, селектор 12, вычитатели 13, 14, коммутатор 15, блок управления . 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 С 06 F 7/52

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCH0MV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 4156897/24-24 ° (22) 05.12.86 (46) 23.09.88; Бюл. У 35 (71) Минский радиотехнический институт (72) А.Г.Батюков и А.А.Шостак (53) 681.325 (088.8) (56) Патент США Ф 3234367, кл. 235- .

156, опублик. 1962. Авторское свидетельство СССР

У 1357947, кл. G 06 Р 7/52, 1986. (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ (57) Изобретение относится к вычисли...Я0„„1425657 А тельной технике и может быть применено в быстродействующих арифметических. устройствах для выполнения операции деления чисел. Целью изобретения является сокращение количества оборудования. Устройство содержит регистры

1, 2 остатка, регистр 3 делителя, сумматор 4 частного, сумматор 7 при" нудительного округления делителя, узел 8 вычисления обратной величины, блоки 5, 10 умножения, вычитатель 9, элемент НЕ 11, селектор 12, вычитате- ли 13 14, коммутатор 15, блок управления. 3 ил.

1425657

Изобретение относится к вычислительной технике и может быть применено в быстродействующих арифметических устройствах для выполнения опера5 ции деления чисел.

Цель изобретения — сокрашечие количества оборудования.

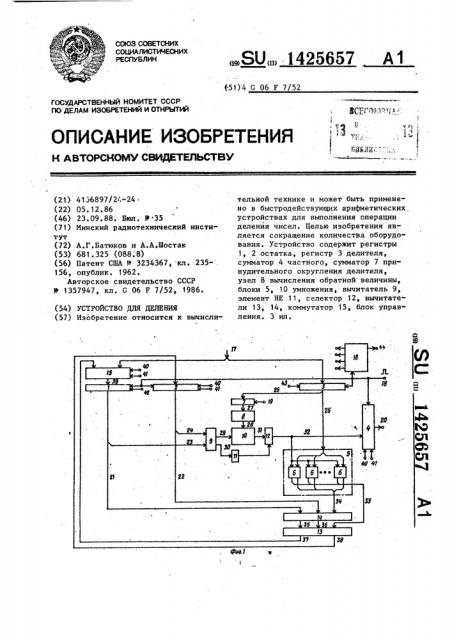

На фиг.1 приведена структурная схема предлагаемого устройства для деления; на фиг.2 — функциональная схема блЬка управления; на фиг.3 микропрограмма работы устройства.

Устройство для деления (фиг.1) содеРжит регистры 1 и 2 остатка, регистр 3 делителя, сумматор 4 частного, блок 5 умножения, состоящий из ! )n/k(k-разрядных умножителей 6 (ив разрядность операндов; k — - число формируемых н одном такте работы устройства цифр частного), сумматор 7 принудительного округления делителя, узел 8 вычисления обратной величины,, вычитатель 9; блок 10 умножения, элемент НЕ 11, селектор 12, вычитатели

13 и 14, коммутатор 15, блок 16 уп; равления, вход 17 данных устройства, ,вход 18 синхронизации устройства,, вход 19 логической единицы устроггст, ва, выход 20 частного устройства, ,выходы 21 регистра 1 остатка, выходы 22 регистра 2 остатка, выходы 23 k+5 старших разрядов регистра 1 остатка, (дна разряда слева от запятой и k+3

, разряда справа от запятой), выходы !, 24 k+5 старших разрядов регистра 2 35 остатка (два разрада слева от запятой и 1+3 раэряца справа от запятой), выходы 25 регистра 3 делителя, выходы ,26 k+3 старших разрядов регистра 3 делителя (все разряды справа от запя- 40 той), выходы 27 сумматора 7 принудительного округления делителя, выходы

28 k+2 разрядов узла 8 нычисления обратной величины (один разряд слева от запятой и k+1 разряд справа от за- 45 пятой), выходы 29 k+4 младших разрядов вычитателя 9 (один разряд слева от запятой и k+3 разряда справа от запятой), выход 30 старшего (старшего от двух расположенных слева от запя- 50 той) разряда вычитателя 9, выходы 31

k разрядов блока 10 умножения (один разряд слева от запятой и k-1 разряц справа от запятой), вьгходы 32 селектора 12, выходы 33 первой группы бло- 55 ка 5 умножения, которые являются ныходами старших разрядов умножителей

6, выходы 34 второй группы блока 5 умножения, которые являются выходами младших разрядов умножителей б, выходы 35 разности вычитателя 14, ныходы 36 заема вычитателя 14, выходы

37 разности вычитателя 13, выходы 38 заема вычитателя 13, выходы 39 коммутатора 15, выходы 40-44 с первого по пятый блока 16 управления соответственно, счетчик 45 блока 16 управления и память 46 микрокоманд блока 16 упранления (фиг.2), Выходы 25 регистра 3 делителя соединены с входами первой группы первого блока 5 умножения, выходы 33 первой группы которого соединены с входами заема вычитателя 13, а выходы о

34 второй группы — с входами заема вычитателя 14, вход 17 данных устройства соединен с информационными входами регистра 3 делителя и с информационными входами первой группы коммутатора 15, информационные входы второй группы которого соединены с выходами 37 разности вычитателя 13, выходы 38 заема которого соединены с информационными входами регистра 2 остатка, выходы 39 коммутатора 15 соединены с информационными входами регистра 1 остатка, выходы 23 старших разрядов которого соединены с входами уменьшаемого вычитателя 9, входы вычитаемого которого соединены с выходами 24 старших разрядов регистра 2 остатка, выходы 29 младших разрядов вычитателя 9 соединены с входами первой группы второго блока

10 умножения, входы второй группы которого соединены с выходами 28 узла

8 вычисления обратной величины, входы которого соединены с выходами 27 сумматора 7 принудительного округления дели, ля, входы которого соединены с выходами 26 старших разрядов регистра 3 делителя, вход переноса сумматора 7 принудительного округления делителя соединен с входом 19 логической единицы устройства, выходы 31 второго блока 10 умножения соединены с информационными входами селектора

12, выходы 32 которого соединены с входами второй группы первого блока

5 умножения и с входами младших разрядов сумматора 4 частного, выходы которого являются выходом 20 частного устройства, выход 30 старшего paзряда вычитателя 9 через элемент НЕ

11 соединен с управляющим входом селектора 12, выхоцы 21 регистра 1

1425657 остатка соединены с входами уменьшаемого вычитателя 14, выходы 22 регистра 2 остатка соединены с входами вычитаемого вычитателя 14, выходы 35 разности вычитателя 14 соединены с

5 входами уменьшаемого вычитателя 13, входы вычитаемого которого соединены с выходами 36 заема вычитателя 14, вход 18 синхронизации устройства соединен с синхровходами регистров

1-3, сумматора 4 частного и блока 16 управления, первый 40 и второй 41 выходы которого соединены соответственно с первым и вторым управляющими входами коммутатора 15, с входами соответственно установки в "0" и разрешения записи регистра 2 остатка и сумматора 4 частного, третий выход

42 блока 16 управления соединен с входом разрешения записи регистра 1 остатка, четвертый выход 43 блока 16 управления соединен с входом разрешения записи регистра 3 делителя, пятый выход 44 блока 16 управления является 25 выходом сигнализации. окончания деления устройства.

Регистр 1 остатка (и+2)-разрядный, из которых два разряда расположены

Ъ слева от запятой и и разрядов — спраЗО ва от запятой. В исходном состоянии в этом регистре хранится без знака и-разрядный двоичный код делимого, все разряды которого расположены справа от запятой. Регистр 2 остатка содержит и+1 разряд, из которых два расположены слева от запятой, а. остальные — справа. В исходном состоянии этот регистр обнуляется. В процессе выполнения операции деления в регистры 1 и 2 в каждом такте работы 40 устройства записывается значение очередного остатка в двухрядном коде (в виде двух чисел), причем если вычитатели 13 и 14 реализованы с использованием одноразрядных двоичных 45 вычитателей, то в регистр 1 записывается значение разности с выходов 37 вычитателя 13, а"в регистр .2 - значение заема с выходов 38 вычитателя 13.

Если же вычитатели 13. и 14 строятся 50 на основе одноразрядных двоичных сум- . маторов и с применением правил обработки информации в обратном или до-полнительном кодах, то в регистр 1 заносится значение суммы двухрядного 55 кода остатка, а в регистр 2 — значение переноса. Регистр 3 делителя п-разрядный, причем все разряды расположены справа от запятой, В исходном состоянии в регистре 3 делителя хранится и-разрядный двоичный код делителя без знака. Все регистры устройства реализованы на основе двухтактных синхронных DV-триггеров, Запись информации в регистры производится по синхроимпульсу при наличии разрешающего потенциала на их V-входах.

Сумматор 4 частного предназначен для хранения частного. Он также участвует в процессе формирования правильного значения частного при выполнении в устройстве операции деления. В первом такте деления сумматор

4 частного обнуляется путем подачи импульса с входа 18 синхронизации устройства на его синхровход и разрешающего потенциала с первого выхода

40 блока 16 управления на вход разрешения установки в "О" сумматора 4 частного. Во всех других тактах работы устройства в сумматоре 4 частного накапливается значение частного.

Для этого к значению частного, сформированному на предыдущих тактах работы устройства и сдвинутому на k-1 разряд влево (в сторону старших разрядов), прибавляется значение k цифр частного, сформированных на выходах

32 селектора 12 в текущем такте. 3апись результата этого суммирования в сумматор 4 частного производится по синхроимнульсу при наличии разрешающего потенциала на его входе разрешения записи, который подключен к второму выходу 41 блока 16 управления. После завершения деления образованное в сумматоре 4 частное поступает на выход 20 частного устройства.

Сумматор 4 частного может быть реализован на основе комбинационного сумматора и регистра.

Блок 5 умножения комбинационного типа и предназначен для умножения значения делителя, поступающего на его входы первой группы с выходов 25 регистра 3 делителя, на значение k цифр частного, поступающих на его входы второй группы с выходов 32 се" лектора 12. На выходах 33 и 34 блока

5 умножения формируется значение произведения в двухрядном коде (в виде двух чисел). Блок 5 умно.-кения реализован с использованием k-разрядных умножителей 6, выходы старших разрядов произведений которых образу"

14 ют выходы 33 первой группы блока 5 умножения, а выходы младших разрядов произведений умножителей 6 являются выходами 34 второй группы блока 5 умножения. Так как на выходах младших разрядов произведений умножителей

6 правильные значения формируются, как правило, раньше, чем на выходах старших разрядов произведений, то работа вычитателя 14 происходит на фоне рабаты блока 5 умножения и не влияет на временной цикл работы устройства.

Блок 5 умножения может быть реализован и другими известными методами и средствами.

С помощью сумматора 7 принудительнога округления делителя, узла 8 вычисления обратной величины, вычитателя 9, второго блока 1О умножения, элемента HE 11 и селектора 12 в устройстве в каждом такте его работы формируется значение k двоичных цифр частного (один разряд слева от запятой и k-1 разряд справа от запятой) с точностью до единицы младшего раэ-(к- ) ряда с весом 2, причем это значение либо является точным, либо меньше истинного значения на единицу младшего разряда. Если делимое и делитель правильные нормализованные двоичные дроби, то для получения k цифр частного с точностью до единицы младшего разряда необходимо, чтобы на входы вычитателя 9 с выходов 23 и 24 регистров 1 и 2 поступало значение k+5 старших разрядов двухрядного кода остатка (два разряда слева от запятой и k+3 разряда справа от запятой), на входы сумматора 7 — значение k+3 старших разрядов делителя (все разряды справа от запятой) с выходов 26 регистра 3, на входы первой группы блока 10 умножения — значение

k+4 младших разрядов.с выходов 29 вычитателя 9 (один разряд слева от запятой, остальные разряды справа ат запятой), а на входы его второй группы - значение k+2 разрядов с выходов

28 узла 8 (один разряд слева от запятой, другие разряды справа от запятой) .

В комбинационном сумматоре 7 осуществляется принудительное округление старших 1+3 разрядов делителя, поступающих на входы сумматора 7 с выходов

26 регистра 3 делителя ° Округление производится путем подачи на вход переноса сумматора 7 с входа 19 устройства значения логической единицы, На

25657 выходах 27 сумматора 7 образуется (k+4)-разрядный результат (один разряд слева от запятой, остальные справа от запятой), С помощью узла 8 определяется значение k+2 старших разрядов обратной величины (один разряд слева, остальные справа от запятой) от результата, сформированного на выходах 27 сумматора 7. Узел 8 — комбинационного типа. Отметим, что возможна совместная реализация сумматора 7 и узла 8 на

ПЗУ по соответствующей таблице истинности °

С помощью вычитателя 9 старшие

k+5 разрядов двухрядного кода остатка приводятся к однорядному коду. На выходах 29 вычитателя 9 образуется эна20 чение k+4 младших разрядов иэ k+5 формируемых в вычитателе 9 разрядов.

Блок 10 умножения комбинационного типа и осуществляет перемножение двух чисел: (k+4)-разрядного, поступающего на входы его первой группы с выходов 29 вычитателя 9, и (k+2)разрядного, подаваемого на входы его второй группы с выходов 28 узла 8, На выходах 31 блока 10 умножения об.разуется k старших разрядов произве30 дения в однорядном коде (один разряд слева от запятой, остальные справа от запятой). Как и блок 5 умножения, блок 10 умножения может быть реализован любым иэ известных способов.

35 Селектор 12 пропускает на свои выходы 32 результат, образованный на выходах 31 блока 10 умножения, если

t на его управляющем входе присутствует потенциал логической единицы (зна40 чение старшего разряда вычитателя 9 равно нулю). В противном случае, т.е ° когда на выходе 30 вычитателя 9 сформирован сигнал логической единицы> на выходах 32 селектора 12 образует45 ся нулевой двоичный кад. Селектор 12 может быть реализован на k двухвходовь:х элементах И, первые входы которых объединены и подключены к управляющему входу селектора.

50 Вычитатели 13 и t4 могут быть построены с использованием одноразрядных двоичных вычитателей. В этом случае на выходах 37 и 38 вычитателя 13 очередной остаток формируется в двух55 рядном коде в виде разности и заема, Вычитатели 13 и 14 могут быть также реализованы на основе одноразрядных двоичных сумматоров с применением, правил обработки информации в обрат-, 1425657

15

45

50 ном или дополнительном кодах. Для этого необходимо только информацию, поступающую на входы вычитателей 13 и 14 с выходов 33 и 34 первого блока

5 умножения, проинвертировать и осуществить прибавление единиц в их младшие разряды (при использовании дополнительного кода) . В этом случае на выходах 37 и 38 вычитателя 13 очередной остаток образуется в двухрядном коде в виде суммы и переноса.

С помощью коммутатора 15 осуществляется передача на информационные входы регистра 1 остатка либо делимого с входа 17 данных устройства, когда на первом выходе 40 блока 16 управления формируется сигнал логической единицы, либо значение разности, образованной на выходах 37 вычитателя 13, когда на втором выходе

41 блока 16 управления формируется сигнал логической единицы. Коммутатор 15 может быть реализован на элементах 2И-2ИЛИ, Блок 16 управления координирует работу узлов и блоков устройства при выполнении в нем операции деления чисел. Он может быть реализован самыми различными методами и средствами, На фиг,2 в качестве примера приведена реализация блока 16 управления на основе счетчика 45 и памяти

46 микрокоманд. Счетчик 45 накапливающего типа и предназначен для естественной адресации микрокоманд.

Вход счета счетчика 45 соединен с входом 18 синхронизации устройства.

В качестве памяти 46 микрокоманд может быть применена быстродействующая постоянная память емкостью (m+2) 5, где m= )(П-1) /(k-1)(.

В самом начале работы счетчик 45 устанавливается в некоторое исходное состояние, например в "0" (на фиг.2 цепь установки четчика 45 в исходное состояние не показана).

Микропрограмма работы устройства представлена на фиг.3.

Устройство для деления работает, следующим образом.

Пусть на вход 17 данных устройства уже поступили и-разрядные двоичные коды делимого Х и делителя Y (здесь предполагается, что делимое и делитель правильные положительные дроби), а счетчик 45 блока 16 управления установлен в исходное нулевое состояние, По содержимому счетчика

45> которое служит адресом обращения к памяти 46 микрокоманд блока 16 управления, из памяти 46 микрокоманд считывается первая микрокоманда, которой соответствуют управляющие сигналы У40, У42 и У 43 (фиг. 3) . В результате этого соответственно на первом 40, третьем 42 и четвертом 43 выходах блока 16 управления устанавливаются уровни логической единицы.

Под действием этих управляющих сигналов коммутатор 15 пропускает на информационные входы регистра 1 остатка делимое Х с входа 17 данных устройства, регистр 1 остатка и регистр 3 делителя подготовлены к приему информации, так как на их.входах разрешения записи присутствуют по, тенциалы логической единицы, а регистр 2 остатка и сумматор 4 частного настроены на обнуление. С приходом первого импуль-а на вход 18 синхронизации устройства производится запись двоичных кодов делимого Х и делителя

Y в регистры соответственно 1 и 3, а также обнуление регистра 2 остатка и сумматора 4 частного и установка счетчика 45 блока 16 управления в состояние "1". С момента окончания действия первого импульса на входе

18 синхронизации устройства заканчивается подготовительный этап н начинается собственно деление, в процессе которого в течение m тактов формируется m (k-1)+1 двоичных цифр частного, Следует отметить, что в некоторых случаях может оказаться целесообразным подготовительный этап организовать двухшаговым, причем на его первом шаге осуществлять запись только делителя Y в регистр 3 делителя, а на втором шаге производить запись делимого в регистр 1 остатка и обнулять регистр 2 остатка и сумматор 4 частного, Этим самым обеспечена меньшая длительность такта работы устройства, так как временная задержка,сумматора 7 принудительного округления делителя и узла 8 вычисления обратной величины не влияет в этом случае на временный цикл работы устройства. В тех же случаях, когда операнды не могут быть загружены в регистр 1 остатка и регистр 3 делителя одновременно (например, при последоватепьной их выборке из памяти), необходимо всегда в первую очередь записывать делитель, а потом уже делимое, !

О (в регистр 1 заносится значение разности, а в регистр 2 — значение заема двухрядного кода остатка), в младшие разряды сумматора 4 частного записывается k двоичных цифр частного (эти цифры являются самыми старшими в конечном результате), а счетчик 45 блока 16 управления устанавливается в состояние "2", Аналогичным образом устройство работает и в других тактах, Отметим только, что в каждом такте старшая двоичная цифра из k очередных цифр частного, образованных на выходах 32 селектора !2 и поступающих на входы

1 младших разрядов сумматора 4 частноro подсуммируется к младшему двоичному разряду содержимого сумматора 4 частного, сдвинутому на 1-1 разряд в сторону его старших разрядов.

После выполнения последнего m+1 такта на выходе 20 частного устройства образуется и-разрядное частное.

Одновременно с этим из памяти 46 микрокоманд блока 16 управления считывается микрокоманда m+2, которой соответствует управляющий сигнал У44, и соответственно на пятом выходе 44 блока 16 управления устанавливается уровень логической единицы, сигнализирующий об окончании операции делеФормула и з о б р е т е н и я

Устройство для деления, содержащее первый и второй регистры остатка, регистр делителя, сумматор частного, сумматор принудительного округления делителя, узел вычисления обратной величины, первый и второй блоки умножения, первый, второй и третий вычитатели, селектор, коммутатор, элемент НЕ и блок управления, причем выходы регистра делителя соединены с входами первой группы первого блока умножения, вход данных устройства соединен с информационными входами регистра делителя и с информационными входами первой группы коммутатора, выходы коммутатора соединены с информационными входами первого регистра остатка, выходы старших разрядов которого соединены с входами уменьшае55 мого первого вычитателя, входы вычитаемого которого соединены с выходами старших разрядов второго регистра остатка, выходы младших разрядов первого вычитателя соединены с входами

1425657

Ь первом такте собственно деления по значению старших разрядов делимого (на следующих тактах в роли делимого выступает остаток, хранящийся в регистрах 1 и 2 в двухрядном коде)

5, :и делителя на выходах 31 второго бло ка 10 умножения формируется М двоичных цифр частного. По значению сигна-! ла на выходе 30 старшего разряда вычи-О

, тателя 9 осуществляется окончательное ,формирование k цифр частного в уст ройстве. Так, если сигнал на выходе !

30 вычитателя 9 соответствует уровню логической единицы, то на выходе эле- 15 мента НЕ 11 формируется сигнал логи, ческого нуля, который устанавливает

,значение k цифр частного на выходах

32 селектора 12, равное нулю. В противном случае в качестве k-разрядного частного в устройстве используется ,;значение k цифр частного, сформиро" ванное на выходах 31 блока 10 умноже ния. Сформированное на выходах 32 ,селектора 12 k-разрядное частное

iZ, (на следующих тактах 2,", где номер такта) поступает на входы младших разрядов сумматора 4 частного и на входы второй группы блока 5 умно,жения, на выходах 33 и 34 которого образуется в двухрядном коде значе-! ,ние произведения Y Zq . С помощью вы читателей 13 и 14 на выходах блока 37 и 38 соответственно разности и заема вычитателя 13 формируется раэ иость Х вЂ” Y Z„ в двухрядном коде, которая в дальнейшем служит остатком подается на информационные входы . которой группы коммутатора 15 и реГистра 2 остатка со сдвигом на 1-1, разряд влево (в сторону старших раз- 40 рядов) . Одновременно с этим из памяти

46 микрокоманд считывается вторая микрокоманда> которой соответствуют управляющие сигналы У41 и У42, и со".

<)тветственно на втором и третьем вы". ходах 4 1 и 42 блока 16 управления устанавливаются уровни логической единицы, Под действием этих управляюи их сигналов коммутатор 15 пропускает на информационные входы регистра 50

1 остатка значение разности, образованной на выходах 37 вычитателя 13, регистры 1 и 2 остатка и сумматор 4 ч.астного подготовлены к приему информации. С приходом второго импульса на вход 18 синхронизации устройства в регистры 1 и 2 остатка записывается сформированный на выходах 37 и 38 иЫчитателя 13 двухрядный код остатка

1425657

Г ! !

Составитель В.Березкин

Редактор Г,Гербер Техред М. Ходанич Корректор N,×åì÷èê

Заказ 4770/46

Тираж 704 Подписное

ВПИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-голиграфическое предприятие, г, Ужгород, ул. Проектная, н я 4 первой группы второго блока умножения, входы второй группы которого соединены с BblxoJI,àìè узла вычисления обратной величины входы которого соУ

5 единены с выходами сумматора принудительного округления делителя, входы которого соединены с выходами старших разрядов регистра делителя, вход переноса сумматора принудительного округления делителя соединен с входом логической единицы устройства, выходы второго блока умножения соединены с информационными входами селектора, выходы которого соединены с входами второй группы первого блока умножения и с входами младших разрядов сумматора частного, выходы которого являются выходом частного устройства, выход старшего разряда первого вычитателя через элемент НЕ соединен с управляющим входом селектора, вход синхронизации устройства соединен с синхровходами первого и второго регистров остатка, регистра делителя, сумматора частного и блока управления, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами коммутатора, с входами соответственно установки в "0 и разрешения записи второго регистра остатка и сумматора частного, третий выход блока управления соединен с входом разрешения записи первого регистра остатка, четвертый выход блока управления соединен с входом разрешения записи регистра делителя, пятый выход блока управления является выходом сигнализации окончания деления устройства, входы уменьшаемого второго вычитателя соединены соответственно с выходам; разности третьего вычитателя, входы уменьшаемого и вычитаемого которого соединены соответственно с выходами разрядов первого и второго регистров остатка, выходы первой группы первого блока умножения соединены соответственно с входами заема второго вычитателя, выходы разности и заема которого соединены соответственно с информационными входами второй группы коммутатора и информационными входами второго регистра остатка, о т л.и— ч а ю щ е е с я тем, что, с целью сокращения количества оборудования, выходы второй группы первого блока умножения подключены к входам заема третьего вычитателя, выходы заема которого подключены к входам вычитаемого второго вычитателя.