Устройство для извлечения квадратного корня из суммы квадратов двух чисел

Иллюстрации

Показать всеРеферат

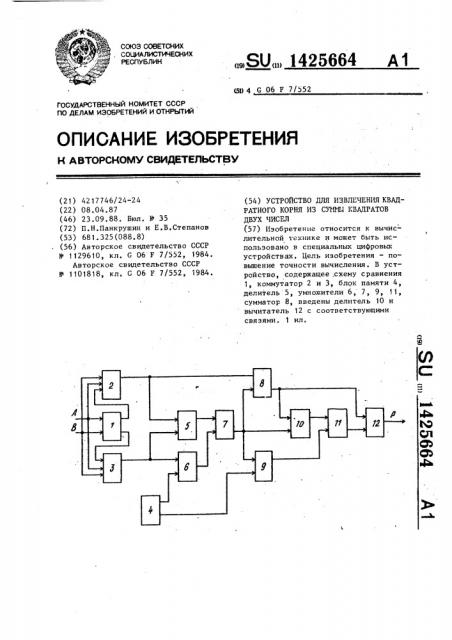

Изобретение относится к вычислительной технике и может быть использовано в специальных цифровых устройствах. Цель изобретения - повьппение точности вычисления. В устройство , содержащее .схему сравнения 1, коммутатор 2 и 3, блок памяти 4, делитель 5, умножители 6, 7, 9, 11, сумматор 8, введены делитель 10 и вычитатель 12 с соответствующими связями. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК сю 4 G 06 Р 7/552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ,Ф СОИДЯТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4217746/24-24 (22) 08.04 ° 87 (46) 23.09.88. Бюл. Р 35 (72) П.Н.Панкрушин и Е.В.Степанов (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 1129610, кл. С 06 F 7/552, 1984.

Авторское свидетельство СССР

Р 1101818, кл. С 06 F 7/552, 1984.

„„SU„„1425664 А1 (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ ИЗ С ЛПЯ1 1:ВАДРАТОВ

ДВУХ ЧИСЕЛ (57) Изобретение относится к вычислительной технике и может быть использовано в специальных цифровых устройствах. Цель изобретения — повьппение точности вычисления. В устройство, содержащее, схему сравнения

1, коммутатор 2 и 3, блок памяти 4, делитель 5, умножители 6, 7, 9, 11, сумматор 8, введены делитель 10 и вычитатель 12 с соответствующими связями. 1 ил.

1425бб4

A2+Â2=1Ai 1+1-) =(А Г+К (1)

25 аппроксимирующей функцией

30 (2) С

У А+С- — --

А+С

Вг уе С = — < .

Коэффициенты, входящие в (2), соответственно равны:

oC = 0,519598;

= 0 501141 °

Устройство работает следующим об- 40 разом.

На вход схемы 1 сравнения и коммутаторов 2 и 3 подаются коды положительных чисел, При этрм выходной сигнал схемы 1 сравнения разрешает прохождение кода большего числа на выход коммутатора 2 и меньшего числа В на выход коммутатора 3, Далее производится параллельное перемножение числа В и коэффициента аС в умнсжителе 6 и деление числа В на А в делителе 5.

В умножителе 7 производится перемножение результатов И/А и В С.

Таким образом, на ныходе умножителя 7 появляется промежуточный ре3 еультат С. Далее производится параллельное перемножение результата С и коэффициента ф .в умножителе 9 и

Изобретение относится к вычислительной технике и может быть использовано в специальных цифровых устройствах.

Целью изобретения является псвьш е 5 ние точности вычисления.

На чертеже представлена блок-схема устройства.

Устройство для извлечения корня из суммы квадратов двух чисел содер жит схему 1 сравнения, коммутаторы

i2 и 3, блок 4 памяти, первый дели;тель 5 первый 6 и второй 7 умножи,тели, сумматор 8, третий умножи:,тель 9, второй делитель 10, четвер1 тый умножитель 11, вычитатель 12.

Работа устройства основана на ис тользовании алгоритма приближенного

2 2

20 вычисления Аг + Вг и заключается в замене функции суммирование результата С и числа А в сумматоре 8. В делителе !0 производится деление результата С на С+А.

В умножителе 11 производится переС множение результатов — — и С P . В выС+А читателе 12 производится вычитание

С2 результата А+С и — — P с выхода коА+С торого считывается результат.

Формула и э о б р е т е н и я

Устройство для извлечения квадратного корня иэ суммы квадратов двух чисел, содержащее схему сравнения, первый и второй коммутаторы, блок памяти, с первого по четвертый умножители, сумматор и первый делитель, причем входы первого и второго сперан дов первого делителя соединены с выходами соответственно первого и второго коммутаторов, управляющие входы которых подключены к первому и второму выходам схемы сравнения, первый вход которой соединен с входом первого числа устройства и с первыми информационными входами первого и второго коммутаторов, вторые информационные входы которых и второй вход схемы сравнения подключен к входу второго числа устройства, выход первого делителя соединен с первым входом второго умножителя, второй вход которого подключен к выходу первого умножителя, первый и второй входы которого соединены с выходом второго коммутатора и первым выходом блока па", мяти, о т л и ч а ю щ е е с я тем, что, с целью повышения точности вычисления, в него введены второй делитель и вычитатель, причем первый вход вычитателя соединен с выходом сумматора и входом первого аргумента второго делителя, вход второго аргумента которого соединен с выходом второго умножителя и первыми входами сумматора и третьего умножителя, вторые входы которых подключены к выходам соответственно второго коммутатора и второму выходу блока памяти, выходы третьего умножителя и второго делителя соединены с первым и вторым входами четвертого умножителя, выход котарогс подключен к второму входу вычитателя, выход которого является выходом устройства.