Устройство для формирования адресов элементов матрицы

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для адресации матриц. Целью изобретения является упрощение устройства. Устройство содержит вход 1 команды, регистры 2,7, дешифратор 3, сумматор 4, вход 5 тактовых импульсов устройства, элемент И 6, блок 9 памяти, выход 10 конца цикла устройства. Использование изобретения позволяет ввести признак транспонирования матриц и уменьшить количество оборудования. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) 1511 4 Г 06 F 9/36, 15/347

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4198557/24-24 (22) 19.02.87 (46) 23.09.88, Бюл. У 35 (72) А.Я,Стальной и В.А.Шуцко (53) 681.,32(088.8) (56) Авторское свидетельство СССР

1126954, кл. G 06 F 9/36, 1984.

Авторское свидетельство СССР

У 1196867, кл. G 06 Р 9/36, 1985. (54) УСТРОЙСТВО ДЛЯ ФОРИИРОВАНИЯ

АДРЕСОВ ЭЛЕМЕНТОВ МАТРИЦЫ (57) Изобретение относится к вычислительной технике и может быть использовано для адресации матриц. Целью изобретения является упрощение устройства. Устройство содержит вход 1 команды, регистры 2,7, дешифратор 3, сумматор 4, вход 5 тактовых импульсов устройства, элемент И 6, блок 9 памяти, выход 10 конца цикла устройства. Использование изобретения позволяет ввести признак транспонирования матриц и уменьшить количество оборудования. 2 ил.

1425667

Изобретение относится к вычислительной технике, в частности к уст" ройствам выполняющим адресацию.

Целью изобретения является упро5 щение устройства.

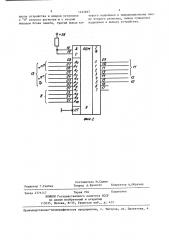

На фиг.1 приведена функциональная схема устройства, на фиг.2 — один из вариантов ПЗУ для матрицы m=3, п=3.

Устройство содержит вход 1 кода команды, первый регистр 2, дешифратор 3, сумматор 4, вход 5 тактовых импульсов, элемент И 6, второй ре гистр 7, первый вход 8 блока 9 па1 мяти, выход 10 признака конца цикла.

Устройство работает следующим образомм.

Исходное состояние устройства устанавливается каждый раз после окон:чания цикла автоматически. В исход- gp ,ном состоянии регистры 2 и 7 установ лены в нулевое состояние, с выхода 12 блока 9 на второй вход элемента И 6 поступает сигнал разрешения. На шину зходных данных поступает код команды, 25 содержащий m — количество строк матрицы, п — количество линейно расположенных элементов в строке, Тр признак транспонирования, А — базовый адрес (фиг.2). На вход 5 поступают актовые импульсы. Дешифратор 3 принимает код команды и выдает сигнал .разрешения на третий вход элемента

Я 6. По приходу тактового импульса а первый вход элемента И 6 вырабатывается сигнал записи в регистр 2.

О выхода регистра 2 информация m,n и Тр поступает на вход 13 блока 9, на первый вход 8 блока 9 поступает нулевая инфоРмация с выхода Регист- 40 ра 7. На выходе 11 блока 9 формируется первый адрес а1 элемента матрицы. IIo тактовому импульсу а1 записывается во второй регистр 7. С выхода второго регистра 7 а1 поступает íà 45 первый вход 8 блока 9 и на первый вход сумматора 4. На выходе сумматора 4 формируется адрес первого эле. мента матрицы: А + а1. По следующему тактовому импульсу аналогично формируется адрес второго элемента матрицы А + а2 и т.д.

После окончания формирования всех адресов матрицы количество адресов равно произведению m х п, с первого выхода 10 блока 9 вырабатывается

55 сигнал конца цикла, устанавливающий регистры 2 и 7 в нулевое состояние, а по следующему тактовому импульсу 5 схема приходит в исходное состояние и на выходе 12 блока 9 формируется сигнал, разрешающий прием следующей команды. Количество тактовых импульсов для формирования адресов массива и приведения схемы в исходное состояние равно (m х п) + 2.

Рассмотрим два варианта формирования адресов массива матрицы ш=З, п=З, А=10, имеющей вид

1 2 3

4 5 6

7 8 9

1, Матрица не транспорнированная

ТР=О, на выходе 11ÏÇÓ9 сформированы адреса элементов матрицы: a1=1, а2=2, a3=3, а4=4, a5=5, а6=6, а7=7, а8=8, а9=9.

На выходе 14 устройства формируются адреса массива матрицы: А1=11, А2=12, A3=13, А4=14, A5=15, A6=16, А7=17, А8=18, А9=19.

2. Матрица транспонирования Тр=1, на выходе 11 блока 9 сформированы адреса элементов матрицы: а1=1, а2=4, a3=7, а4=2, а5=5, а6=8, а7=3, a8=6, а9=9.

На выходе 14 устройства формируются адреса массива матрицы: А1=11, А2=14, A3=17, А4=12, A5=15, А6=18, А7=13, А8=16, А9=19.

Формула и з обретения

Устройство для формирования адресов элементов матрицы, содержащее два регистра, сумматор, элемент И и дешифратор, причем вход команды устройства подключен к входу дешифратора, информационному входу первого регистра и входу первого слагаемого сумматора, о т л и ч а ю щ е е с я тем, что, с целью упрощения, оно содержит блок памяти, причем первый вход элемента И подключен к входу записи второго регистра и входу тактовых импульсов устройства, выход второго регистра подключен к входу второго слагаемого сумматора и к старшим разрядам адресного входа блока памяти, младшие разряды адресного входа и первый выход которого подключены соответственно к выходу первого регистра и второму входу элемента И, третий вход и выход которого подключены соответственно к выходу дешифратора и входу записи первого регистра, вход установки н "0" которого соединен с выходом признака конца з

1425667 цикла устройства и входом установки торого подключен к информационному вхов "0" второго регистра и с вторыщ ду второго регистра, выход сумматора выходом блока памяти, третий выход ко- подключен к выходу устройства.

Составитель М.Силин

Техред А.Кравчук

Редактор Г.Гербер

Корректор А.Обручар

Подписное

Заказ 4771/47 Тираж 704

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д,. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4