Устройство для отладки программ

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике-и может быть использовано при отладке программ микропроцессорных систем. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения отладки программ в реальных условиях. Устройство содержит блок 1 управления , регистры 2 и 11 данных, блоки 3 и 8 индикатдии данных, регистр 4 адреса, блок 5 индикации адреса, блоки 6 и 10 сравнениясоответственно адресов и данных, регистр 12 адреса останова, дешифратор 13 старших разрядов адреса, элементы И-НЕ 14-17. Устройство обеспечивает различные режимы обмена информацией между блоками устройства и между устройством и отлаживаемой микропроцессорной системой, дополнительные возможности запоминания и индикации информации адресации к отладочной памяти. 1 з.п. ф-лы, 1 нл. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

42 68 А1 (19) (11) (я) 4 G 06 F 11/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

И 1Л"" 1Р

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4230684/24-24 (22) 26. 02.87 (46) 23.09.88. Бюл. М - 35 (72) В.С.Дунаев (53) 681.3 (088.8) (56) Патент СНА 11 4231087, кл. G 06 F 11/00, 1980.

Патент ГДР У 159914, кл. G 06 F 11/28, 1981. (54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ (57) Изобретение относится к .автоматике и вычислительной технике и может быть использовано при отладке программ микропроцессорных систем.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения отладки программ в реальных условиях.

Устройство содержит блок 1 управления, регистры 2 и 11 данных, блоки

3 и 8 индикации данных, регистр 4 адреса, блок 5 индикации адреса, блоки 6 и 10 сравнения соответственно адресов и данных, регистр 12 адреса-останова, дешифратор 13 старших разрядов адреса, элементы И-НЕ

14-17. Устройство обеспечивает различные режимы обмена информацией между блоками устройства и между устройством и отлаживаемой микропроцессорной системой, дополнительные возможности запоминания и индикации информации адресации к отла- а дочной памяти. 1 з.п. ф-лы, 1 ил.

1425687

Изобретение относится к вычислительной технике и может, быть использовано для отладки программных и аппаратных средств и тестирования микропроцессорных систем (МПС).

Целью изобретения является расигирение функциональных возможностей устройства за счет отладки программ в реальных условиях.

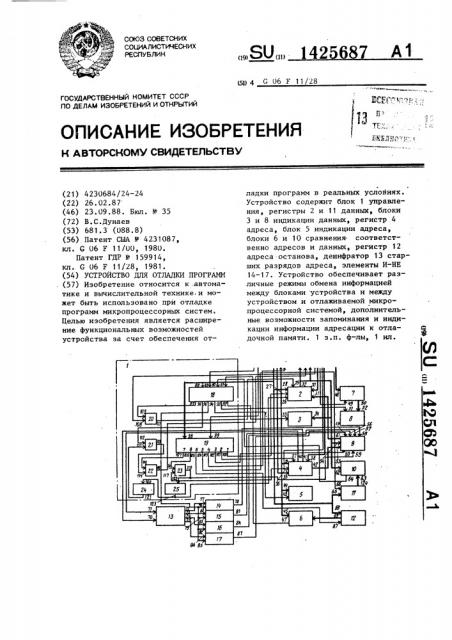

На чертеже изображена структурная схема устройства для отладки программ. Схема содержит блок 1 управления, первый регистр 2 данных, первый блок 3 индикации данных, регистр 4 адреса, блок 5 индикации адреса, блок 6 сравнения адресов, регистр 7 данных, второй блок 8 индикации данных, блок 9 отладочной памяти, блок

10 сравнения данных, второй регистр

11 данных, регистр 12 адреса остано: ва, дешифратор 13 ста >ших разрядов адреса, элементы И-HE 14-17, регистр

18 режимов,, дешифратор 19 команд, :блока управления, элементы И 20 и

: 21, элементы ИЛИ 22 и 23, блоки 24 и 25 задержки.

Кроме того, на чертеже показаны входы-выходы 26-124.

Устройство работает следующим образом.

При записи информации в блок 9 отладочной памяти в регистр 2 дан",ных и регистр 4 адреса предварительно заносятся данные и адрес, причем на первый вход данных регистра 2

:данных от устройства ввода пос.тупают данные по сигналу, приходящему на

,вход записи регистра 2 данных, а ,на первый адресный вход регистра. 4 адреса поступает адрес от устройства ввода по сигналу на вход записи регистра 4 адреса с выхода дешифратора 19 команд. Управляющие сигналы вырабатываются блоком 1 управления при поступлении от устройства ввода информации на вход данных и признака команды на входах дешифратора 19 команд. С выходов1регистра 2 данных на информациойный вход блока 9 отладочной памяти поступает код и записывается по сигналу, поступающему на вход записи блока 9 отладочной памяти, по адресу, поступившему на адресный -вход блока 9 с выхода регистра 4 адреса. Обращение с целью записи или чтения производится к 8разрядной ячейке блока 9, если на входы элементов И-НЕ соответственно

14-17 поступает сигнал уровня логической единицы. В этом случае при поступлении с одного иэ выходов дешифратора 13 старших разрядов сигнала уровня логической нуля на вход одного из элементов И-HE 14, 15. l6 и 17, на выходе соответствующего элемента появится сигнал логической единицы. Обращение производится к

24-разрядной ячейке памяти. Если на входы элементов И-НЕ 14-17 поступают нулевые потенциалы, при чтении из блока 9 по команде, поступающей от устройства ввода, запись адреса в регистр 4 адреса производится таким же образом, как и при записи в блок

9 отладочной памяти. Считывание из блока 9 отладочной памяти производится по сигналу, поступившему на вход чтения с выхода элемента ИЛИ 23.

Сигнал на выходе элемента KHH 23 появляется при поступлении сигнала на его вход с выхода дешифратора 19 команд.

Информация с выхода блока 9 отладочной памяти гоступает на информационный вход регистра 2 данных и заносится в него по сигналу, поступившему на его вход записи с выхода блока 2 задержки. Блок 2 задержки служит для задержки на время чтения из блока 9 отладочной памяти, поэтому сигнал записи в регистр 2 данных поступает на его вход записи после того, как данные в блоке 9 отладочной памяти появляются на выходе. Информация с выхода регистра.

2 данных поступает для индикации на вход данных блока 3 индикации данных. Сигнал, поступающий на управляющий вход этого блока индикации, запрещает или разрешает индикацию в зависимости от его уровня.

При каждом обмене информацией между блоками устройства для отладки программ с отлаживаемой микропроцессорной системы ЙПС с устройством ввода-вывода в регистр 18 режимов предварительно загружается код, который интерпретируется блоком 1 управления и определяет направление и режим обмена. Код поступает на информационный вход регистра 18 режимов от устройства ввода.-вывода по сигналу, поступающему на вход записи регистра режимов 18 от устройства ввода-вывода. Данные из блока 9 отладочной памяти могут быть переда1425687 ны через регистр 2 данных к устройству ввода-вывода и от него, например, в ЭВМ с целью их анализа и контроля, Адрес с выхода регистра 4 адреса также может быть передан через устройство ввода-вывода во внешнюю среду. Кроме того, адрес может индицироваться в блоке 5 индикации.

Возможны различные режимы отлад- 1п кн, В режиме непрерывного выполнения программы КПС по сигналу, поступающему от NHC на вход записи регистра 4 адреса, на его информационный вход поступает адрес, а с era выхода поступает на адресный вход блока 9 отладочной памяти. Управляющий сигнал от МПС поступает на вход элемента ИЛИ 23, с выхода которого сигнал чтения поступает на вход бло- 2О ка 9 отладочной памяти. После задержки на время чтения, осуществляемой блоком 25 задержки, данные по сигналу, поступающему с выхода блока 25 задержки, заносятся в регистр 2 дан- 2б ных. Блок 24 задержки осуществляет временную задержку выдачи сигнала готовности данных на время записи данных в регистр 2 данных. С выхода регистра 2 данных данные передаются к KIC по управляющему сигналу, поступающему к liIC с выхода элемента

РЛИ 22. Если эти данные являются командой, то она выполняется процессором KIC. Управляющий сигнал

35 с выхода элемента ИПИ 22 вырабатывается с учетом состояния регистра

18 режимов. При положительном уровне сигнала, поступающего на вход элемента И 21, на второй вход этого 1О элемента поступает также сигнал положительного уровня с выхода блока

24 задержки. При этом с выхода элемента И 21 поступает сигнал на вход элемента ИЛИ 22. В шаговом режиме отладки на вход элемента И 21 с выхода регистра 18 режимов поступает сигнал низкого уровня, который запрещает прохождение сигнала с выхода элемента И 21 на вход элемента ИЛИ 22.

Управляющий сигнал на выходе элемента ИЛИ 22 формируется при поступлении сигнала с выхода дешифратора 19 команд на вход элемента.ИЛИ 22. Сигнал на выходе дешифратора 19 команд формируется при поступлении на его вход соответствующего кода от устройства ввода-вывода по сигналу, поступающему на вход признака команды цешифратора 19 команд от устройства ввода-вывода. Таким образом, управление шаговым режимом отладки осуществляется оператором с помощью устройства ввода информации.

При непрерывном выполнении программы IIIIC устройством анализируются адреса выполняемых команд и информации, являющаяся командой или операндом, или содержимым регистра состояния. Эта информация сравнивается в блоках 6 и 10 соответственно с содержимым регистра 12 адреса останова и регистра 11 данных. При совпадении с выходов блоков 6 или 10 на входы регистра 18 режимов поступают сигналы, которые переводят устройство в режим отладки по шагам. Информация в регистры 11, 12 заносится с их информационных входов от устройства ввода-вывода при поступлении на их входы записи управляющих сигналов.

При выполнении программы KIC промежуточные результаты вычислений, нужные для контроля правильности выполнения программы .ИПС, могут быть занесены в регистр 7 данных от ИПС (по сигналу записи), содержимое которого поступает на блок 8 индикации. Индикация может быть разрешена или запрещена по сигналу, поступающему на вход блока 8.

Формула изобретения

1.устройство для отладки программ, содержащее блок управления, первый регистр данных, регистр адреса, блок индикации адреса, блок сравнения адресов, блок отладочной памяти, регистр адреса останова и первый блок индикации данных, причем первый информационный вход устройства соединен с первым информационным входом первого региСтра данных и информационным входом регистра адреса останова, второй информационный вход устройства соединен с вторым информационным входом регистра данных, информационный выход блока отладочной памяти соединен с третьим информационным входом первого регистра данных, выход которого соединен с информационным входом первого блока индикации, с первым информационным входом блока отладочной. памяти, с первым входом блока сравнения данных

1425687 и является первым информационньм выходом устройства, первый адресный вход устройства соединен с первым информационным входом регистра адреса, второй адресный вход устройства соединен с вторым информационным входом регистра адреса, первый вход признака адреса устройства соединен с входом записи регистра адреса, первый выход которого соединен с информационным входом блока индикации адреса, с первым входом блока сравнения адресов и является адресным выходом устройства, второй информационный выход регистра адреса соединен с адресным входом блока отладочной памяти, выход регистра адреса останова соединен с вторым входом блока сравнения адресов, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения отладки программ в реальных условиях, в устройство введены второй регистр данных, второй блок индикации данных, блок сравнения данных, буферный регистр," дешифратор старших разрядов адреса, четыре элемента И-НЕ, причем выходы старших разрядов регистра адреса соединены с входами дешифратора старших разрядов, адреса, первый, второй, третий и четвертый выходы которого соединены с первыми входами соответственно первого, второго, третьего и четвертого элементов

И-НЕ, выходы которых соединены соответственно с первым, вторым, третьим и четвертым входами обращения блока отладочной памяти, первый,. второй, третий, четвертый, пятьй, шестой, седьмой, восьмой, девятый, десятый, ;одиннадцатый, двенадцатый и тринад- ) . цатый выходы блока управления соеди нены .соответственно с первым входом записи первого регистра данных, с первым входом записи регистра адреса, с входом записи блока отладочной ! памяти, с выходом признака записи устройства, с входом признака записи второго регистра данных, с входом признака записи регистра адреса останова, с входом чтения блока отладочной памяти, с вторым входом записи первого регистра данных, с входом разрешения индикации первого блока индикации данных, с входом разрешения индикации второго блока

55 индикация данных, с входом разрешения индикации блока индикации адреса, с третьим входом записи первого регистра данных и вторым выходом записи устройства, выход опроса обращения блока управления соединен с вторыми входами первого, второго, третьего и четвертого элементов

И-НЕ, первый информационный вход устройства соединен с информационным входом блока управления и информационным входом второго регистра данных, выходы равенства блоков сравнения адресов и данных соединены соответственно с первым и вторым режимными входами блока управления, вход признака ре>яма устройства соединен с входом записи режима блока управления, вход обращения устройства соединен с первым входом блока управления, вход признака данных устройства соединен с входом записи буферного регистра, третий информационный вход устройства соединен с информационным входом буферного регистра,. выход которого соединен с информационным входом второго блока индикации, второй вход признака адреса ссединен с вторым входом записи регистра адреса и первым входом блока управления, вход признака команды устройства соединен с входом опроса дешифратора команд.

2. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что блок управления содержит регистр режимов, первый и второй элементы И. первый и второй элементы ИЛИ, первый и второй блоки задержки и дешифратор команд, причем первый и второй режимные входы блока управления соединены с соответствующими установочными входами регистра режимов, вход признака записи реяима соединен с входом записи регистра режимов первыи второй, третий, четвертый, пятый, шестой, седьмой и восьмой выходы дешифратора команд соединен с первым, вторым, т ретьим, четвертым, пятым . и шестым выходами блока управления, с первыми входами первого и второго элемента .UIH, выход которого является седьмыч выходом блока и через первый элемент задержки соединен с восьмым выходом блока и с входом второго элемента задержки, первый, второй, третий, четвертый, пятый и шестой информационные выходы регист.

Составитель В.Сигалов

Техред M.Õîäàíè÷ Корректор С.Шекмар

Редактор H.Ãóíüêî

Заказ 4772/48

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

7 1425687 8 ра режимов являются соответственно элемента ИЛИ и первого элемента И, девятым, десятым, одиннадцатым вы- выход первого элемента И является ходами блока управления и соединены двенадцатым выходом блока, выход с выходом опроса обращения блока

5 второго элемента задержки соединен управления, с первыми входами соот- с вторым входом второго элемента И, ветственно первого и второго эле- выход которого соединен с вторым ментов И, первый и второй входы входом первого элемента И, выход блока управления соединены с вторы- которого является тринадцатым выми входами соответственно второго 10 ходом блока.