Двухканальное устройство для сопряжения двух электронно- вычислительных машин

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для буферизации сообщений при обмене массивами информации между двумя электронно-вычислительными машинами. Цель изобретения - уменьшение затрат машинного времени при обмене информацией за счет исключения периодического обращения к буферной памяти устройства. Устройство 1 для сопряжения содержит блок 2 памяти, вторую 3 и первую 4 группы элементов ИЛИ, первый 5 и второй 6 элементы ИЛИ, первый 7-и второй 8 каналы, каждым из которых содержит вторую 9 и первую 10 группы элементов И, информационный вход-выход 11 устройства, первый элемент И 12, элемент ИЛИ 13, второй элемент И 14, вход 15 считывания устройства, вход 16 записи устройства, регистр 17 адреса, дешифратор 18 поля .адресов памяти, триггер 19, тактовый вход 20 устройства, элемент И-НЕ 21, элемент НЕ 22, третью группу элементов И 23; элемент 24 задержки, управляющий выход 25, вычитающий счетчик 26, дешифратор адреса счетчика 27, третий элемент И 28, дополнительный 29 триггер, выход 30 запроса прерывания и вход 31 разрешения прерьюания. Первая 32 и вторая 33 ЭВМ соединены соответственно с каналами 7 и 8. 1 ил. с сл с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИ Х

РЕСПУБЛИК (si} q G 06 F 13/00, 15/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ, (61) 1180906 (21) 4206428/24-24 (22) 03.03.87 (46) 23.09.88. Вюл. У 35 (72) Р.В.Рабешко, М.В.Купчак и О.В.Коблик (53) 681.325 (088.8) (56) Авторское свидетельство СССР

Р 1180906, кл. G 06 F 13/00, 1985, (54) ДВУХКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ

СОПРЯ>КЕНИЯ ДВУХ ЭЛЕКТРОННО-ВЪ|ЧИСЛИТЕЛЬНЪК МАНИН (57) Изобретение относится к вычислительной технике и может быть использовано для буферизации сообщений при обмене массивами информации между двумя электронно-вычислительными машинами. Цель изобретения уменьшение затрат машинного времени при обмене информацией за счет исключения периодического обращения к буферной памяти устройства. Устройство 1 для сопряжения содержит блок

ЛВ 1425692 А 2

2 памяти, вторую 3 и первую 4 группы элементов ИЛИ, первый 5 и второй

6 элементы ИЛИ, первый 7 и второй

8 каналы, каждый из которых содержит вторую 9 и первую 10 группы элементов И, информационный вход-выход

11 устройства, первый элемент И 12, элемент ИЛИ 13, второй элемент И 14, вход 15 считывания устройства, вход

16 записи устройства, регистр 17 адреса, дешифратор 18 поля адресов памяти, триггер 19, тактовый вход

20 устройства, элемент И-НЕ 21, элемент HE 22, третью группу элементов

И 23; элемент 24 задержки, управляющий выход 25, вычитающий счетчик

26, дешифратор адреса счетчика 27, третий элемент И 28, дополнительный

29 триггер, выход 30 запроса прерывания и вход 31 разрешения прерывания. Первая 32 и вторая 33 ЭВМ соединены соответственно с каналами 7 и 8. 1 ил.

1425692

Изобретете относится к вычислительной технике, может быть использовано дял буферизации сообщений при обмене массивами информации между двумя электронно-вычислительными машинами (3BM) и является усовер" шенствованием Известного устройства, описанного в явт.св. Р 1180906.

Цель изобретения — уменьшение 1Î затрат машинного времени при обмене информацией за счет исключения периодического обращения к буферной памяти устройства.

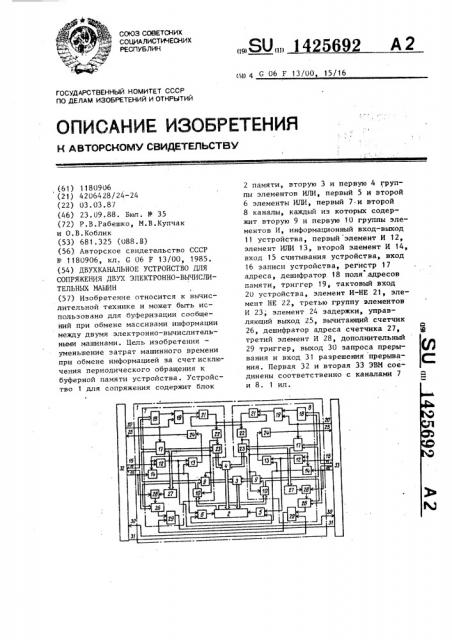

Ня чертеже представлена струкI турная схема устройства.

Устройство 1 для сопряжения со, держит блок 2 памяти, вторую 3 и первую 4 группы элементог И1П1, .первый 5 и второй 6 элементы ИЛИ, пер- 20 вый 7 и второй 8 каналы, каждый из которых содержит. вторую 9 и первую

10 группы элементов И, информационный вход-выход 11 устройства, пер-!

l âûé элемент И 12, элемент ИЛИ 13, 25 второй элемент И 14, вход 15 счить:— вания устройства, вход 16 записи устройства, регистр 17 адреса, де шифратор 18 поля адресов памяти, триггер 19, тактовый вход 20 уст .ройства, элемент И-HE 21, элемент

НЕ 22, третью группу элемечтов И 23, элемент 24 задержки, управляющий выход 25,вычитающий счетчик 26, де шифратор адреса счетчика 27, третий

35 элемент И 28, дополнительный триггер 29, выход 30 запроса прерывания и вход 31 разрешения прерывания.

Первая 32 и вторая ЗЗ ЭВИ соецинены соответственно с каналами 7 и 8, Счетчик 26 представляет собой вычитающий двоичный счетчик с количеством триггеров, определяемым как двоичный логарифм от объема максимального передаваемого массива, и с упрявпяющим выходом признака нулевого состояния, активный уровень сигнала на котором вырабатывается при нулевом состоянии всех триггеров счетчика 26.

Дешифратор адреса счетчика 2? представляет собой схему, активный уровень сигнала на выходе которой вырабатывается при наличии ня ее входе адреса счетчика 26,, и может

55 быть построен как схема совпадения... на одну группу входов которой поступает информация с регистра 17 ядреса, а на другой группе входов перемычками установлен ацрес счетчика.

Сигнал "Разрешения прерывания" вырабатывается ЭВИ, поступает на вход 31 устройства и информирует устройство, что ЭВИ приняла запрос на прерывание от устройства 1 для сопряжения.

СигHBÇI запроса прерывания ходе 30 информирует одну ЗВИ, что другая ЭВИ записала в блок, 2 памяти массив информации.

Описание других устройств и остальные особенности устройства приведены в описании известного изобре тения.

Устройство работает счедующим образом.

Пусть ЭВИ 32 подготовила массив информации и начинает запись в блок

2 памяти. Перед записью массива ЭВИ

32 устанавливает на информационных входах-выходах 11 адрес счетчика 26 канала 7. Тяк как на входе детифрятора адреса счетчика 27 находится адрес счетчика, на его выходе имеется активный уровень напряжения.

ЭВИ 32 помещает HB информационные входы-выходы 11 данные, которые ог.— ределяют число ов в массиве, и вырабатывает на входе 16 активный сигнал "Вывод", На. выходе элемента

И 28 формируется активный уровень, который записывает данные в вычитаю1щ1й счетчик 26.

После этого начинается запись слов массива в блок Z памяти. Запись каждого слова массива происходит следуюшим образом.

ЗВИ 32 в адресной части цикла

"Вывод" передает на входы-выходы 11 адрес ячейки блока 2 памяти, в которую необходимо записать информа-" цию. На входе 20 при этом присутствует высокий потенциал i". который поступает на тактовые входы регистра 17 и триггера 19 канала 7. В регистр 17 производится -апись адреса.

Дешифратор 18 дешифрует адрес и в случае принадлежности его адресному полю блока 2 памяти вырабатывает сигнал ня информационный вход первого триггера 19, .который устанавливает первый триггер 19 в

Сигнал с выхода гервого триггера 19 поступает на первый вход элемента, И-НЕ 21, на втором входе которого присутствует высокий потенциал 1

3 14256 с выхода элемента И-НЕ 21 канала 8, и вызывает на его выходе появление сигнала логического "0". На выходе элемента НЕ 22 появляется разрешаю!

1 13

5 щий сигнал 1", который поступает на вторые входы элементов 9,10 12 и 14. После адресной части цикла

ЭВМ 32 помещает на входы-выходы 11 данные, которые необходимо записать в блок 2 памяти, после чего на входе 16 устанавливается сигнал Вывод".

Так как на втором входе элемента

И 14 присутствует сигнал "1", то сигнал "Вывод" через элемент ИЛИ 6 поступает на управляющий вход блока

2 "Запись".

При этом на адресных и информационных входах блока 2 присутствуют соответственно адрес с выхода элементов И 23 через элементы ИЛИ 4 и данные с выхода элементов И 9 через элементы ИЛИ 3, следовательно, происходит операция записи выданных

ЭВМ 32 данных по необходимому адре- 25 су.

Одновременно сигнал "Вывод" поступает на счетный вход счетчика 26, уменьшая его содержимое на единицу.

Сигнал "Вывод" также поступает 30 через элементы ИЛИ 13 на элемент 24 задержки, с выхода которого через время а поступает по выходу 25 в

ЭВМ 32 в результате чего сигнал

"Вывод" устанавливается в "0" сни35 маются данные с входов-выходов 11 и устанавливается высокий уровень

"1" на входе 20.

После записи последнего слова массива в блок 2 памяти содержимое вычитающего счетчика 26 становится равньи нулю и на его выходе признака нулевого состояния появляется управляющий сигнал, который фронтом импульса перебрасывает триггер 29 в состояние логической "1". Сигнал с выхода триггера 29 поступает на выход 30 запроса прерывания в ЭВМ

33, сообщая ей, что массив записан в блок 2 памяти. ЭВМ 33, приняв запрос на прерывание, вьщает сигнал разрешения прерывания, который поступает на вход 31, сбрасывая триггер 29.

После этого ЭВМ 33 начинает считывать содержимое блока 2 памяти.

Операция "Ввод" аналогична операции Вь|вод" за исключением того, что управляющий сигнал поступает на вход

92 4

15 и через элемент И 12 поступает на вход элемента ИЛИ 5 и с его выхода на управляющий вход. блока 2 памяти "Считывание". Содержимое ячейки памяти, адрес которой указан на адресных линиях блока 2 памяти, через элемент И 10 передается на информационный вход-выход 11 устройства.

Время считывания массива из блока 2 памяти известно и равно времени считывания одного слова, умноженному на количество слов. Время считывания одного слова из памяти равно

1 времени записи в блок 2 памяти и определяется временем задержки элемента 24 задержки. Осуществив необходимую задержку, ЭВМ 32 может снова записывать данные в блок 2 памяти.

Так как ЭВМ 32 и 33 работают независимо, то они могут одновременно записывать или считывать данные с разных ячеек блока 2 памяти, Если ЭВМ 33 поместит адрес одной из ячеек блока 2 памяти после того, как он был выдан ЭВМ 32, то сигнал логического "0" с выхода элемента

И-НЕ 21 канала 7 запретит установку на выходе элемента И вЂ” НЕ 21 канала

8 сигнала логического "0" и на выходе элемента НЕ 22 канала 8 не будет разрешающего потенциала. Поэтому адрес регистра 17 канала 8, данные

1 и сигнал "Вывод" не дойдут на вход блока 2 памяти до того времени, пока ЭВМ 32 обращается к памяти.

В случае одновременного обращения

ЭВМ 32 и 33 к устройству 1 для сопряжения, т.е. одновременного помещения адреса на входы-выходы 11, происходит установление триггеров

19 в "1", запоминание адресов в регистрах 17 и присутствие сигналов

"Ввод" или "Вывод" на одном из входов соответственно 15 или 16 каналов 7 и 8.

Так как элементы И-НЕ 21 с их взаимными связями представляют собой триггер. то одновременное поступление на их первые входы сигналов "1" с триггеров 19 приводит к неопределенному (непредсказуемому состоянию выходов элементов И-НЕ 21.

Однако это состояния будет одним из двух: на выходах элемента И вЂ” НЕ канала 8 "1" или наоборот. Таким образом, работа устройства 1 для сопряжения в дальнейшем происходит

1425

Составитель Е.Устинов

Техред M.Õoäàíè÷

Корректор В.Бутяга

Редактор Е.Папп

Заказ 4772/48

Тираж 704 Подпис ное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4 аналогично работе, описанной дл т режима последовательного обращения

ЭВМ к устройству для сопряжения.

Формула и з о б р е т е н и я

Двухканальное устройство для сопряжения двух электронно-вычислительных машин по ав г.св. У 1180906, о тл и ч.а ю щ е е с я тем, что, с целью уменьшения затрат машинного времени при обмене информацией за счет исключения периодического обрашения к буферной памяти устройства, в каждый канал устройства введены .вычитающий счетчик, дешифратор адреса счетчика, третий элемент И и дополнительный триггер, причем информационный вход вычитающего счетчика соединен с информационным входом692 б выходом устройства, вход разрешения записи информации вычитающего счетчика соединен с выходом третьего элемента И, первый и второй входы которого соединены с входом записи устройства и с выходом дешифратора адреса счетчика соответственно, вход дешифратора адреса счетчика соединен с выходом регистра адреса, выход признака нулевого состояния вычитающего счетчика соединен с входом установки дополнительного триггера, выход которого является выходом запроса прерывания другого канала, вход сброса дополнительного триггера является входом разрешения прерывания другого канала.