Ассоциативная ячейка памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ пятого пбколения для создания без данных в ассоциативных накопителях. Цель изобретения - расширение функциональных возможностей ассоциативной запоминающей ячейки за счет увеличения числа реализуемых им конических функций. Поставленная цель достигается тем, что запоминающий элемент содержит второй I1, третий 6, четвертый 2 и пятый 3 элементы И, второй 8 и третий 4 триггеры, инвертор 5, элемент И-ШТИ 1, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10 с соответствующими связями. Введение в ассоциативный запоминающий элемент указанных блоков, позволяет ему реализовать четыре конические функции, необгходимые для организации структуры данных в накопителе, обеспечивающей динамическую перестройку ассоциативных связей по совокупности свойств об ьектов между элементами хранимой информации. 3 ил. с: S (Л с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

1б11 4 0 11 С 15/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4230702/24-24 (22) 04.03.87 (46) 23.09.88. Бюл. 1в 35 (.71) Институт кибернетики им. В,М.Глушкова (72) В.А.Ященко и С.O.Чепига (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР

У 1045272, кл. G 11 С 15/00, 1983.

Кохонен Т, Ассоциативные запоминающие устройства. — М.: Мир, 1982, с. 93. (54) АССОЦИАТИВНАЯ ЯЧЕЙКА ПАМЯТИ (57) Изобретение относится к вычисли- тельной технике и может быть использовано в ЭВМ .пятого поколения для создания без данных в ассоциативных накопителях. Цель изобретения — расширение функциональных возможностей

ÄÄSUÄÄ 1425783 А1 ассоциативной запоминающей ячейки за счет увеличения числа реализуемых им конических функций, Поставленная цель достигается тем, что зайоминающий элемент содержит второй 11, третий б, четвертый 2 и пятый 3 элементы И, второй 8 и третий 4 триггеры, инвертор 5, элемент И-1ШИ 1, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10 с соответствующими связями. Введение в ассоциативный запоминающий элемент указанных блоков позволяет ему реализовать четыре конические функций, необ-. ходимые для организации структуры данных в накопителе, обеспечивающей динамическую перестройку ассоциатив- с ных связей по совокупности свойств

Ф объектов между элементами хранимой информации. 3 ил.

1425783

И зобретение относится к вычислительной технике и может быть использовано в ЭВМ пятого поколения для создания баз данных в ассоциативных накопителях.

Цель изобретения — расширение

1 ункциональных возможностей ассоциативной ячейки памяти за счет увеличеИия реализуемых логических функций. 1Q

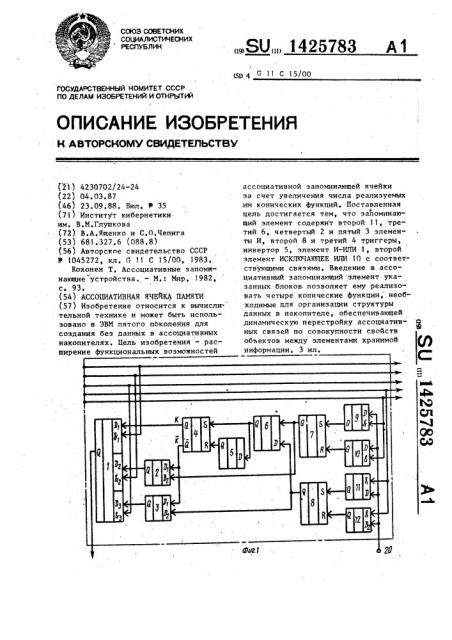

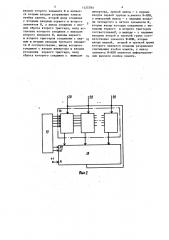

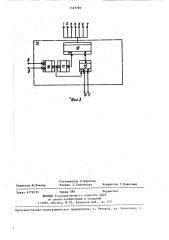

На фиг.! представлена функциональИая схема ассоциативной ячейки памя ти; на фиг. 2 — структурная схема

1 ! ассоциативного запоминающего устройства; на фиг, 3 — структурная схема 15

1лока управления.

Ассоциативная ячейка памяти содерит элемент И-ИЛИ 1, четвертый 2 и ятый 3 элементы И, третий триггер 4, Инвертор 5, третий элемент И 6, пер- 20

ый 7. и второй 8 триггеры, первый рлемент И 9, первый элемент ИСКЛ ОЧА ОЩЕЕ ИЛИ 10, второй элемент И 11, вто рой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12.

Ассоциативное запоминающее уст ойство содержит блок 13 управления, ;,блок 14 ассоциативных ячеек памяти, накопитель 15. Блок 13 управления ! ,состоит иэ элемента И 1б, счетчика

;17 задержки, блока 18 памяти микроко-3О ианд и счетчика 19 адреса микрокоманд.

Кроме того, обозначены (фиг, 1-3) ! . — информационный выход; D — инфорационный вход; g — вход выборки; — вход установки триггера; R— ход сброса триггера; g — инверсный

Информационный выход; ЧТ вЂ” вход разрешения чтения; А — адресный вход;

ЗП - вход разрешения записи, . +1

Инкрементный вход. 40

Ассоциативная ячейка памяти реализует следующие логические функции:

A m» ° 1 ihA 11 (), АЬ,„) А, 45

I !

А ),, 1 A m,1. À(,1) j,l (3)

А А, фА1,„1,, (4) где m 1,2,3,4..., К, число ячеек в матрице накопителя;

1 2 3 4 ... K-1;

1,2,3,4,... число разрядов

s ячейке матрицы, причем при

m.— 2 .1 =1

9 О Ф

31 1929

m 1ф = 1,2ф39 е 1 4

m = К,1 = 1,2,3...,,К-1.

Запоминающее устройство, использующее ассоциативные ячейки памяти, работает следующим образом, Иа входные шины 20 ассоциативной ячейки последовательно подаются признаки объектов В, где (m 1,2, 3,,-,). По управляющим сигналам блока 13 управления осуществляется запись объектов В у в блок 14 ассоциативных ячеек, выполняются логические функции 1 — 4 и в соответствии с результатами этих функций по сигналу с блока 13 управления осуществляется запись одной из функций в накопитель 15. Таким образом, в накопителе 15 формируется матрица ассоциативных связей (по совокупности свойств объектов) между ячейками с хранимой информации, Считывание информации из ассоциативной ячейки памяти осуществляется по управляющим сигналам блока 13 управления.

Блок 13 управления представляет о микропрограммное устройство управления, Управляющие сигналы (микрокоманды) хранятся в блоке !8 перепрограммируемой памяти микрокоманд блока 13 управления. Микрокоманда имеет вертикальное кодирование микроопераций. Циклы в микропрограмме организованы многократным повторением одних и тех же микрокоманд, число которых равно параметру цикла °

Ф

Формула изобретения

Ассоциативная ячейка памяти, содержащая первый элемент И, первый элемент ИСКЛ!ОЧИ!!ЕЕ ИЛИ и первый триггер, вход установки которого соединен с выходом первого элемента И, а вход сброса — с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены с первым и вторым входами первого элемента И соответственно и являютсм первым входом разрешения записи и информационным входом ячейки памяти соответственно, о т л и ч а ю щ а яс,я тем, что, с целью расширения функциональных возможностей ассоциативной ячейки памяти за счет увеличения числа реализуемых логических функций, оня содержит с второго по пятый элементы И, второй и третий триггеры, инвертор, элемент И-ИЛИ, втсрой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с первым

1425783 4 входом второго элемента И и являет- инвертора, прямой выход — c первым ся вторым входом разрешения записи входом первой группы э .емента И-KIH ячейки памяти, вто ой вхо сое инеи р вх д соединен а инверсный выход — с первьпж входас вторыми входами пе вого и вто ого ервого и второго ми четвертого и пятого элементов И, вторые. входы которых соединены с выдом сброса второго т игге а вхо р р pHFrepa, вход ус- ходами первого и второго триггеров тановки которого соединен с выходом соответственно, а выходы — с первыми второго элемента И, выходы первого входами второй и третьей групп сооти второго триггеров соединены с пер" Ig ветственно элемента И-HJIH, вторые вым и вторым входами третьего элемен-. входы первой, второй и третьей групп та И соответственно етственно, выход которого которого являются входами разрешения соединен с входом инвертора и входом считывания ячейки памяти, а выход установки первого триггера, вход элемента И-ИЛИ является информационсброса которого соединен с выходом 15 ным выходом ячейки памяти.

1425783

Ю 11

Составитель С.Королев

Техред Л.Сердюкова Корректор Г. ешетник

Редактор М.Бланар

Заказ 4779/52

Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4