Частотный детектор

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51)4 Н 03 D 3/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ЗЯ

I

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTGPCHGMV СВИДЕТЕЛЬСТВУ (21 ) 4173895/24-09 (22) 04.01.87 (46) 23,09.88. Бил, N- 35 (71) Львовский политехнический институт им. Ленинского комсомола (72) А.М.Агизим, И.П.Карплюк9

А.Е.Фриш и Л.Е.Добродняк (53) 621.376(088.8) (56) Авторское свидетельство СССР

У 1059659, кл. Н 03 D 3/00, 19.02.82.

Вых (54) ЧАСТОТНЫЙ ДЕТЕКТОР (57) Изобретение относится к радиоизмерительной технике и предназначено для выделения частотной огибающей сигнала. Цель изобретения — повышение помехоустойчивости по отношению к

ВЧ-помехам. Частотный детектор содержит входной формирователь импульсов (ФИ) 1, D-триггеры 2, 3, генератор 4 тактовых импульсов, счетчик 5

„„SU, 1425805 А1 импульсов, выходной ФИ 6, фильтр нижних частот 7. В устройство введены блок 8 одноразрядного оперативного запоминающего устройства и элемент

ИСКЛ10ЧАНЩЕЕ ИЛИ 9, Помехоустойчивость повышается эа счет последовательного применения промежуточного запоминания, введения задержки и выполнения логической операции антисовпадения над временными последовательностями задержанных и незадержанных логических сигналов. Обеспечивается увеличение помехоустойчивости в 16 раз. Предел помехозащищенности достигается при перекрытии во времени задержанных и неэадержанных импульсов дребезга, т.е. когда величина задержки недостаточно велика, что накладывает ограничения на ширину частотного диапазона детектируемых частотных огибающих. 1 ил.

1425805

Изобретение относится к радиоизмерительной технике и предназначено дпя выделения частотной огибающей сигнала, 5

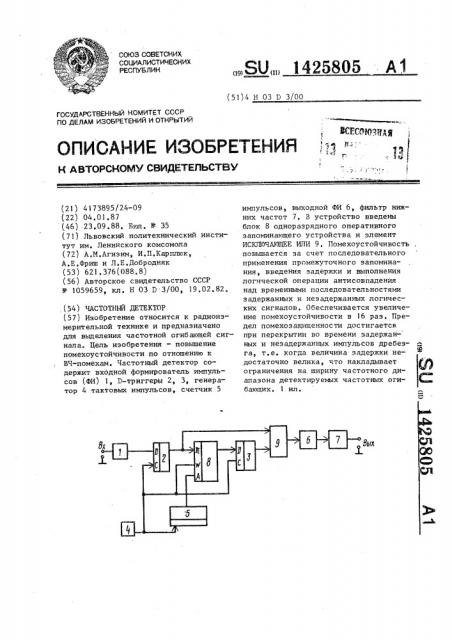

Цель изобретения — повышение помехоустойчивости по отношению к высокочастотным помехам, На чертеже приведена функциональная электрическая схема частотного детектора.

Частотный детектор содержит входной формирователь 1 импуль-.ов, первый 2 и второй 3 D-триггеры, генератор 4 тактовых импульсов, счетчик 5

Импульсов, выходной формирователь б

1лмпульсов, фильтр 7 нижних частот, блок 8 одноразрядного оперативного запоминающего устройства (ОЗУ) и эле-мент ИСКЛЮЧАЮЩЕЕ ИЛИ 9, Q

Частотный детектор работает следующим образом.

Частота тактовых импульсов должна быть выше частоты импульсов помехи, которая превышает в 10-100 раз частоту сигнала. Цикл работы начина ется с чтения блока 8 ОЗУ (длительI ! ность определяется паузой между им пульсами генератора 4 тактовых импульсон).„ затем следует запись новой информации (длительность определяется тактовым импульсом) в ячейку блока 8

ОЗУ с тем же адресом, а по заднему фронту импульса генератора 4 производится перестройка счетчика 5. Таким образом, чтение записанной в момент времени информации производится в момент времени t< — -1л+V.

При реально встречающихся соотношениях амплитуд сигнала и помехи всег40 да можно выбрать необходимую величину L таким образом, чтобы сформированные импульсы дребезга на переходе сигнала из минуса в плюс после задержки на C. совпадали по времени с непрерывной вершиной импульса с выхода триггера 2,,а сформированные импульсы дребезга на переходе сигнала из плюса в минус — с непрерывной вер шиной задержанного на Г импульса с выхода триггера 3. Такие временные со50 отношения приводя т к посл едо ват ельному появлению на ьыходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9 повторения и инверсии импульсов дребезга вокруг моментов

5Г перехода сигнала через нуль в обоих

MTO H IIpBB0pHT к rtocTOянству вольтсекундной площади дпя данного мгновенного периода детектируемого сигнала. При этом не требуется симметричность расположения многократных переходов через нуль относитель но истинных нулей сигнала, Максимально необходимый объем ОЗУ определяется как произведение минимального полупериода полезного сигнала на частоту тактовых импульсов. Например, длительность полупериода больше 50 мкс, а частота генератора 4 тактовых импульсов равна 20 МГц, тогда объем ОЗУ составляет 1000 бит, что легко реализуется.

Помехоустойчивость повышается за счет последовательного применения промежуточного запоминания, введения задержки и выполнения логической операции антисовпадения над временными последовательностями задержанных и незадержанных логических сигналов.

Обеспечивается увеличение помехоустойчивости примерно в 16 раз. Предел помехозащищенности достигается при перекрытии во времени задержанных и незадержанных импульсов дребезга, т,е. когда величина задержки Г недостаточно велика, что накладывает ограничения на ширину частотного диапазона детектируемых частотных огибающих.

Входным формирователем может служить компаратор серии 594 или 521, триг-. геры, счетчик, выходной формирователь и элемент ИСКЛЮЧА10ЩЕЕ ИЛИ могут быть реализованы на серии 533.

Формула и э о б р е т е н и я

Частотный детектор, содержащий входной формирователь импульсов, первый и второй D-триггеры, последовательно соединенные генератор тактовых импульсов и счетчик импульсов, а также последовательно соединенные вы— ходной формирователь импульсов и фильтр нижних частот, о т л и ч аю шийся тем, что, с целью повышения помехоустойчивости по отношению к высокочастотным помехам, введены блок одноразрядного оперативного запоминающего устройства и элемент

HCKJIN×AIOÙÅE ИЛИ, при этом выход входного формирователя импульсов соединен с D-входом .первого D-триггера, выход которого соединен с информационным входом блока одноразрядного оперативного запоминающего устройства и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход блока одноразрядного оператив1425805

Составитель В, Цветков

Редактор И.Булла Техред N. Ходанич Корректор N.Васильева

Заказ 4781/53 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 ного запоминающего устройства соединен с D-входом второго D-триггера, выход которого подключен к второму входу элемента ИСКЛОЧАМЩЕЕ ИЛИ, выход элемента ИСКЛ10ЧАН)ЩЕЕ ИЛИ соединен с входом выходного формирователя импульсов, причем, тактовые входы первого и второго D-триггеров и вход управления записью блока однораврядноro оперативного запоминающего устройства подключены к выходу генератора тактовых импульсов, а адресные

5 входы блока одноразрядного оперативного запоминающего устройства соеди" нены с соответствующими выходами счетчика импульсов,