Делитель частоты с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

Изобретекие относится к импульсной технике и может быть использовано в системах цифрового синтеза частоты с делителем с дробнопеременным коэффициентом деления. Цель изобретения - расширение функциональных возможностей - достигается за счет обеспечения возможности уменьшения или увеличения коэффициента деления на целое число при одновременном повышении быстродействия. Делитель содержит счетчик 1 импульсов, блок 2 сравнения кодов, сдвиговый регистр 3, дешифратор 4, регистр 5 хранения, шины: входную 6, управления 7, первую 8 и вторую 9 - сигналов манипуляции , выходную 10. В предлагаемом делителе повьш1ается быстродействие за счет того, что под действием импульсов на входе синхронизации блока 2 можно сразу сдвигать содержимое регистра 3. 2 ил. § (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1425825 А 3 (51) 4 Н 03 К 23/66

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ У СВИДЕТЕЛЬСТВУ

Ь

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4124257/24-21 (22) 30.06.86 (46) 23.09.88.Бюл. Р 35 (72) Н.А.Чечеткина, Л.Н.Новиков и Э.В.Волков (53) 621.374 (088.8) (56) Авторское свидетельство СССР

У 1115238, кл. Н 03 К 23/66, 04.10.82.

Авторское свидетельство СССР

У 940316, кл. Н 03 К 23/66, 29.12.80. (54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ

КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ (57) Изобретение относится к импульсной технике и может быть использовано в системах цифрового синтеза час- тоты с делителем с дробнопеременным коэффициентом деления. Цель изобретения — расширение функциональных возможностей — достигается за счет обеспечения возможности уменьшения или увеличения коэффициента деления на целое число при одновременном повышении быстродействия. Делитель со.держит счетчик 1 импульсов, блок 2 сравнения кодов, сдвиговый регистр 3, дешифратор 4, регистр 5 хранения, шины: входную 6, управления 7, первую 8 и вторую 9 — сигналов манипуляции, выходную 10. В предлагаемом делителе повышается быстродействие за счет того, что под действием импульсов на входе синхронизации блока 2 можно сразу сдвигать содержимое регистра 3. 2 ил.

1425825, 2

Изобретение относится к импульсной технике, в частности к делителям частоты, предназначенным для использования в системах цифрового синтеза частот с делителем с дробнопеременным коэффициентом деления.

Цель изобретения — расширение функциональных возможностей за счет обеспечения возможности уменьшения или увеличения коэффициента деления на целое число при одновременном повышении быстродействия.

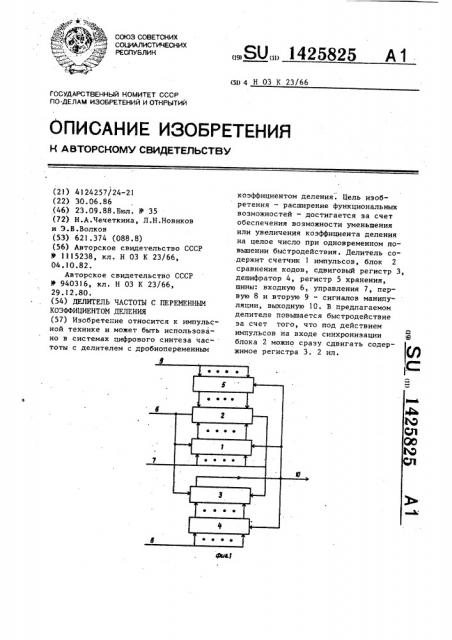

На фиг,1 представлена структурная электрическая схема делителя частоты !5 с переменным коэффициентом деления; на фиг.2 — вариант построения сдвигового регистра переменной длины.

Делитель частоты содержит счетчик

I импульсов,, блок 2 сравнения кодов,,20 сдвиговый регистр 3, дешифратор 4, регистр 5 хранения (параллельный), входную шину 6, шину 7 управления, первую и вторую шины 8 и 9 сигналов манипуляции и выходную шину 10, кото- 25 рая соединена с выходом сдвигового регистра 3 и с входами: синхронизации дешифратора 4 и записи счетчика 1 импульсов и регистра 5 хранения.

Входная шина 6 соединена с тактовым 30 входом сдвигового регистра 3, с .входом синхронизации блока 2 сравнения кодов и со счетным входом счетчика 1 импульсов, информационные входы которого соединены с шиной

7 управления. Первая и вторая группы информационных входов блока 2 сравнения кодов соединены с выходами соответственно счетчика 1 импульсов и регистра 5 хранения, выход — с инфор- 40 мационным входом сдвигового регистра

3, управляющие входы которого соеди— нены с вьиодами дешифратора 4, информационные входы которого соединены с первой шиной 8 сигнала манипуля- 45 ции. Информационные входы регистра

5 хранения соединены с второй шиной

9 сигнала манипуляции, Сдвиговый регистр 3 (регистр переменной длины) состоит из группы

D-триггеров 11.1,...,11.М-1, 11.M и группы мультиплексоров 12.1,. ° ., 12.М-1. На информационный вход 13 сдвигового регистра 3 подается сигнал с выхода блока 2, а на управляющие входы 14.1,...,14.М-1 — сигналы с выхода дешифратора 4. На информационный вход триггера 11.i+1 через мультиплексор 12.i поступает либо сигнал с шины 13, если на управляющем входе 14. логическая единица, либо сигнал с выхода триггера ll.i если на управляющем входе 14.i логический нуль. Таким образом, подавая различные комбинации сигналов на уп- равляющие входы 14,1, °,14.М-I, можно получать различные пути прохождения сигнала с шины 13 на выходную шину 10 и, тем самым, менять разрядность регистра 3 от 1 до M.

Делитель частоты работает следующим образом.

Работа устройства происходит идентичными циклами. Под действием входного импульса с шины 6 с выхода регистра 3 на шине 10 появляется логическая единица. Счетчик lпереходит в состояние, при котором его счетный вход закрыт и производится запись кода с шины 7. На втором информационном входе блока 2 и управляющих входах регистра 3 через регистр 5 сигна лом с шины 9. и через дешифратор 4 сигналом с шины 8 устанавливается число, с которым сравнивается в блоке

2 код счетчика 1, и разрядность регистра 3. С этого момента начинается условно счет входных импульсов.

Первый импульс с шины 6 устанавливает на выходной шине 10 лбгический нуль, счетчик 1 начинает счет входных импульсов от установленного в нем кода. После того как код в счетчике 1 совпадает с установленным в блоке 2, следующий импульс формирует на выходе блока 2 логическую единицу, которая поступает на . информационный вход регистра 3. Каждым очередным импульсом с шины 6 содержимое регистра 3 сдвигается на один разряд влево. Если регистр 3

r-разрядный где r меняется от 1 до

М, то с r-ным импульсом на шину 10 с выхода регистра 3 поступает логическая единица. Далее начинается очередной цикл работы, протекающий аналогично рассмотренному. Таким образом, на шине 10 формируется под действием фронтов входного сигнала импульс длительностью, равной длительности периода входного сигнала.

Если в качестве счетчика 1 испольэовать вычитающий счетчик, то коэффициент деления определяется по формуле

N=K+r -1+2, Фиа2

Составитель А.Соколов

Редактор Н.Яцола Техред А.Кравчук - Корректор М.Пожо

Тираж 928 Подписное

ВПИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4782/54

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

1425 где К вЂ” прямой код числа на шине в соответствующей счетчику 1 системе счисления;

r †-разрядность регистра 3, при5 чем r = 1,М;

М вЂ” максимальная длина регистра

3;

1 — прямой код числа на шине 9 в соответствующей счетчику 1 системе счисления.

Пусть 1 2,M+3, тогда диапазон дискретного изменения частоты сигнала на шине 10 при фиксированном К определяется выражением 15 ах ех кх

c ----- p

К+М - ьых - K-М где М 1, К » 1.

Минимальный коэффициент деления частоты равен N „н 3, 20

Увеличение быстродействия делителя частоты с переменным коэффициентом деления по сравнению с известным достигается за счет того, что после появления логической единицы под действием импульса на входе синхронизации блока 2 можно сразу сдвигать содержимое регистра 3, т.е. не требуется время для параллельной записи: информации в этот регистр. Кроме то- 30 го, использование в регистре 3 D-триггеров с одним информационным входом позволяет применять элементы в этих

D-триггерах более низкого быстро-, действия, чем в счетчике 1.

825

Формула изобретения

Делитель частоты с переменным коэффициентом деления, содержащий счетчик импульсов, счетный вход которого соединен .с входом синхронизации блока сравнения кодов, с тактовым входом сдвигового регистра и с вход- ной шиной, информационные входы — с шиной сигналов управления, разрядные выходы — с первой группой информационных входов блока сравнения кодов, выход которого соединен с информационным входом сдвигового регистра, гГервую шину сигнала манипуляции, отличающийся тем," что, с целью расширения функционапьных возможностей при одновременном повышении быстродействия, ц него введены вторая шина сигнала манипуляции, регистр хранения и дешифратор, информационные входы которого соединены с первой шиной сигналов мани" пуляции, выходы — с управляющими входами сдвигового регистра, выход которого соединен с входом синхронизации дешифратора, с входом разрешения записи счетчика импульсов, с выходной шиной и с входом записи регистра хранения, информационные входы которого соединены с второй шиной сигнала манипуляции, выходы — с второй группой информационных входов блока сравнения кодов.