Преобразователь угла поворота вала в код

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью уменьшения динамической погрешности путем уменьшения времени переходных процессов при отработке рассогласований в преобразователь угла поворота вала в код, содержапщй синусно-косинусньй вращающийся трансформатор (СКВТ), четыре цифроаналоговьгх преобразователя (ЦАП), два аналоговых сумматора, 1Ц1фровой сумматор, реверсивный счётчик, делитель напряжения , два блока функционального преобразования кодов, два формирователя питающих напряжений, компаратор, блок выделения модуля, блок преобразования напряжения в частоту, генератор импульсов, делитель частоты, введены пятьш ЦАП, два интегратора, два элемента выборки - хранения и блок , управления. Из сигналов делителя частоты формирователи вырабатывают напряжения , питающие СКВТ. В цифровом сумматоре, блоках функционального преобразования кодов, трех ЦАП и одном сумматоре вырабатывается компенсационное напряжение, которое на другом сумматоре сравнивается с выходным сигналом СКВТ. Рассогласование по фазе сравниваемых напряжений устраняется путем изменения кода в реверсивном счетчике, а рассогласование по амплитуде - путем изменения коэффициента передачи делителя напрйженйя. 1 3.п.ф-лы, 1 ил, с 4 ГО 01 00 со to

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК,„;SU„„1425832 (gp y Н 03 М 1/48

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H A BT0PCHQMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4218317/24-24 (22) 30.03.87 (46) 23.09.88. Бюл. № 35 (71) Московский инженерно-физический институт (72) А.С. Буянов, И.Г. Креславский

Н.В. Синицын и Н.H. Смирнов (53) 681.325 (088.8) (56) Авторское свидетельство СССР

:¹ 1088045, кл. Н 03 М i/64, 1983.

Авторское свидетельство СССР № 840995, кл. Н 03 М i/64, 1979. (54) ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА

ВАЛА В КОД (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью уменьшения динамической погрешности путем уменьшения времени переходных процессов при отработке рассогласований в преобразователь угла поворота вала в код, содержащий синусно-косинусный вращающийся трансформатор (СКВТ), четыре цифроаналоговых преобразователя (ЦАП), два аналоговых сумматора, цифровой сумматор, реверсивный счетчик, делитель напряжения, два блока функционального преобразования кодов, два формирователя питающих напряжений, компаратор, блок выделения модуля, блок преобразования напряжения в частоту, генератор импульсов, делитель частоты, введены пятый ЦАП, два интегратора, два элемента выборки — хранения и блок управления. Из сигналов делителя частоты формирователи вырабатывают напряжения„ питающие СКВТ. В цифровом сумматоре, блоках функционального преобразования кодов, трех ЦАП и од- щ ном сумматоре вырабатывается компенсационное напряжение, которое на другам сумматоре сравнивается с выводным С сигналом СКВТ. Рассогласование по фазе сравниваемых напряжений устраня- ф ется путем изменения кода в реверсивном счетчике, а рассогласование по амплитуде — путем изменения коэффициента передачи делителя напряжения.

1 з.п.ф-лы, 1 ил, СЛ

1425832

Изобретение относится к автоматике и вычислительной технике и может . быть использовано для связи аналого.вых источников информации с цифровым вычислительным устройством.

Цель йзобретения — уменьшение динамической погрешности преобразователя путем уменьшения времени переходных процессов при отработке рас- 10 согласований.

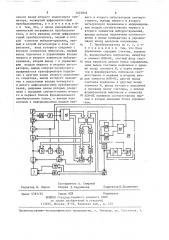

На чертеже представлена структур. ная схема преобразователя.

Преобразователь содержит синуснокосинусный вращающийся трансформатор (СКВТ) 1, аналоговые сумматоры 2 и 3, цифроаналоговые преобразователи (ЦАП)

4 и 5, интеграторы 6 и 7, компаратор 8, блок 9 преобразования напряжения в частоту, реверсивный счетчик 20

i0 генератор !1 импульсов, делитель

12 частоты, цифровой сумматор 13 блоки 14 и 15 функционального преобразования кодов, формирователи 16 и 17 питающих напряжений, ЦАП 18-20, 25 делитель 21 напряжения, элементы 23 и 23 выборки — хранения, блок 24 выделения модуля, блок 25 управления, Блок 25 управления содержит счетчик

26, элемент И 27, инвертор 28, фор- 30 мирователь 29 импульсов и элемент

ИЛИ-НЕ 30.

Преобразователь угла поворота вала в код работает следующим образом.

От генератора 11 импульсы поступают на делитель 12 частоты. Значения разрядов делителя 12 частоты подаются на входы формирователей 16 и 17 синусоидальных напряжений питания, которые подаются на входы CKBT 1.

Компенсационное напряжение, поступающее на вход аналогового сумматора

2 со сдвигом фазы, задаваемым кодом реверсивного счетчика 10, формируется грубо-точным способом. Формирова— 45 ние синусоидального сигнала со сдвигом фазы в пределах п старших разрядов реверсивного счетчика 10 осуществляется путем их сложения с выходами разрядов делителя 12 частоты в сумматоре i3 Выходной код сумматора

13, представляющий собой линейно изменяющийся код со сдвигом фазы отчосительно выходного кода делителя 12 частоты на величину, задаваемую кодом и старших разрядов реверсивного счетчика 10, преобразуется блокамн 14 и 15 в коды синуса и косинуса. Блоки 14 и 15 представляют собой блоки постоянной памяти с прошивкой функций синуса и косинуса. ЦАП 18 и 19 преобразуют выходные коды блоков 14 и 15 в напряжение. На выходах ЦАП 18 и 19 формируются напряжения, аппроксимирующие синусоидальные и косинусоидальные функции выходных кодов сумматора

13 со сдвигом фаз относительно выходных сигналов формирователей 16 и 17 синусоидальных напряжений на величину, задаваемую грубо кодом старших п разрядов реверсивного счетчика 10.

Фазовый сдвиг выходного сигнала ЦАП

18 в пределах кванта выходного кода сумматора 13 осуществляется путем

его суммирования в аналоговом су жаторе 3 с выходным сигналом ЦАП 19, промодулированным по амплитуде в ЦАП

20 кодом ш младших разряцов реверсивного счетчика 10. Согласованис величин сдвигов фаз, задаваемых кодами младших и старших разрядов реверсивного счетчика 10, осуществляется при помощи задания коэффициентов суммироBBHHR в аналоговом сумматоре 3 выходных напряжений ЦАП 18 и 20.

Сформированное компенсационное напряжение с выхода аналогового сумматора 3 через управляемый делитель 21 напряжения и выходное напряжение СКВТ

1 подаются на входы аналогового сум-, матора 2.

Для малых значений разбалансов фаз

Мои амплитуд 6.U соответствующих основному режиму работы преобразователя угла поворота вала в код, выходной сигнал .сумматора 2 на осчовной частоте И можно представить выражением

U> U(aUsinut + ьЦ cosut) .

Выходное напряжение аналогового сумматора 2 умножается в ЦАП 4 и 5 на коды косинуса и синуса, сформированные в блоках 15 и 14 соответственно. Выходные сигналы ЦАП 4 и 5 интег1

2Я рируются в течение периода Т = — в

Я интеграторах 6 и 7 сооветственно. Выходные напряжения интеграторов 6 и 7 в момент времени Т после начала интегрирования пропорциональны соответственно разностифаз Ь у и разбалансу амплитуд 6U между выходным напряжением

СКВТ 1 и компенсирующим напряжением с выхода делителя 21.

32 4 преобразования, то требуется автоматически регулировать ее до минимума.

Минимизация разности амплитуд Ц осуществляетсн при помощи следящей системы, состоящей из аналогового сумматора 2, ЦАП 5, интегратора 7, элемента 23 выборки-хранения и управляемого делителя 21 йапряжения, путем преобразования величины разности амплитуд ЛП выходного напряжения СКВТ 1 и компенсирующего напряжения в пропорциональное ему постоянное напряже" ние, которое изменяет величину коэффициента передачи управляемого делителя 21 напряжения, изменяя таким образом амплитуду компенсирующего напряжения до сведения к нулю разности амплитуд.

Формула изобретения

1. Преобразователь угла поворота вала в код, содержащий компаратор, генератор импульсов, выход которого подключен к входу делителя частоты, I выходы разрядов делителя частоты подключены к первой группе входов цифрового сумматора и входам первого и второго формирователей питающих напряжений, выходы которых подключены к входам синусно-косинусного вращающе" гося трансформатора, вход компаратора соединен с входом блока выделения модуля, выход K0TGpol o подключен к входу блока преобразования напряжения в частоту, выход которого и выход компаратора подключены соответственно к счетному и управляющему входам реверсивного счетчика, выходы старших разрядов реверсивного счетчика под". ключены к второй группе входов цифрового сумматора, а выходы младших разрядов — к цифровым входам первого цифроаналогового преобразователя, вык входам первого и второго блоков функционального преобразования кодов, выходы которых подключены к входам соответственно второго и третьего цифроаналоговых преобразователей, выход третьего цифроаналогового пре-, образователя подключен к аналоговому входу первого цифроаналогового преобразователя, выходы первого и второго цифроаналоговых преобраэователей подключены к входам первого аналогового сумматора, выход которого через делитель напряжения подключен к

3 14258

Временные режимы (циклы) работы интеграторов 6 и 7 элементов 22 и 23, выборки-хранения задаются при помощи блока 25 управления. Один цикл преобразования задается немногим больше времени одного периода Т напряже-. ний питания СКВТ 1 при помощи деления частоты генератора 11 на 2 + 2

n . % в делителе и его сброса выходным им- 10 пульсом элемента И 27.

Управляющий импульс элементов 22 и 23 выборки-хранения вырабатывает элемент 29 по переднему фронту импульсов n+1-го разряда делителя частоты. Импульс, управляющий сбросом интеграторов 6 и 7, вырабатывается при помощи элемента И и элемента ИЛИ-НЕ

30 из импульсов n+i-го разряда делителя частоты и выходных импульсов 20 элемента 29. Импульсы сброса интеграторов 6 и 7 начинаются в моменты окончания импульсов, управляющих элементами 22 и 23 выборки-хранения, и оканчиваются в моменты, когда начина- 25 ется новый цикл деления делителя частоты. Таким образом, в каждом цикле преобразования на выходе элементов 22

Й 23 выборки-хранения выделяются и хранятся постоянные напряжения, про-3р порциональные соответственно величинам фазового g(g и амплитудного а0. разбалансов выходного напряжения СКВТ 1 и компенсирующего напряжения.

Информацию о разности сдвигов фаз выходного напряжения СКИТ 1 и компенсирующего напряжения, т.е. о разности углового положения вала СКВТ 1 и выходного кода преобразователя, представленного кодом реверсивного .40 счетчика 10, несет напряжение на выходе элемента 22 выборки-хранения, которое преобразуется компаратором 8 в сигнал направления счета реверсивного счетчика 10, а блоком 24 выделе- 45 ния модуля напряжения и блоком 9 пре- ходы цифрового сумматора подключены образования напряжения в частоту — в последовательность счетных импульсов реверсивного счетчика 10. Код реверсивного счетчика 10 изменяется до сведения к нулю разности фаз выходного напряжения СКВТ 1 и компенсирующего напряжения.

Разность амплитуд aU выходного напряжения СКЕТ 1 и компенсирующего напряжения не является носителем информации об угловом положении вала СКВТ

1. Однако поскольку наличие разности амплитуд а0 приводит к погрешности

Составитель А„ Смирнов

Техред Л.Сердюкова

Корректор Л,Пилипенко

Редактор Н. Яцола

Заказ 4783/55 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 11(-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 5 14258 одному входу второго аналогового сум- матора, четвертый цифроаналоговый преобразователь, о т л и ч а ю щ и йс я тем, что, с целью уменьшения динамической погрешности преобразователя, в него введены пятый цифроаналоговый преобразователь, первый и второй элементы выборки-хранения, первый и второй интеграторы и блок управления, вход которого соединен с выходом генератора импульсов, первый выход подключен к управляющим входам первого и второго элементов выборкихранения, второй выход - к управляющим входам первого и второго интеграторов, выход синусно-косинусного вращающегося трансформатора подключен к другому входу второго аналогового сумматора, выход которого подключен к аналоговым входам четвертого и пятого цифроаналоговых преобразователей, цифровые входы которых соединены с выходами соответственно второго и первого блоков функционального 2б преобразования кодов, а выходы подключены к информационным входам первого и второго интеграторов соответственно, выходы первого и второго интеграторов подключены к информационным входам соответственно первого и второго элементов выборки-хранения, выходы которых подключены соответственно к входу компаратора и управляющему входу делителя напряжения.

2. Преобразователь по п. 1, о тл и ч а ю шийся тем, что блок управления содержит счетчик, элемент

И, формирователь импульсов, инвертор и элемент ИЛИ-НЕ, счетный вход счетчика является входом блока управления, один выход счетчика подключен к одному входу элемента И, а через инвертор и формирователь импульсов соответственно к первому и второму входам элемента ИЛИ-НЕ, другой выход счетчика подключен к другому входу элемента И, выход которого подключен к нулевому входу счетчика, а выходы формирователя импульсов и элемента

ИЛИ-НЕ являются соответственно первым и вторым выходами блока управления.