Формирователь цифровых сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - обеспечение возможности формирования сигналов изменяемой амплитуды и частоты , меньшей частоты дискретизации. Формирователь содержит блок управления (БУ) 1 памятью, заданлций г-р 2, блок формирования (БФ) 3 параметров сигналов, счетчик 4 адреса, буферный регистр 5 и БФ 6 - 8 цифровых потоков , каждьй из которых состоит из эл-та 9 памяти, регистра 10 синхросигнала и преобразователя 11 кода, формирователь работает в двух режимах . В режиме записи информация о параметрах синтезируемого сигнала вводится в БУ 1. В нем вычисляются мгновенные значения отсчетов синтезируемого цифрового сигнала, которые последовательно записьшаются в эл-ты 9. После записи N-ro отсчета осу1цествляется считьшание цифровых отсчетов из эл-тов 9 на преобразователи 11. В них полученные цифровые потоки преобразуются в квазитроичньй линейный код. 1 ил., 1 табл. (Л

СООЭ СОНЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК,51) 4 Н 04 J 3/!2

ОПИСАНИЬ ИЗОБРКТКНИя

Н АBTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТНЕННЫЙ КОМИТЕТ СССР

00 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4215195/24-09. (22) 25.03 ° 87 (46) 23.09.88. Бюл. Р 35 (72) В.И.Альбах и В.Г.Шаповальянц (53) 621.395.44:621.37 (088.8) (56) Егранжиев А.Н., Шехтман Б.И.

Генератор цифрового периодического сигнала. — Техника средств связи.

Сер. "Техника радиовещательного приема и акустики". Вып. 3, 1984, с.62-68. (54) ФОРМИРОВАТЕЛЬ ЦИФРОВЫХ СИГНАЛОВ (57) Изобретение относится к электросвязи. Цель изобретения — обеспечение возможности формирования сигналов изменяемой амплитуды и частоты, меньшей частоты дискретизации.

Формирователь содержит блок управления (ВУ) 1 памятью, задающий r-p 2, „„80„„1425860 Я1 блок формирования (БФ) 3 параметров сигналов, счетчик 4 адреса, буферный регистр 5 и БФ б — 8 цифровых потоков, каждый иэ которых состоит из эл-та 9 памяти, регистра 10 синхросигнала и преобразователя 11 кода.

Формирователь работает в двух режимах. В режиме записи информация о

V параметрах синтезируемого сигнала вводится в БУ 1. В нем вычисляются мгновенные значения отсчетов синте, зируемого цифрового сигнала, которые последовательно записываются в эл-ты 9. После записи N-го отсчета осуществляется считывание цифровых отсчетов иэ эл-тов 9 на преобразо- с ватели 11: В них полученные цифроВ вые потоки преобразуются в квазитроичный линейный код. 1 ил., 1 табл.

1425860

Изобретение относится к устройствам электросвязи.

Цель изобретения — обеспечение возможности формирования сигналов изменяемой амплитуды и частоты, меньшей частоты дискретизации.

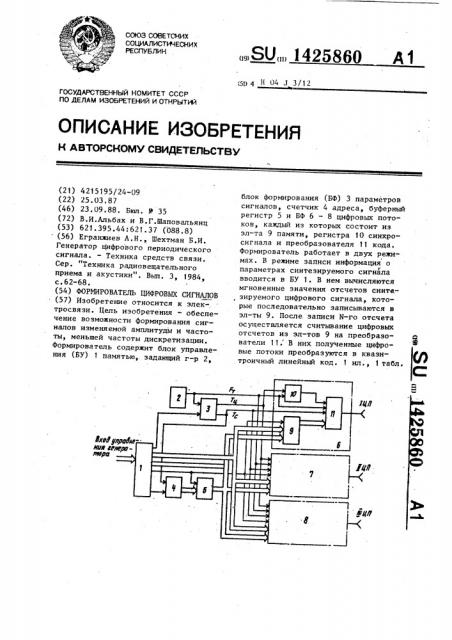

На чертеже представлена функциональная схема предлагаемого формирователя цифровых сигналов.

Формирователь цифровых сигналов содержит блок 1 управления памятью, задающий генератор 2, блок 3 формирования параметров сигналов, счетчик 4 адреса, буферный регистр 5, ; блоки 6 — 8 формирования цифровых потоков, содержащие элемент 9 памя, ти, ре.истр 10 синхросигнала и пре,образователь 11 кода.

Формирователь цифровых сигналов работает в режиме записи и генерирования цифровых сигналов следующим образом.

В режиме записи информация о параметрах синтезируемого сигнала вводится через вход формирователя цифр сигналов в блок 1 управления памятью.

По алгоритму, введенному в блок 1, в нем вычисляются мгновенные значения отсчетов синтезируемого цифрового сигнала и последовательно записываются в элементы 9 памяти блоков

6 — 8 формирования цифровых потоков.

Элемент 9 памяти устанавливается в режим записи сигналом, который формируется на выходе блока 1. Последовательность записи цифровых отсчетов в элемент 9 памяти каждого из блоков 6 — 8 соответствует алгоритму передачи информации, приведенному в таблице.

После записи N-го отсчета в элемент 9 памяти блока 6 элемент 9 памяти устанавливается сигналом в режим чтения, и далее на выходе блока

1 вырабатывается сигнал,,который запускает блок 3 формирования параметров сигналов. После этого буферный регистр 5 подключает выход счетчика 4 адреса. На выходах блока 3 вырабатываются сигналы Т и Т,, определяющие временной цикл аппаратуры.

Сигнал, определяющий длительность слова, поступает на вход счетчика 4 адреса, который работает в циклическом режиме. Цикл работы (диапазон счета) счетчика 4 адреса определяется сигналом, который вырабатывается

S0

55 блоком 1, периодически после считывания последнего отсчета из элемента 9 памяти каждого из блоков 6 — 8.

Считывание цифровых отсчетов из элемента 9 памяти осуществляется одновременно и управляется счетчиком 4 адреса, выход которого через буферный регистр 5 подключен к входам элемента 9 памяти. С вь1хода элемента 9 памяти цифровые отсчеты сигналов в параллельном коде поступают на вход преобразователей 11 кодов, где с помощью сигнала преобразуются в последовательный код. Аналогично с помощью сигнала длительности цикла в регистре 10 синхросигнала синхросигнал (определенный для каждого цифрового потока) хранится и преобразуется в последовательный код, а затем в преобразователе 11 кода вводится в цифровой поток один раз за период цикла. Далее в преобразователях 11 кода полученные цифровые потоки преобразуются в квазитроичный линейный код.

Формула изобретения

Формирователь цифровых сигналов, содержащий задающий генератор, счет-. чик адреса, буферный регистр, о т— л и ч а ю шийся тем, что, с целью обеспечения формирования периодических сигналов изменяемой амплитуды и частоты, меньшей частоты дискретизации, введены блок управления памятью, блок формирования параметров сигналов и три блока формирования цифровых потоков, при этом каждый блок формирования цифровых потоков содержит преобразователь кода, регистр синхросигнала и элемент памяти, выход которого соединен с первым входом преобразователя кода, к

E второму входу которого подключен выход регистра синхросигнала, выход задающего генератора подключен к первому входу блока формирования параметров сигналов, первым входам регистров синхросигналов и третьим входам преобразователей кода соответствующих блоков формирования цифровых потоков, второй вход блока формирования параметров сигналов соединен с первым выходом блока управления памятью, при этом первый выход блока формирования параметров сигналов подключен к вторым входам регистров синхросигнала соответст1425860

Блок формирования цифровых потоков

3-й отсчет

2-й отсчет

1-й отсчет

6-й отсчет

5-й отсчет

4-й отсчет е ° ° ° ° ° 4 ° ° (N-2)-й отсчет а

° 0 ° ° ° f ° 4

Ъ ° ° ° ° ° ° ° ° ° (N-1)-й отсчет &й отсчет

Ф

П р и м е ч а н и е.

N количество отсчетов, необходимое для получения целого периодов синтезируемого сигнала с заданной точностью.

Составитель Т Давыдова

Редактор О.Юрковецкая

Техред М.Ходанич Корректор В.Гирняк

Заказ 4784/56 Тираж 660 Подписное

ВИИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 вующих блоков формирования цифровых потоков, второй выход блока формирования параметров сигналов соединен с первым входом счетчика адреса и с четвертыми входами преобразователей кода соответствующих блоков формирования цифровых потоков, второй выход блока управления памятью соединен с вторым входом счетчика адреса, выход которого подключен к первому входу буферного регистра, второй вход которого соединен с третьим выходом блока управления памятью и с первыми входами элементов памяти,. соответствукпцих блоков формирования цифровых потоков, четвертый выход блока управления памятью соединен с выходом буферного регистра и с вторыми входами элементов памяти соответствующих блоков формирования цифровых потоков; пятый выход блока управления памятью соединен с третьими входами элементов памяти соответствующих блоков формирования цифровых потоков, при этом вход блока управления памятью является входом формирователя цифровых сигналов.