Устройство для синхронизации вычислительной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислителбной технике и может быть использовано при проектировании кшкропроцессорных систем модульного типа. Целью изобретения является повьшение надежности за счет сохранения при выходе из строя одного из блоков вьфаботки синхросигналов синхронной работы остальных групп блоков. Устройство для синхронизации вычислительной системы содержит п блоков (1,-1) выработки синхросигналов. Каждый блок 1; содержит задающий генератор 2, элемент задержки 3.3 ил. с

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

as> ш> (1427 5 (51) 4 С 06 Р 1/04

А1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ,21) 4080485/24-24 (22) 16.04.86 (46) 30.09.88. Вюл. У, 36 (72) А.Н.Латышев, Ю.А.Ушаков и В.Ю,Игнатьев (53) 681.3 (088.8) (56) Авторское свидетельство СССР

Ф 458825, кл. С 06 F 15/16» 1975.

Авторское свидетельство СССР

У 809132, кл. G 06 F 1/04 ° 1979. (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ

ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ (57) Изобретение отнбсится к вычислительной технике и может быть использовано при проектировании микропроцессорных систем модульного тица.

Целью изобретения является повьппение надежности за счет сохранения при выходе иэ строя одного из блоков выработки синхросигналов синхронной работы остальных групп блоков. Устройство для синхронизации вычислительной системы содержит и блоков (1,-1„) выработки синхросигналов. Каждый блок

1; содержит задающий генератор 2, с элемент задержки 3..3 ил. (0

1427355

T ьзо4

Устройство для синхронизации вы» числительной системы, содержащее и

Облоков выработки синхросигналов (где п — число процессоров в системе), о т л и ч а ю щ е е с я тем, что, с целью повьппения надежности эа счет сохранения при выходе иэ строя одного из блоков выработки синхросигналов синхронной работы отдельных групп блоков, каждый блок выработки синхросигналов содержит задающий генератор и элемент задержки, причем.синхровход первого блока выработки синхро35 сигналов является входом запуска устройства, тактовый выход каждого блока выработки синхросигналов является

i-м (где i = 1,,,п) выходом устрой" ства, запускающий выход j-го блока

40 выработки синхросигналов (где j

1,...,n-1) соединен с синхровходом (j +1)-ro блока выработки синхросигналов, причем в каждом блоке выработки синхросигналов синхровход

45 задающего генератора является синхровходом блока, выход задающего генератора соединен с входом элемента задержки и является тактовым выходом блока, выход элемента задержки явля50 ется запускающим выходом блока.

Изобретение относится к вычислительной технике и может быть использовано при проектировании микропроцессорных систем модульного типа.

Цель изобретения — повьппение точности за счет сохранения при выходе из строя одного из блоков выработки синхросигналов синхронной работы отдельных групп блоков.

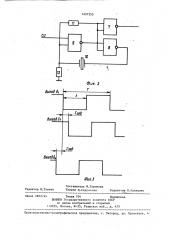

Йа фиг.1 лриведена схема устройства на фиг.2 — схема синхронизируемого генератора тактовых импульсов, на фиг.З вЂ” временная диаграмма работы устройства.

Устройство содержит и блоков (1< -1„) выработки синхросигналов.

Каждьп блок 1 содержит задающий генератор 2, элемент 3 задержки, синхровход 4, запускающий выход 5, тактовый выход 6.

Каждый генератор 2 содержит элементы И-НЕ 7, 8, 9, кварцевьп» резонатор 10, резисторы 11, 12. Работа устройства заключается в том, что импульсы, вырабатываемые синхронизируемым генератором 2< тактовых импульсов, являются синхронизирующими сигналами для работы синхропиэируемаго генератора 2 тактовых импульсов, который, в свою очередь, синхронизирует работу следующего генератора 2> и так далее последовательно до генератора 2„ тактовых импульсов.

Синхронизация оауществляется путем подачи на вход элемента И-НЕ 2 синхрониэирующего отрицательного импульса длительностью t, сдвинутого на величину, запрещающего формирование тактовых импульсов на время

Генератор 2, таким образом, будет генерировать тактовые импульсы, аналогичные тактовым импульсам, вырабатываемые генератором 2 „,, но сдвинутые по фазе на с,м1д .

Элемент 3 задержки введен для того чтобы исключить ситуацию одновремен" ного обращения процессоров к общим ресурсам, что может привести к воз1 никновению помех большой амплитуды по цепям питания. Величина задержки выбирается по формуле где n — максимальное количество процессорных модулей, Т вЂ” период формирования импульсов синхронизации синхронизируемого генератора тактовых импульсов.

При отсутствии синхрониэирующих отрицательных импульсов на синхровходе 4 блока 1 на входе элемента

И-НЕ 9 присутствует высокий логический уровень.

Формула и з о б р е т е н и я

1427355

Фце. 2

ЮФ/И

Юад

Составитель Н.Торопова

Техред Jl.Ceðäþêoâà

Корректор О.Кравцова

Редактор М.Товтин

Заказ 4852/44 Тираж 704 Подписное.

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4