Конвейерный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройс-твах цифровой обработки сигналов. Цель изобретения - расширение функциональных возможностей устройства за счет накопления локальных сумм последовательности чисел . Конвейерный сумматор содержит суммирующие ячейки 1, 2, информационные входы 3, 4, выходы 5, управля- : ющие входы 6, 7, Конвейерный сумматор цюжет реализовать различные вычислительные операции, в частности сложение и вычитание, накопление суммы чисел , последовательно поступакяцих на входную шину сумматора. Наиболее общей операцией, которую реализует предлагаемый сумматор, является вычисление локальных сумм m чисел из входной последовательности чисел. При этом в данном конвейерном сумматоре совмещается вьтолнение операции вычитания двух чисел и накопление полученг ых разностей, t, з.п, ф-лы. Зил. о « (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11)(51)4 G 06 F 7 50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ASTOPCHOMV СВИДЕТЕЛЬСТВУ

° ° °

° ° °

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

llO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4215144/24-24 (22) 25,03.87 (46) 30.09.88. Бюп. 36 (71) Физико-механический институт

АН УССР (72) В.В.Грицык, И.Г.Любецкая, P.Ì.Ïàëåíè÷êà и Г.Т.Черчик (53) 681.325.5(088.8) (56) Авторское свидетельство СССР

9 1190380, кл. G 06 F 7/50, 1985.

Авторское свидетельство СССР

1) 1067499, кл. G 06 F 7/50, 1982. (54) I

1427

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой обработки сигналов например для сглажиФ 1

5 вания видеосигнала телевизионного изображения.

Известен конвейерный накапливающий сумматор, содержащий параллельные сумматоры, элементы задержки суммы, элементы задержки переноса, распределитель импульсов, элементы задержки входного кода, элементы И-НЕ, элементы И, входные кодовые шины, выход синхронного переноса, шину запуска, шины синхронной суммы, вход сброса, вход разрешения смены кода и тактовую шину.

Цель изобретения — расширение функциональных возможностей за счет 20 возможности накопления локальных сумм последовательности чисел.

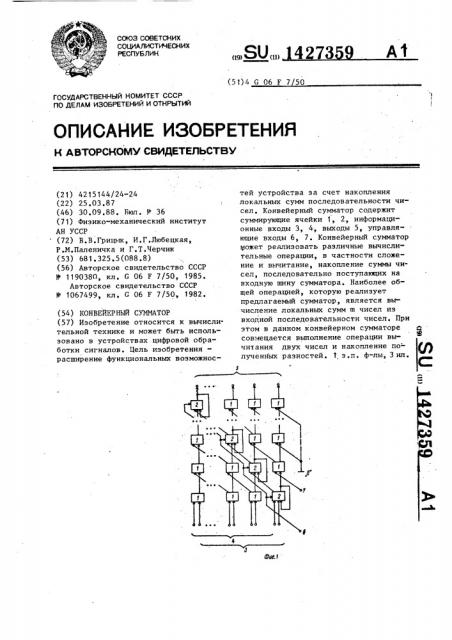

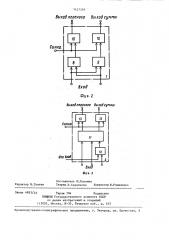

На фиг.1 представлена функциональная схема конвейерного сумматора, на фиг.2 — пример выполнения суммирующих25 ячеек, кроме (К,K)-ых, где К = 1,n,п-разрядность операндов на фиг.3функциональная схема (К,К)-ой суммирующей ячейки.

Конвейерный сумматор (фиг.1) со- 30 держит суммирующие ячейки 1, 2, информационные входы 3, 4, выходы 5, управляющие входы 6, 7. Каждая суммирующая ячейка (фиг.2), кроме (К, К)-ой содержит элемент И 8, элемент ИСКЛЮЧАЮЩЕЕ KIH 9, триггеры 10.

Каждая (К,К)-ая суммирующая ячейка (фиг.3) содержит одноразрядный сумматор 11, элемент И 12, триггеры 13.

Конвейерный сумматор работает сле* дующим образом.

При подаче на первый вход 6 управления сигнала "0" данный сумматор осуществляет сложение (вычитание) ко" дов входных чисел. Для реализации вычитания вычитаемое число поступает на вторую входную шину 4,в инверсном двоичном коде, а на второй вход 7 управления подается сигнал "1". Для работы в режиме накапливающего сумматора на первый вход 6 управления пода- 50 ется сигнал "1", а на второй вход 7"0". Суммируемые числа поступают последовательно на вход 3 в прямом двоичном коде, в то время как на разрядах входа 4 присутствуют сигналы "0".55

Наиболее общей операцией, которую реализует сумматор, является вычисление локальных сумм чисел из после359 2 с довательности двоичных чисел, которые. последовательно подаются на входную шину 3. В данном случае сумматор реализует следующую формулу рекурсивного вычисления локальных сумм m чисел:

S, = Si„+ a, - ai, - (1) где S — сумма последовательных чисел, вычисленная относительно числа а, т.е. и51 (2) к=о

Sq1, — сумма m последовательных чисел, вычисленная относительно числа а; „.

Таким образом, данный конвейерный сумматор может быть использован для скользящего усреднения (сглаживания) последовательности двоичных чисел, т.е. отсчетов сигнала по следующей формуле:

КИ \ у; =«" Га;„, m

К о где у — результат скользящего усреднения.

Когда m является степенью двойки, т.е. ш = 2, то операция деления вые числительной суммы на m соответствует сдвигу кода суммы вправо на 1 разрядов. Поэтому данный сумматор при наличии элементов задержки (регистров) на m чисел для задержки а; „„ может реализовать операцию скользящего усреднения.

При реализации операции вычитания п-ый разряд двух входных шин сумматора является знаковым разрядом.

Для конвейерной реализации вычисления суммы m чисел по формуле (1) числа на вход 4 должны быть представлены в дополнительном двоичном коде. Для этого они подаются на вход

4 в инверсном коде, а для получения дополнительного кода в процессе суммирования к младшему (первому) разряду добавляется единица путем подачи сигнала "1" на второй вход суммирующей ячейки 1 с номером (2,1) с второго входа управления сумматора. Это дает возможность сэкономить схемотехнические затраты на преобразование прямого кода в дополнительный.

Когда числа входной последовательности кодируются р-разрядными двоичI ными кодами, то для вычисления локальных сумм (2) разрядность и кон-. вейерного сумматора должна превышать число (р + logjam). Сумматор работает в параллельно-конвейерном режиме, для

3 142 чего в суммирующих ячейках используются фиксаторы результата суммирования, реализованные в виде триггеров.

В каждом такте работы сумматора на его входы 3 и 4 подаются коды новых суммируемых чисел, а результаты промежуточных вычислений фиксируются в триггерах 10 и 13. Результат суммирования, например, вычисления локальных сумм по рекуррентному соотношению (1), поступает на выход 5.

Формула изобретения

1. Конвейерный сумматор, состоящий из матрицы и суммирующих ячеек, где n — разрядность операндов, выход суммы (i j)-ой ячейки которой, где — номер строки матрицы à j — номер столбца матрицы, i = 1,п-1, 1,п-1, соединен с первым входом (i+1 1)-ой суммирующей ячейки, вторые входы ячеек с номерами (i,1), где

=, 3,п подключены к шине нулевого потенциала сумматора, первый информационный вход (1,j)-ой ячейки, где

1 = 1,n, соединен с j-ым разрядом первого информационного входа сумматора, отличающийся тем, что, с целью расширения функциональных возможностей устройства за счет возможности накопления локальных сумм последовательности чисел, выход дереноса (,j)-ой ячейки, где i = 1,п-1, j = 1,й 11, соединен с вторым входом

7359 4 (i+1,j+1)-ой ячейки, второй информационный вход (1,К)-ой ячейки, где

K = 1,п, подключен к К-ому разряду второго информационного входа сумматора, третий информационный вход (К,К)-ой ячейки, соединен с ее выходом суммы, а ее вход управления объединен с первым входом управления сумматора, второй вход управления сумматора соединен с вторым входом (2, 1)ой ячейки, выход суммы (n,К)-ой ячей— ки является К-ым разрядом выхода результата сумматора, тактирующие входы суммирующих ячеек соединены с TBKTH рующим входом сумматора.

2. Сумматор по п.1, о т л и ч а— ю шийся тем, что каж (ая (К,К)-ая

20 суммирующая ячейка содержит элемент

И, два тактируемых элемента памяти, одноразрядный сумматор, причем первый и второй информационные входы ячейки соединены с первым и вторым входами одноразрядного сумматора, третий вход которого соединен с выходом элемента

И, первый и второй входы которого соединены соответственно с входом управления ячейки, выход суммы и выход переноса которой соединены с выходами соответственно первого и второго тактируемых элементов памяти, информационные.входы которых соединены с выходами переноса и суммы соответственно, а актирующие их входы соединены с тактирующим входом ячейки. 1427359 Риг. 2

Выхо8перенпса Вью сутти

Составитель М.Есенина

Техред Л.Сердюкова Корректор В.Романенко

Редактор М.Товтин

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

l13035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4853/45

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4