Умножитель частоты

Иллюстрации

Показать всеРеферат

Изобретение отнбсится к радиотехнике и может использоваться для З множения частоты а аппаратуре приемо-передачи информащш и в системах передачи устр-в вычислительной тех- НИКИ. Цель изобретения - повышение точности умножения.. Умножитель частоты содержит два делителя частоты (ДЧ) 1,5, счетчик 2 реверсивный счетчик (РС) 3,. блок 4 сравнения, триггеры 6, элементы ИЛИ 8, 10, элементы И 9, П. С целью повышения точности умножения введены элемент И 12 и элемент ИЛИ 13. Изменение кода на выходах PC 3 вызывает соот ветствующее изменение выходной.час- TOTbi, Процесс изменения кода продолжается до момента прихода .на счет- Hbiii вход триггера 7 через элемент . ИЛИ iO импульса входной частоты fef. При поступленни импульса fg и импульса переполнения ДЧ 5 на вход г триггера 7 с другой последовательностью PC 3 переходит из режима сложения в режим вычитания, который задает триггер 6. Если импульсы совпадают хотя бы , то импульс совпадения, вьщеляющийся элементом И 12, через элемент ИЛИ 13 поступает на вход установки триггера 7 и устанавливает его в исходное состояние , т.е. код PC не изменится и выходная частота остается неизменной . 1. Ш1. О SS со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (sy -; Н 03 В 19(00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 4226184j24-09 (22) 08.04.87 (46) 30.09.88. Вюл. 11 36 (72) В.И. Тепляков и И.Ф. Тепляков (53) 621.373.42(088.8) . (56) Авторское свидетельство СССР

У !148088, кл. Н 03 В 19/00, 1982. (54) УМНОЖИТЕЛЬ ЧАСТОТЫ (57) Изобретение относится к радио-; технике и может использоваться для умножения частоты в аппаратуре приемо-передачи информации и в системах передачи устр-в вычислительной техники. Цель изобретения - повышение точности, умножения.. Умножитель частоты содержит два делителя частоты (ДЧ) 1,5, счетчик 2, реверсивный счетчик (PC) 3,. блок 4 сравнения, триггеры 6,7 элементы ИЛИ 8, 10, элементы И 9, 11. С целью повьппения точности умножения введены элемент.,Я1Л 1427552

И 1. и элемент И1И 13. Изменение кода на вьыадах РС 3 вызывает соот" ветствующее изменение выходной .частоты. Процесс изменения кода продолжается до момента прихода .на счетный вход триггера ? через элемент

ИПИ 10 импульса входной частоты Гщ.

При поступлении импульса щ и импульса переполнения ДЧ 5 на вход триггера 7 с другой последовательностью РС 3 переходит из режима сложения в режим вычитания, который задает триггер 6. Если импульсы совпадают хотя бы частично, то импульс совпадения, выделяющийся элементом

И 12, через элемент ИЛИ 13 посту" Я пает на вход установки триггера 7 и устанавливает его в исходное состояние, т.е. код РС не изменится и выходная частота остается неизменной. 1 ил.

1427552

Изобретение относится к радиотехнике и может быть использовано для умножения частоты в аппаратуре приемо-передачи информации и в системах передачи устройс. в вычислитель5 ной техники.

Цель изобретения — повьппение точности умножения.

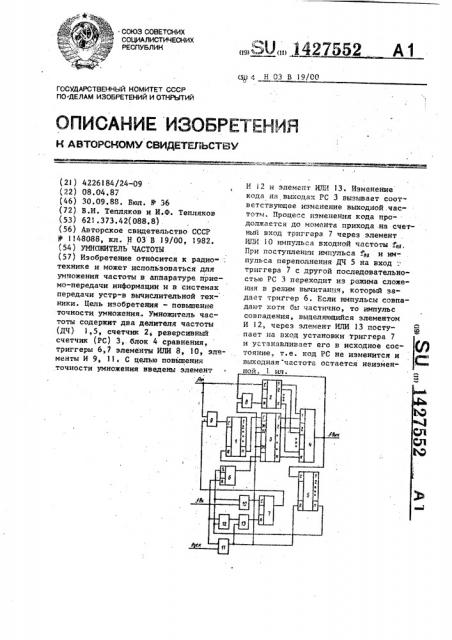

На чертеже представлена структур" 1 ная электрическая схема предложен.ного умножителя частоты.

Умножитель частоты содержит первый делитель I частоты, с .етчик 2, уеверсивный счетчик 3; блок 4 сравнения,, второй делитель 5 частоты, первый б и второй 7 триггеры, первый элемент ИЛИ 8, первый элемент

И 3, второй элемент ИШ4 1Î, второй

11 и третий 12 элементы И и третий 2 элемент ИЛИ 13.

Умножитель частоты работает сле1 дующим образом.

При подаче пускового сигнала на второй вход элемента И 11 сигнал 2 входной частоты Ге„ через элемент И устанавливает в начальное состояние счетчик 2, делитель I и 5 частоты, реверсивный счетчик 3 и через элемент ИЛИ 13 триггер 7. Сигнал опорной частоты Го„ поступает на счетный вход счетчика 2. При совпадении выходных кодов счетчика 2 и реверсивного счетчика 3 на выходе блока 4 сравнения появляется сигнал выходной частоты Яц„, который поступает на счетный вход делителя 5 частоты и через элемент ИЛИ 8 устанавливает в состояние "О" счетчик 2.

При переполнении делителя 5 частоты импульс переполнения с его выхода поступает через элемент ИЛИ 10 на вход триггера 7 и устанавливает его в единичное состояние, выходной сигнал через элемент И 9 разрешает поступление на вход делителя частоты

1 сигналов опорной частоты f Сигналы переполнения с выхода делителя 1 частоты поступают на счетный вход реверсивного счетчика 3. Ns-.;. енение кода на выходах реверсивного счетчика 3 вызывает соответствующее изменение выходной частоты. Процесс изменения кода продолжается до момента прихода на счетный вход триггера 7 через элемент ИЛИ !0 импульса входной частоты Га„

При поступлении импульса входной частоты и импульса переполнения делителя 5 частоты на вход триггера 7 в другой последовательности процесс изменения кода реверсивного счетчика 3 происходит аналогично, при этом счетчик 3 переходит из режима сложения в режим вычитания, который задает триггер б. Ксли эти импульсы совпадают хотя бы частично, то импульс совпадения, выделяющийся элементом И 12, через элемент ИЛИ 13 поступает на вход установки триггера

7 и устанавливает его в исходное состояние, т.е. код реверсивного счетчика 3 не изменяется и выходная частота остается неизменной.

Формула изобретения

Умножитель частоты, содержащий последовательно соединенные первый элемент ИЛИ и счетчик, поразрядные выходы которого соединены с соответствующими входами первой группы входов блока сравнения, последовательно соединенные первый элемент И, первый делитель частоты и реверсивный счетчик, поразрядные выходы которого соединены с соответствующимИ входами второй группы входов блока сравнения, второй элемент И, выход которого соединен с установочным входом второго делителя частоты, ус тановочным входом первого делителя частоты, группой установочных входов реверсивного счетчика и первым входом первого элемента ИЛИ, первый триггер, выход которого соединен с . управляющим входом реверсивного счетчика, второй элемент ИЛИ, выход ко" торого соединеч со счетным входом второго триггера„,выход которого соединен с первым входом первого элемента И, при этом выход второго делителя частоты соединен с вторым входом второго элемента .ИЛИ и вторым установочным входом первого триггера, первый вход второго элемента И соединен с первым входом второго элемента ИЛИ и первым установочным входом первого триггера, точка их соединения является сигнальным входом умножителя частоты, выход блока сравнения соединен с вторым входом первого элемента ИЛИ и счетным входом второго делителя частоты и является выходом умножителя частоты, счетный вход счетчика соединен с вторым входом первого элемента И, точка их соСоставитель Г. Захарченко

Редактор Л. Пчолинская Техред Л.Олийнык

Корректор С. Черни

Заказ 4864/54 Тираж 929

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 з 14 единения является входом опорной частоты умножителя частоты, а второй вход второго элемента И является входом пускового сигнала умножителя частоты, отличающийся тем, что, с целью повьппения точности умножения, в него. введены последовательно соединенные третий элемент И

27552

4 и третий элемент ИЛИ, выход которого соединен с установочным входом второго триггера, при этом второй вход

5 третьего элемента ИЛИ соединен с вы;.одом второго элемента И, а первый и второй входы третьего элемента И соединены соответственно с первым и вторым входами второго элемента ИЛИ.