Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к технике преобразования информации и может найти применение в информационноизмерительных системах, гибрвдных вычислительных комплексах, системах автоматического управления. Цель изобретения - повышение надежности за счет упрощения устройства. Устройство содержит два восьмиразрядных цифроаналоговых преобразователя, регистр последовательного приближения, постоянное запоминающее устройство, мультиплексор, сумматор, регистр и компаратор. Наличие дополнительного цифроаналогового преобразователя позволяет производить коррекцию старших разрядов основного цифроаналогового преобразователя, что существенно уменьшает объем цифровой части аналого-цифрового преобразователя. Сущность изобретения состоит в том, что в процессе кодирования формируется напряжение поправки, что обеспечивает высокую точность преобразователя , а аппяратная реализация алгоритма , кодирования - его высокое быстродействие . Компенсация ошибок старших разрядов первого цифроаналогового преобразователя производится аналого-цифровым способом на втором цифроаналоговом преобразователе. 1 з.п. ф-лы, 1 ил. 4; Ю сд О) 4

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1427564 А1 (50 4 Н 03 М 1/10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕККЫЙ КОМИТЕТ СССР

00 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3921110/24-24 (22) 02.07.85 (46) 30.09.88. Бюл., Ф 36 (71) Ленинградский электротехнический институт им. В.И.Ульянова (Ленина) (l2) А.А.Воротов и П.Б.Могнонов (53) 681.325 (088.8) (56) Зарубежная радиоэлектроника, 1984, N 2, с. 32-35, рис. 10.

Проблемы создания преобразователей формы информации. Материалы II

Всесоюзного симпозиума. Киев, 1973, с. 377-380. (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к технике преобразования информации и может найти применение в информационноизмерительных системах, гибридных вычислительных комплексах, системах автоматического управления. Цель изобретения — повышение надежности за счет упрощения устройства. Устройство содержит два восьмиразрядных цифроаналоговых преобразователя, регистр последовательного приближения, постоянное запоминающее устройство, мультиплексор, сумматор, регистр и компаратор. Наличие дополнительного цифроаналогового преобразователя позволяет производить коррекцию старших разрядов основного цифроаналогового преобразователя, что существенно уменьшает объем цифровой части аналого-цифрового преобразователя.

Сущность изобретения состоит в том, что в процессе кодирования формируется напряжение поправки, что обес- . печивает высокую точность преобразователя, а аппаратная реализация алгоритма, кодирования — его высокое быстродействие. Компенсация ошибок старших разрядов первого цифроаналогового преобразователя производится аналого-цифровым способом на втором цифроаналоговом преобразователе.

1 з.п. ф-лы, 1 ил.

1427564

Изобретение относится к преобразо" ванию информации и может найти применение в информационно-измерительных системах, гибридных вычислительных комплексах, системах автоматического управления.

Цель изобретения — повышение надежности за счет упрощения преобразователя. l0

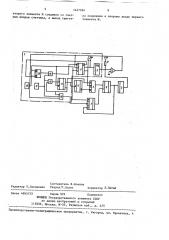

На чертеже приведена схема устройства.

Устройство содержит формирователь

1 компенсирующего напряжения, компаратор 2, первый цифроаналоговый преобразователь (ЦАП) 3, постоянное запоминающее устройство (ПЗУ) 4, мультиплексор 5, сумматор 6, регистр 7, токоограничнвающий элемент (резис— тор) 8, причем формирователь ком- 20 пенсирующего напряжения выполнен на втором цифроаналоговом преобразователе (ЦЛЛ) 9, двух генераторах тактовых импульсов (ГТИ) 10 и .11, триггере 12, счетчике 13, трех элементах 25

И 14-16, регистре 17 последовательного приближения (РПП).

Преобразователь работает следующим образом.

В ПЗУ 4 хранятся коды ошибок весо- 30 вых коэффициентов восьми старших разрядов.

Процесс преобразования происходит за 16 тактов по методу последовательного уравновешивания. На цифроаналоговый преобразователь (ЦАП) 9 загружается код восьми старших разрядов, а в первые восемь .тактов преобразования на ЦАП 3 — коды поправок, соответствующие кодам старших восьми разря 40 дов. В следующих восьми тактах на

ЦАП 3 загружается результирующий код, полученный как сумма кодов младших разрядов РПП 17 и сформированного кода поправки, соответствующий старшим разрядам РПП 17 и хранящийся в регистре 7, I

Отклонения весов разрядов от идеальных значений определяются после изготовления кристалла ЦАП и записываются в ПЗУ.

При поступлении импульса первого генератора тактовых импульсов ГТИ 10 происходит установка триггера 12 в единичное состояние, сброс в нулевое состояние счетчика 13 и регистра 7, запуск PIIII 17. Сигналом "0" с четвертого старшего разряда счетчика 13 происходит переключение мультиплексора 5 на второй канал и разрешение прохождения тактовых импульсов через второй 15 и третий 16 элементы И, а сигналом с прямого выхода триггера

12 разрешается прохождение тактовых импульсов через первый элемент И 14 на вход синхронизации РПП 17. В пер=вом такте преобразования по тактовому импульсу с выхода первого элемента И 14 при наличии сигнала ГТИ 10 устанавливается в единичное состояние старший разряд PIIII 17. Так как в первом такте сигналом ГТИ 10 блокируется импульс, поступающий с выхода второго элемента И 15 на счетный вход счетчика 13, то счетчик будет находиться в нулевом состоянии, а на первые входы сумматора 6 через второй канал мультиплексора 5 подается код ошибки старшего разряда, считанный из ПЗУ 4 по нулевому адресу.

Код поправки, полученный как сумма кода ошибки старшего разряда и кода с выхода регистра 7, который в пер" вом такте равен нулю, подается на цифровые входы ЦАП 3 ° В результате в первом такте в суммирующей точке первого входа компаратора 2 формируется аналоговый эквивалент, соответствующий весу старшего разряда и его поправки, который сравнивается со входным током. В зависимости от состояния компаратора 2 следующим тактовым импульсом, который поступает на вход синхронизации РПП 17, происходит сохранение или сброс единицы в старшем разряде РПП 17 и обязательный сдвиг этой единицы на один разряд в сторону младшего. Одновременно этот же тактовый импульс в зависимости от состояния компаратора 2 проходит на вход синхронизации регистра

7 через третий элемент И 16. При со1 хранении единицы в текущем разряде

РПП 17 в регистре 7 записывается код поправки с выхода сумматора 6, соответствующий коду РПП. Таким образом в регистре 7 сохраняется код поправки, соответствующий коду РПП, полученного в предыдущих тактах. В результате в каждом такте преобразования в суммирующей точке первого входа компаратора 2 формируется аналоговый эквивалент, соответствующий коду старших восьми разрядов РПП и его поправки. В девятом такте при появлении сигнала "1" в старшем разряде счетчика 13 происходит переклю

1427564

Формула изобретения 40

1. Аналого-цифровой преобразователь, содержащий компаратор, первый вход которого подключен к первому выходу формирователя компенсирующего напряжения и выходу цифроаналогового преобразователя, а выход соединен с управляющим входом формирователя компенсирующего напряжения, второй выход которого соединен с входом постоянного запоминающего устройства, отличающийся тем, что, с целью повышения надежности за счет упрощения преобразователя, в него введены мультиплексор, сумматор, регистр .и токоограничивающий элемент, вход которого является входной шиной, а выход соединен с первым входом компаратора, второй вход которого

55 чение мультиплексора 5 на второй канал, блокировка счетных импульсов счетчика 13 и прохождения синхросигналов в регистр 7 через третий эле- i .5 мент И 16. Код младших .разрядов РПП через первый канал мультиплексора 5 поступает на первые входы сумматора

6 и складывается с кодовои поправкой, зафиксированной в регистре 7 и соответствующей сформированному коду старших разрядов Р1П1. Результирующий код подается на ЦАП 3. Таким образом в девятом такте в суммирующей точке первого входа компаратора 2 формиру- 15 ется аналоговый эквивалент, соответствующий коду старших разрядов

РПП, и сумма кодов младших разрядов

РПП и поправки, который сравнивается со входным током. В последующие . 2p такты процесс уравновешивания происходит аналогично. По окончании урав новешивания импульс "Конец преобразования" РПП 17, поступающий на вход сброса триггера 12, сбрасывает его 25 и блокируется поступление тактовых импульсов на сход синхронизации PIU!

17. В результате на выходе РПП полу чается преобразованный код входного тока. 30

По приходу следующего импульса ГТИ описанный процесс повторяется.

Шкала ЦА11 3 выбирается -равной 17. от диапазона ЦАП 9 с учетом перекрытия его погрешностей. Общая точность аналого-цифрового преобразователя равна 0,005Х что соответствует 14 двоичным разрядам. подключен к общей шине, причем управляющий вход мультиплексора соединен с третьим выходом формирователя компенсирующего напряжения, четвертый выход которого подключен к первому информационному входу мультиплексора, второй информационный вход которого соединен с выходом постоянного запоминающего устройства, а выход — с первым входом сумматора, второй вход которого подключен к выходу регистра, вход сброса и вход синхронизации которого соединены соответственно с пятым и шестым выходами формирователя компенсирующего напряжения, а информационный вход объединен с входом цифроаналогового преобразователя и подключен к выходу сумматора.

2. Преобразователь по п. 1, о т— л и ч а ю шийся тем, что формирователь компенсирующего напряжения выполнен на цифроаналоговом преобразователе, -двух генераторах тактовых импульсов, триггере, счетчике, трех элементах И и регистре последовательного приближения, выход конец преобразования которого соединен с входом сброса триггера, вход синхронизации— с выходом первого элемента И, информационный вход является управляющим входом формирователя, вход запуска объединен с вход; м сброса счетчика, входом установти триггера, является пятым выходом .+,ормирователя и подключен к выхору первого генератора тактовых импульсов, выход старших разрядов — с входом цифроаналогового преобразователя, выход которого является первым выходом формирователя, выход младших разрядов регистра последовательных приближений является четвертым выходом форггирователя, вторым выходом которого янляется первый выход счетчика, второй выход которого соединен с первыми входами .второго и .третьего элементов И и является третьим выходом формирователя, шестым выходом кото-. рого является выход третьего элемента И, второй вход которого объединен с первым входом первого и вторым входом второго элементов И и подключен к выходу BToporo генератора тактовых импульсов, а третий вход третьего элемента И является управляющим входом формирователя, выход

1427564 второго элемента И соединен со счетным входом счетчика, а выход тригге ра подключен к второму входу первого элемента И.

Составитель Н.Козлов

Редактор Т.Лазоренко Техред ").Д дьк Корректор Л.Патаи

Заказ 4865/55 Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035-, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4