Преобразователь частота-код

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и автоматике, может быть использовано в цифровых системах управления для преобразования в циф ровой код сигналов частотных датчиков и является дополнительным к основному авт. св. № 970681. Изобретение позволяет повысить быстродействие и расширить область использования преобразователя . Для этого в преобразователь , содержащий блок 1 антисовпадений , кварцевый генератор 2, частотньй компаратор 3, регистр 4 памяти, реверсивный счетчик 5, преобразователь 6 код - частота, введены регистр 7.адреса, мультиплексор 8, формирователь 9 импульсов, преобразователь 10 период - код и формирователь 11 обратно1 о кода, что позволило быстро получагь грубую оценку измеряемой частоты с последующим устранением рассогласования между полученным и истинным значениями измеряемой частоты , а также применять преобразователь Q в многоканальных системах измерения частотных сигналов, в которых при переключении кььапов значение измеряемой частоты именяется скачкообразно . 1 з.п. ф-лы, 3 ил. S (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А2

„„SU„„1427571 (51)4 Н 03 И 1/60

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHGMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫИ НОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 97068 1 (21) 4219012/24-24 (22) 30.03.87 (46) 30.09.88. Бюл. Р- 36 (71) Уфимский авиационный институт им. Серго Орджоникидзе (72) А.И.Иванов, Д.Ю.Бухвостов, А.Н.Печенкин и С.И.Яковлев (53) 681.325.3(088.8) (56) Авторское свидетельство СССР

У 970681, кл. Н 03 М 1/60, 1 981. (54) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТА — КОД (57) Изобретение относится к вычислительной технике и автоматике, может быть использовано в цифровых системах управления для преобразования в цифровой код сигналов частотных датчиков и является дополнительным к основному авт. св. !! - 970681. Изобретение позволяет повысить быстродействие и расширить область использования преобразователя. Пля этого в преобраэо" ватель, содержащий блок 1 антисовпадений, кварцевый генератор 2, частотный компаратор 3, регистр 4 памяти, реверсивный счетчик 5, преобразователь 6 код — частота, введены регистр

7, адреса, мультиплексор 8, формирователь 9 импульсов, преобразователь

10 период — код и формирователь обратного кода, что позволило быстро получагь rpубую оценку измеряемой частоты с последукщим устранением рассогласования между полученным и истинным значениями измеряемой частоты, а также применять преобразователь д в многоканальных истемах измерения частотных сигналов. в которых при переключении каналов значение измеряемой частоты v.-.ìåíÿåòñÿ скачкообраэ- ( но. 1 э.п. ф-лы, 3 ил.

1427571

Изобретение относится к вычислительной технике и автоматике, может быть использовано в цифровых системах управления для преобразования в циф5 ровой код сигналов частотных датчиков и является дополнительным к изобретению по авт. св. N -970681.

Цель изобретения — повышение быстродействия и расширение области использования за счет возможности предварительного получения грубой оценки измеряемой частоты.

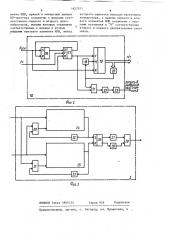

На фиг. 1 представлена структурная схема предлагаемого преобразователя, на фиг, 2 и 3 — схемы соответственно преобразователя период — код и частотного компаратора.

Преобразователь (фиг.1) содержит блок 1 антисовпадений,кварцевый генера- 0 тор 2,частотный компаратор З,регистр 4 памяти, реверсивный счетчик 5, преобразователь 6 код — частота, регистр

7 адреса, мультиплексор 8, формирователь 9 импульсов, преобразователь 10 период — код, формирователь 11 обратного кода, шину 12 "Запуск", адресную шину 13, входную шину 14 и выходную шину 15.

Преобразователь период — код (фиг ° 2) образуют RS-триггер 16, Dтриггер 17, генератор 18, счетчик 19, элемент И 20, элемент ИЛИ 21, элемент 2? задержки и одновибратор 23.

Частотный компаратор (фиг. 3) включает двухразрядные счетчики 24 35 и 25, RS òðèããåð 26, одновибраторы

27 и 28, элементы ИЛИ 29-31 и элементы 32 и 33 задержки.

Преобразователь работает следую40 щим образом.

Весь процесс получения кода частоты состоит из трех этапов: этап быстрого получения грубой ошибки измеряемой частоты, этап дослеживания и этап ,45 слеже ни я.

На этапе грубой оценки импульс на шине 12 осуществляет запись кода с шины 13 в регистр 7 адреса. При этом код адреса поступает на вход мультиплексора 8, коммутирующего в соответ— 50 ствии с ним один из входных сигналов с шины 14 через формирователь 9 импульсов на первый вход блока 1 антисовпадений и информационный вход преобразователя 10. После окончания 55 импульса запуска преобразователь 10 измеряет интервал времени между первым и вторым импульсами входной частоты f» следующим образом. Импульс запуска устанавливает в единицу триггер 16 и обнуляет счетчик 19 и триггер 17, Первый импульс Г„ устанавливает в единицу триггер 17, который сбрасывает триггер 16 и разрешает работу счетчика 19. Счетчик 19 заполняется импульсами частоты f генератора 18. Второй импульс fx сбрасывает триггер 17 и запрещает работу счетчика 19, Сигнал с инверсного выхода триггера 17 проходит через элемент ИЛИ 21, элемент 22 задержки и запускает одновибратор 23, импульс которого стробирует запись в счетчик

5, Элемент И 20 срабатывает при заполнении счетчика 19, при этом блокируется работа генератора 18, и через элемент ИЛИ 21 и элемент задержки

22 запускается одновибратор 23. Это необходимо для предотвращения переполнения счетчика 19. Код периода

N,. с выхода преобразователя 10 поступает на формирователь 11, который преобразует код периода N в код грубой оценки частоты :/, записываемый в старшие разряды реверсивного счетчика 5 по импульсу одновибратора 23. Элемент 22 задержки необходим для задержки импульса записи на время получения обратного кода в формирователе 11.

На этапе дослеживания устраняется рассогласование между истинным значением измеряемой частоты и грубой оценкой, полученной при измерении периода f . Преобразователь 6, представляющий собой триггерный делитель частоты, управляемый кодом счетчика

5, формирует из частоты f,. кварцевого генератора 2 сигнал компенсирующей частоты f„, соответствующий коду в счетчике 5 в каждый момент времени.

Частоты f> и Гк подаются на входы блока 1, который осуществляет их привязку к двум синхронизирующим несовпадающим последовательностям — сигналам с прямого и инверсного выходов генератора 2. С выходов блока 1 импульсы f» и f поступают соответственно на суммирующий и вычитающий входы счетчика 5 ° При этом направление и скорость изменения кода в счетчике определяются разностью частот

fi — f . Например, если f > к, код в счетчике 5 увеличивается, при этом частота f будет возрастать вплоть до момента f = f, . С выход» блока 1

1427571 импульсы 1: „и f подаются также на входы частотного компаратора 3, который пред ызначен для фиксации моментов равенства этих частот. Счетчик

Ф 5

24 заполняется импульсами f». и сбрасывается через элемент ИЛИ 30 импульсами f„. Если f. > f», то будут иметь место случаи, когда между двумя импульсами f„áóä÷T располагаться не менее двух импульсов f,, при этом на выходе элемента И 38 будет появляться сигнал, подтверждающий соотношение f > . Счетчик 25 аналогичен счетчику 24, заполняется

Ф импульсами f<. и сбрасывается импульсами f „. Сигналы на выходе элемента

И 39 подтверждают соотношение f„(f„.

Триггер 26, устанавливаемый при в 1» а при Й» (f» В "0", 20 меняет свое состояние при смене в момент равенства этих частот. При этом запускается одновибратор 27 или

28, импульс с выхода которого через элемент ИЛИ 29 переписывает код час- 2 тоты Ng из счетчика 5 в регистр 4, На этапе слежения код в счетчике

5 отслеживает изменение входной частоты f». Информация в регистре 4 обновляется при каждом срабатывании частотного компаратора 3.

Выходной код Nw преобразователя

10 обратно пропорционален частоте входного сигнала:

35 где C 3 — операция округления до целого, 40 вЂ, частота генератора 18.

Значение f< выбирается следующим образом:

Ъ)

4 лчиц 2 где m — разрядность счетчика 19;

Г» чнй — минимальное значение измеряемой частоты.

Формирователь 11 обратного кода может быть реализован в виде ПЗУ ем50 костью 2 m-разрядных слов ° Каждому возможному значению кода Nj ставится в соответствие код грубой оценки частоты N(. Таблица кодирования ПЗУ может быть представлена формулой

Частота кварцевого генератора f„ выбирается равной максимальному зн чению измеряемой частоты f<м,с

Формула изобретения

1. Преобразователь частота — код поавт. св. 1970681, отлич аю шийся тем, что» с целью повыиаэс ния быстродействия и расширения области использования за счет возможности предварительного получения грубой оценки измеряемой частоты, в него введены преобразователь период— код, формирователь обратного кода, регистр адреса, мультиплексор и формирователь импульсов, причем последовательно соединенные мультиплексор и формирователь импульсов подключены между входной шиной устройства и первым входом блока антисовпадений, объединенным с информационным входом преобразователя период . — код, управляющий вход которого, объединен- ный с управляющим входом регистра адреса, является шиной Запуск преобразователя, выход соединен с входом записи реверсивного счетчика, а выходы группы соединены с соответствующими входами формирователя обратного кода, выходы которого соединены с соответствующими информационными входами реверсивного счетчика, информационные вход» регистра адреса являются адресной шиной преобразователя,,а выходы соединены с соответствующими адр"сными входами мультиплексора.

2. Преобразователь по п. 1, о т— л и ч а ю шийся тем, что частотный компаратор содержит два одновибратора, RS-триггер, три элемента

ИЛИ, два элемента задержки и два двухразрядных счетчика, счетные входы которых являются соответственно первым и вторым входами частотного компаратора и объединены с первыми входами соответственно первого и второго элементов ИЛИ, выход переполнения первого двухразряднога счетчика соединен с S-входом RS-триггера и через первый элемент задержки с вторым входом второго элемента ИЛИ, выход переполнения второго двухразря, ного счетчика соединен с R-входом триггера и через второй элемент задержки с вторым входом первого эле1427571 которого является выходом частотного компаратора, а выходы первого и второго элементов ИЛИ соединены с входами установки в "О" соответственно второго и первого двухразрядных счетчиков, BHHHIIH Заказ 4865/55 Тираж 929 Подписное

Произв-полигр. пр-тие, г. Ужгород, ул. Проектная, 4 мента ИЛИ, прямой и инверсный выходы

RS-триггера соединены с входами соответственно -первого и второго одновибраторов, выходы которых соединены

5 соответственно с первым и вторым входами третьего элемента ИЛИ, выход

1 иск 6 урсов

4М7юМ