Устройство приведения кодов фибоначчи к минимальной форме

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для приведения кодов избыточных систем счисления к минимальной форме. Целью изобретения является расширение области применения за счет приведения к минимальной форме кодов двоичной избыточной системы счисления . Устройство содержит блоки свертки , каждый из которых выходы 2 и 3, входы 4-15 и содержит триггер 16, элементы И 17-22, элементы ИЛИ 23-28. 1 з.п.ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 Н 03 M 13/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ б

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПОДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4013589/24-24 (22) 14.01.86 (46) 30.09.88. Бюл. У 36 (72) А.В.Ткаченко, В.В.Дудкин и О.П.Гриб (53) 681.3 (088.8) (56) Авторское свидетельство СССР

В 1019434, кл. Н 03 M 13/12 ° 1982. (54) УСТРОЙСТВО ПРИВЕДЕНИЯ КОДОВ ФИБОНАЧЧИ К МИНИМАЛЬНОЙ ФОРМЕ (57) Изобретение относится к вычисли„„SU„„1427577 А 1 тельной технике и может быть использовано для приведения кодов избыточных систем счисления к минимальной форме. Целью изобретения является расширение области применения за счет приведения к минимальной форме кодов двоичной избыточной системы счисления. Устройство содержит блоки свертки, каждый иэ которых имеЕт выходы

2 и 3, входы 4-15 и содержит триггер

16, элементы И 17-22, элементы ИЛИ

23-28. 1 з.п.ф-лы, 2 ил.

1427577

Изобретение относится к вычислительной технике и может быть использовано для приведения кодов избыточных систем счисления к минимальной форме °

Целью изобретения является расширение области применения за счет приведения к минимальной фбрме кодов двоичной избыточной системы счисления.

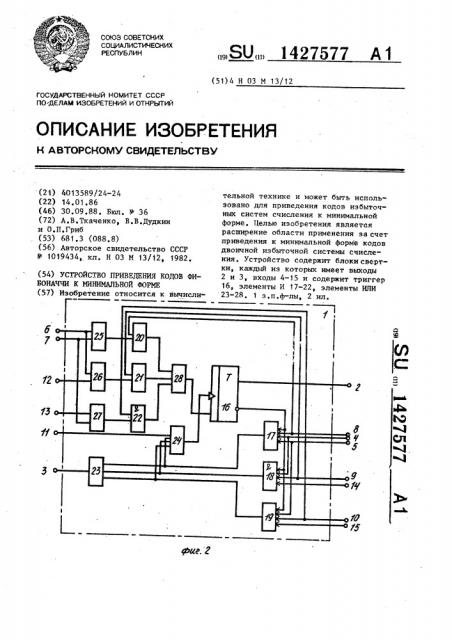

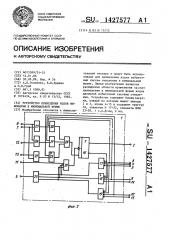

На фиг.1 приведена функциональная 10 схема устройства, на фиг.2 — схема блока свертки.

Устройство содержит блоки 1 свертки, каждый блок свертки имеет первый и второй выходы 2 и 3, первый — один-15 надцатый входы 4-15, каждый блок свертки — триггер 16, элементы И 1722, элементы ИЛИ 23-28.

Устройство работает следующим об разом. 20

В начальном состоянии триггеры 16 блоков обнулены. Входной код подается на входы 11 блоков 1, единичные информационные сигналы поступают через элементы ИЛИ 24 на счетные входы триггеров 16 соответствующих разрядов и переводят их в единичные состояния.

При подаче разрешающего сигнала на входы 8 блоков 1 осуществляется свертка кодов Фибоначчи. При этом с,помощью элемента И 17 в каждой группе из

30 трех смежных разрядов выделяются комбинации типа 110 и при наличии подобной комбинации на выходе элемента И 16 формируется единичньй сигнал, который, проходя через элемент ИЛИ 24, поступает на счетный вход триггера

16 и переводит его в единичное состояние. Этот же сигнал через элемент

ИЛИ 23 поступает на выход 3 блока и далее на входы 6 и 7 блоков 1 свертки младших разрядов, в которых он проходит через элементы ИЛИ 25, И 20, ИЛИ 28 и обнуляет триггер 16. В результате кодовая комбинация 110 в трех смежных разрядах переходит в ком-45 бинацию 001.

При приведении кодов в двоичной избыточной системе счисления разрешающие сигналы попеременно подаются на входы 9 и 10 блоков 1. В результа- 50 те этого с помощью элементов И 18 вы\ деляются кодовые комбинации, когда значение i-ro разряда .нулевое, а значения (i-1)-го и (i-5 )-ro разрядов единичные. С помощью элемента И 19 55 выделяются комбинации, когда значение

i-ro разряда нулевое, а значения (i-2)-го и (i-3)-ro разрядов единичные. Далее сигналы с выходов элементов И 18 и 19 через элемент ИЛИ 24 переводят триггер 16 i-ro разряда в единичное значение, а через элемент

И 23 блока 1 i-го разряда и элементы

ИЛИ 26, И 21 и ИЛИ 28 переводят триггеры 16 блоков 1 (i-1)-ro и (i-5) -ro разрядов в нулевое состояние. Обнуление триггеров 16 блоков 1 свертки (1. 2)-ro и (i-3)-го разрядов производится с помощью сигнала, поступающего на вход обнуления триггера 16 через элементы ИЛИ 27, И 22 и ИЛИ 28 блока 1 соответствующего разряда. Выходной код снимается с выходов 2 блоков 1.

Формула и э о б р е т е н и я

1. Устройство приведения кодов

Фибоначчи к минимальной форме, содержащее и блоков свертки (n — разрядность кода), первый выход i-го блока свертки (1=1,...,n) является i-м информационным выходом устройства и соединен с первым входом (i+1)-го блока свертки и вторым входом (i+2)-ro блока свертки, второй выход 1. го (1.=1, ...,n) блока свертки соединен с третьим входом (i-1)-го блока свертки и четвертым входом (i-2)-го блока свертки, объединенные пятые, шестые и седьмые входы блоков свертки являются соответственно первым, вторым и третьим управляющими входами устройства, восьмой вход каждого блока свертки является соответствующим информационным входом устройства, о т:.л и ч а ю щ е е с я тем, что, с целью расширения области применения sa счет приведения к минимальной форме кодов избыточной системы счисления, девятый вход (i-5)-го блока свертки объединен с дейятым входом (i-3)-ro блока свертки и подключен ко второму выходу 1-го блока свертки, одиннадцатый вход (i+5)-го и двенадцатый вход (i+3)-го блоков свертки подключены к первому выходу i-ro блока свертки.

2. Устройство по п.1, о т л ич а ю щ е е с я тем, что блок свертки содержит триггер, элементы И и элементы ИЛИ, пряяпй выход триггера ! подключен к первому выходу блока свертки, инверсный выход триггера подключен к объединенным первым входам первого, второго и третьего эле-.

1427577

Составитель О.Йеплохов

ТехРед М.Дидык

Корректор Л.Пилипенко

Редактор Н.Горват

Заказ 4865/55

Тираж 929 Подписное

ВНИИПИ Гасударственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная, 4 ментов И, вторые входы которых объединены с первыми входами соответственно четвертого, пятого и шестого элементов И и подключены соответственно к пятому, шестому -и седьмому входам блока свертки, третий и четвертый входы первого элемента И объединены с третьими входами соответственно второго и третьего элементов

И и подключены соответственно к первому и второму входам блока свертки, четвертые входы второго и третьего элементов И подключены соответственно к одиннадцатому и двенадцатому входам блока свертки, выходы первого, второго и третьего элементов И соединены соответственно с объединенными первыми, вторыми и третьими входами первого и второго элементов ИПИ, выход первого элемента ИЛИ подключен к второму выходу блока свертки, четвертый вход второго элемента ИЛИ под ключен к восьмому входу блока свертки, а выход — к счетному входу триггера, первый и.второй входы третьего элемента ИЛИ объединены с первыми входами соответственно четвертого и пятого элементов ИЛИ и подключены соответственно к третьему и четвертому входам блока свертки, вторые входы четвертого и пято"о элементов ИЛИ подключены соответственно к девятому и десятому входам блока свертки, выходы третьего — пятого элементов ИЛИ подключены к вторым входам соответственно четвертого — шестого элементов

И, выходы которых соединены с соответствующими входами шестого элемента ИЛИ, выход которого соединен с входом обнуления триггера,