Устройство для детектирования многочастотных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике передачи дискретной информации. Цель изобретения - повьшение помехоустойчивости за счет коррекции линейных искажений сигнала, В устр-во для достижения цели введены фазовый корректор 1, перемножители 2, 3 и второй запоминающий блок (ЗБ) 13. Входной многочастотный сигнал, пройдя через фазовый корректор 1, поступает на два перемножителя 2 и 3. Выходные сигналы перемножителей су 1мируются в сумматоре 4 и поступают на вход многоканального коррелятора 5, в котором осуществляется вычисление коэффициентов корреляции с синфазным и квадратурным опор сигналами всех частотных подканалов модема, включая н пилот-сигналы. В блоке 6 коэф.корреляции пересчитываются т. обр., чтобн устранить сдвиг фаз между несущими и опорными колебаниями. Анализатор 7 расстройки фазы, многоканальньй накопитель 3 иЗБ 13 формируют сигналы синуса и косинуса смещения фаз для кaж,oгo подканала, а анализатор 10 расстройки частоты совместно с ЗБ 3 формируют опорные сигналы на перемноу « жители 2 и 3, осуществляя коррекцию сдвига частоты в канапе св.язи, ф-лы, 2 ил. з.п. 2

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ люргИФЪЩ Г,Я

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н Д BTOPCHOMY СВИДЕТЕЛЬСТВУ (54) УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ

МНОГОЧАСТОТНЫХ СИГНАЛОВ (21) 4229539/24-09 (22) 13,04 ° 87 (46) 30,09,88, Бюл. Р 36 (72) В.А.Балашов, Ф.Г.Кишиневский, Ю.В.Король, П.Я.Нудельман, В.С.Скляр, Е.Л.Спиваковский и А.M.Òèìåñîâ (53) 621 396.61(088.8) (56) Авторское свидетельство СССР . Р 786047, кл.- Н 04 L 27/22, 1978. (57) Изобретение относится к технике передачи дискретной информации. Цель изобретения — повышение помехоустойчивости за счет коррекции линейных искажений сигнала. В устр-во для достижения цели введены фазовый корректор 1, перемножители 2, 3 и второй запоминающий блок (ЗБ) 13. Входной многочастотный сигнал, пройдя через

У 8

„„SU„„ l 427596 А1 фазовый корректор 1, поступает на два перемножителя 2 и 3. Выходные сигналы перемножителей суммируются в сумматоре 4 и поступают на вход многоканального коррелятора 5, в котором осуществляется вычисление коэффициентов корреляции с синфазным и квадратурным опорными сигналами всех частотных подканалов модема, включая и пилот-сигналы. В блоке 6 коэф.корреляции пересчитываются т. обр.„ чтоб устранить сдвиг фаз между несущимц и опорными колебаниями. Анализатор 7 расстройки фазы, многоканальный накопитель 8 и ЗБ 13 формируют сигналы с. синуса и косинуса смещения фаз „для о каждого подканала, а анализатор 10 расстройки частоты совмес-,.íî с ЗБ 13 формируют опорные сигналы на перемно- жители 2 и 3, осуществляя коррекцию сдвига частоты в канале связи, 1 з.п. ф-лы, 2 ил.

1427596

Изобретение относится к технике передачи дискретной информации и может быть использовано в многочастотных устройствах преобразования сигналов (модемах) с амплитудно-фазовой

:модуляцией (АФМ), Цель изобретения — повышение помехоустойчивости за счет коррекции линейных искажений сигнала, 10

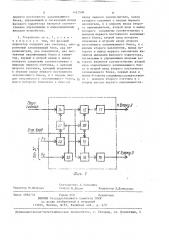

Ня фиг. 1 предстанлена структурная электрическая схема предлагаемо4 го устройства; на фиг. 2 — вариант выполнения фаз4вого корректора.

Устройство для детектирования многочастотных сигналов содержит .(фиг. 1) фазовый корректор 1, первый и второй перемножители 2 и 3, сумматор 4, многоканальный коррелятор

5, блок 6 вычисления разности фаз, 20 анализатор 7 расстройки фаз, многоканальный накопитель 8, декодер 9, анализатор 10 рясстройки частоты, .первый запоминаюший блок 11, распре- делитель 12 тактовых импульсов и нто- 25 рой запоминающий блок (ПЗУ) 13.

Фазовый корректор 1 содержит (фиг. 2) оперативный запоминающий блок (ОЗУ) 14, первый и второй перемножители 15 и 16, первый и второй 30 накопители 17 и 18, первый и второй постоянные запоминающие блоки (ПЗУ)

19 и 20, сумматор 2 1, первый и второй счетчики 22 и 23, Устройство работает следующим об. разом.

Входной цифровой сигнал (фиг. 1)

S(n c), где с = 1/F — интервал диск2 ретизации, F — частота дискретизации, n = О, 1, 2, ... — текущий но- 40 мер отсчета, последовательно запоминается в оперативном запоминающем блоке (ОЗУ) 14 фазового корректора

1 (фиг, 2). Запись осуществляется по адресам, задаваемым первым счетчи- 45 ком 22. Разрядность первого и второго счетчиков 22 и 23, число ячеек

ОЗУ 14 определяется длиной импульсной реакции фазового корректора 1, которую в дальнейшеM для упрощения

50 называют корректирующим сигналом.

Для определенности полагаем число отсчетов корректирующего сигнала равным N.

Отсчеты группового сигнала считываются из ОЗУ 14 с тактовой частотой

ИР, т.е. на каждом такте дискретизации (на интервале времени между двумя тактами записи н ОЗУ 14) из него считываются все N отсчетов. н последовательности, задаваемой вторым счетчиком 23. Суммирование двоичных сигналов с выходов первого и второго счетчиков 22 и 23 н сумматоре 21 обеспечивает смещение адреса ячейки записи и начала считывания, Считанные с частотой Fz из ОЗУ 14 N отсчетов группового, сигнала S(п ) последовательно поступают на входы первого и второго перемножителей 15 и 16, Ня вторые входы первого и второго перемножителей 15 и 16 из первого и второго постоянных запоминающих блокон (ПЗУ) 19 и 20 синхронно поступают N отсчетов соответствующего варианта корректирующего сигнала. Во втором ПЗУ 20 хранятся отсчеты M вариантон корректирующих сигналов, а н первом ПЗУ 19 — столько же вариантов соответствующих сигналов, преобразованных по Гильберту. Корректирующие сигналы из них извлекаются синхронно.

Корректирующие сигналы рассчитываются на этапе проектирования .по известной методике.

Каждый вариант корректирующего сигналя представлен N отсчетами, амплитуды которых записаны числами в двоичном предстянлении.. Адресация ячеек первого и второго ПЗУ 19 и 20 выбрана таким образом, что старшие двоичные разряды числа М определяют номер варианта корректирующего сигнала, а j младших разрядов (где N = 2) задают номер отсчета. В результате этого синхронная работа ОЗУ 14 и

ПЗУ 19 и 20 достигается тем, что адресация их ячеек осуществляется одним и тем же вторым счетчиком 23.

Значения старших разрядов адреса первого и второго ПЗУ 19 и 20 задают с помощью внешнего сигнала. в зависимости от требуемого шаблона.

Результаты перемножений отсчетов входного сигнала и корректирующих на каждом тактовом интервале суммируются н первом и втором накопителях

17 и 18. В дальнейшем сигналом F состояние второго счетчика 23 изменяется на единицу. В результате очередной отсчет входного сигнала S(nc)

-записывается в ячейку ОЗУ 14 с новым адресом. Затем вновь считываются все N отсчетов из ОЗУ. 14 в порядке, смещенном на единицу относительно предыдущего цикла, и весь описан1427596

J0!

25

50

55 ный цикл работы фазового корректора 1 повторяется. Сигналы S„(nI,) и

S„,(n<) с выходов первого и второго накопителей 17 и 18 фазового корректора 1 поступают соответственно на первые входы первого и второго перемножителей 2 и 3 (фиг. 1), в которых последовательно перемножаются с отсчетом цифровых сигналов slngt u

cosset, считываемых из ПЗУ 13 второго запоминающего блока в соответствии с сигналом управления анализатора 10 расстройки частоты, Выходные сигналы перемножителей суммируются в сумматоре 4 и поступают на вход многоканального коррелятора 5, в котором осуществляется вычисление коэффициентов корреляции с синфазным и квадратурным опорными сигналами всех частотных подканалов модема, включая и пилот-сигналы:

М+Н

Х„= Б(п) sin63n7. (1)

ne No

No+8

У = + S(n<.) cosa„at.

@=N<

Затем в блоке 6 вычисления разности фаз коэффициенты корреляции пересчитываются таким образом, чтобы устранить сдвиг фаз между несущими и опорными колебаниями:

Х = X„cos g„— Y sin (p„(2) Y Х з1пц + Y coscp к

Пересчитанные проекции Х „и Y q поступают на входы анализатора 7 расстройки фазы, где для каждого подканала производится вычисление расстройки фаз

sin сук = X„Y„+ Y„X„,, (3)

I где Х к и Y „о — координаты принятого ко сигнала после принятия решения.

Полученные значения sin ср„ усредняются в многоканальном накопителе 8 и поступают на первый запоминающий блок 11, задавая адрес ячеек, в которых записаны отсчеты функций sin y и cosy, На вход анализатора 10 расстройки частоты поступает сигнал проекции пилот-сигнала на квадратурную ось, который пропорционален величине набега фазы пилот-сигнала относительно опорного сигнала за время длительности посылки. Усредненное в анализаторе 10 значение этого сигнала поступает в качестве адреса на нходь. второго запоминающего блока 13, В соответствии с этими адреса п1 и него на каждой посылке изьлекаются отсчеты функций sin g и созс1, которые поступают на соответствующие входы первого и второго перемножителей 2 и 3, осуществляя коррекцию сдвига частоты в канале связи„

Формула изобретения

1. Устройство для детектирования многочастотных сигналов, содержащее сумматор и многоканальный коррелятор, тактовые входы и вы..одь: .:от..:.:— го соединены соотнетстьенно .- с. -,-1=,1 ми выходами распределится..: —:I! -I, .;-, импульсов и с информацка.- .-.;-.:. ми блока вычисле .ия р з з пoc т:.,:,-а э . выходы которого подключень, .< --. ..=да. 1. декодера, выхоп которс.: .: ". =.ëse-".: выходом устрои;-.тва, к входам:;:.a"I

Выходы I-.юс ми входами блока вычисления разнс.:;; фаз, а вход распределителя тактовых импульсов является тактовым Bxcäñì устройства, о т л и а ю щ е е с я тем, что, с целью повышения пс.мехоустойчивости за сче-. коррекции ли-нейных искажений сигн=-ла. вве, -="-ны два перемножителя, второй заппы =н"-=." -.IíÃ:: блок и фазовьп1 корректор- зыхогы которого подключены к первым входам гер- ного и втор ого пер емножителей,. вторые входы и выходы которых coe,".;-.".,.ены соответственно с выходами второго запоминающего блока, к входу которо=

ro подключен выход анализатора расстройки частоты, и с входами с,ъ aòo" ра, выход которого подключен к ин оормационному входу многоканального коррелятора, причем выход многоканаль.ного накопителя соединен с входом

1427596 (Дц (;

Составитель А, Москевич

Техреду М,Дидык Корректор Э.Лончакона

Редактор M.Петрова

Заказ 4866/56

Тираж 660 Подписное

БНК111И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35„ Раушская наб,, д, 4/5

Производственно-пслиграфическое предприятие, г, Ужгород, ул. Проектная, 4 первого постоянного запоминающего блока, упранляющий и сигнальный входы фазового корректора являются соотнетСтвенно управляющим и информационным входами устройства.

2, Устройство о п. 1, о т л и— ,ч а ю щ е. е с я тем, что фазовый

Корректор содержит дна счетчика, опе- 10 ративный запоминающий блок, два перемножителя, дна накопителя, два постоянных запоминающих блока и сумматор, первый и второй входы и выход которого соединены соответственно с ныходом первого счетчика, с выходом второго счетчика, который подключен к первому входу первого постоянного запоминающего блока, и с первым входом оперативного запоминающего iïîêà, ньгход которого подключен к первому входу первого перемножителя, выход которого соединен с входом первого накопителя, и к первому входу второго перемножителя, второй вход и выход которого соединены соответственно с ныходом первого постоянного запоминающего блока, второй вход которого подключен к второму входу второго постоянного запоминающего блока, и с входом второго накопителя-, выход которого и выход первого накопителя являются вьгходами фазонorо корректора, сигнальным и управляющим входами которого являются соответственно второй нход оперативного запоминающего блока и второй вход второго постоянного запоминающего блока, первый вход и выход которого соединены соответственно с выходом второго счетчика и с вторым входом первого перемножителя.