Устройство для деления чисел

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1 ц 4 G Об F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3869848/24-24 (22) 18.03.85 (46) 07.10 ° 88. Бил. Y 37 (71) Иинский радиотехнический институт (7?) А.Г.Батвков и А.А.Шостак (53) 681.325 (088.8) (56) Патент С01А Р 3234367, кл. 235156, опублик. 1962.

Патент СИА Р 3293418, кл. 235-156, опублик. 1964.

Авторское свидетельство СССР

Ф 1247862, кл. G 06 F 7/52, 07,01,85, (54)(57) уСтРОЙСТБ0 gJ18 pFtIF}IHH 111СБП, содержащее первый и второй регистры . остатка, регистр делителя, регистр частного, блок деления усеченных чисел, содержащий сумматор принудительного округления делителя, первый и второй вычитатели, первый и второй узлы деления и коммутатор, блок умножения, первый, второй и третий вычитатели, первый коммутатор, узел коррекции частного и блок управления, причем вход данных устройства соединен с информационными входами регистра делителя и с информационными входами первой группы первого коммутатора,-информационные входы второй группы которого соединены с выходами разности первого вычитателя, выходы первого коммутатора соединены с информационными входами первого регистра остатка, информационные входы второго регистра остатка соединены с выходами займа первого вычитателя, вьмоды старших разрядов регистра делителя соединены с входами сумматора принудительного округления делителя блока деления усеченньж чисел, вход переноса сумматора принудительного округления делителя блока деления усеченных чисел подклвчен к шине логической единицы, а выходы соединены с входами делителя первого и второго узлов деления блока деления усеченных чисел, входы делимого которых соединены с выходами первого и второго вычитателей блока деления усеченных чисел соответственно, входы уменьщаемого первого и второго вычитателей блока деления усеченных чисел соединены с выходами старших разрядов первого регистра остатка, а входы вычитаемого первого и второго вычитателей блока деления усеченных чисел соединеHEI с выходами старших разрядов второго регистра остатка, входы займа пер" ного н аторого нычнтателец Олена де- ления усеченных чисел подклвчены к шинам логнческой единицы н нуда соотнет- )С ственно, выходы первого и второго уз:— лов деления блока деления усеченньж чисел соединены с информационными входами первой и второй групп коммутатора блока деления усеченных чисел соответственно, выход заема в старшие © разряды второго вычитателя соединен с управлявщим входом коммутатора блока деления усеченных чисел, выходы разрядов которого, эа исключением выхода старшего разряда, соединены с информационными входами первой группы узла коррекции частного и с входами первой группы блока умножения, информационные входы второй группы узла коррекции частного соединены с выходами младших разрядов регистра частного, выходы узла коррекции частного соединены с информационными входами младших разрядов регистра частного, вьмоды разрядов которого

14?9109 соединены с выходами частного устройства, выходи разрядов первого регист раа остатка соединены с входами умень шаемого второго внчитателя, входы

:вычитаемого которого соединены с выходами разрядов второго регистра остатка, выходы разности второго вычитателя соединены с входами уменьшяемого третьего внчитятеля и соединены с выходами остатка устройства, выходы разрядов регистра делителя соединены

) с входами вычитаемого третьего вычи тателя и входами второй группы блока умноже ни я, в ых оды пе рв ой! и в то рой групп которого соединены с входами

,вычитаемого первой и в торой групп ! первого вычитателя соответственно, вход синхронизации устройства соединен с синхровходями регистра частного, первого и второго регистров остатка и с первым входом блока управления,,второй вход которого соединен с пер1 вым управляищим входом узла коррек ции частного и с выходом заема старше го разряда третьего вычитятеля, третий вход блока управления соединен с выходом старшего разряда коммутатора блока деления усеченных чисел, первый выход блока управления соедиИзобретение относится к ннчислиТельной технике и может бить применеНо в арифметических устройствах для выполнения операции деления чисел.

Цель изобретения — сокращение ко- 5 личества оборудования.

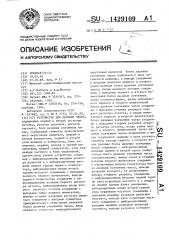

На чертеже представлена схема устройства для деления чисел.

Устройство содержит первый регистр

1 остатка, второй регистр, 2 остатка, регистры 3 и 4 делителя и частного, блок 5 деления усеченных чисел, сумматор 6 принудительного округления делителя блока 5, первый и второй вычитатели 7 и 8 блока 5, первый и второй уэлн 9 и 10 деления блока 5, коммутатор 11 блока 5, блок 12 умножения, первнй, второй и третий внчитатели 1315, первый и второй коммутаторы.lб и

17, узел )8 коррекции частного, блок

19 управления, входы 20 и 21 данных и синхронизации, выходы 22 и ?3 остатка нен с синхровходом регистра делителя и с входом установки в нуль первого регистра остатка,второй, третий и четвертый выходы блока управления соединены с первым, вторым и третьим управлявщими входами первого коммутатора соответственно, пятый выход блока управления является выходом сигнализации окончания деления, шестой выход блока управления соединен с входом установки в нуль второго регистра остатка, седьмой выход блока управления соединен с вторим управляющим входом узла коррекции частного, о т л и ч я и щ е е с я тем, что, с цельв сокращения количества оборудования, устройство содержит второй коммутатор, информационные входи первой группы которого соединени с выходами остатка устройства, ипформацноннне входи второй группы соединены с выходами разности третьего вичитятеля, выходы второго коммутатора соединены с входами уменьшяемого первого вичитятеля и с информационными входами третьей группы первого коммутатора, упрявляищий вход второго коммутатора соединен с выходом заема старшего разряда третьего внчитятеля. и частного, шинн 24 и 25, логической единицы и логического нуля, выходы 26 разрядов регистра 1, выходи 27 старших разрядов регистра 1, выходи 28 разрядов регистра 2, выходи 29 старших разрядов регистра 2, выходи 30 разрядов регистра 3, виходи 31 старших разрядов регистра 3, выходи 32 коммутатора ll виходы 33 коммутатора ll эа искличением старшего разряда, выход 34 старшего разряда коммутатора 11, выходи 35 разности вычитателя 14, выход 36 заема н старшие разряди вычитателя 14, выход 37 заема старшего разряда внчитятеля 15, выходы 38 разности вичитателя 15, выходи

39 разрядов коммутатора 17, выходи

40 и 41 первой и второй групп блока

1?, выходи 42 и 43 разности и заема вичитятеля 13, выходи 44 4млядших разрядов регистра 4, выходи 45 узля 18, выходи 46-51 блока )9.

I 4 29

Выходы разрядов 26 первого регистра 1 остатка соединены с входами уменьшаемого второго нкчитателя 14, входы нкчитаемого которого соединены

5 с выходами разрядов ?8 второго регистра ? остатка, выходы 35 разности второго нкчитателя 14 соединены с входами уменьнаемого третьего вычитателя 15, с информационными входами первой группы второго коммутатора 17 и являются выходами 22 остатка устройства, выходы 30 разрядов регистра делителя 3 соединены с входами вкчитаемого третьего вычитателя 15 и с входами второй группы блока 12 умножения, выходы 40 и 41 первой и второй групп блока 12 умно ения соединены с входами вычитаемого первой и второй групп первого вычитателя 13 соответственно, выходы 35 разности третьего вычитателя 15 соединены с входами второй группы второго коммутатора 17, выходы 39 второго коммутатора 17 соединены с входами уменьшаемого перво- 26 го вычитателя 13 и с информационными входами третьей группы первого коммутатора 16, вход 20 данных устройства соединен с информационными входами регистра делителя 3 и с информационными входами первой группы первого коммутатора 16, информационные входы второй группы которого соединены с выходами 42 разности первого вычитателя 13, выходы первого коммута35 тора 16 соединены с информационными входами первого регистра 1 остатка, информационные входы второго регистра 2 остатка соединены с выходами 43 займа первого вычитателя 13, выходы 4О

31 старших разрядов регистра 3 делителя соединены с входами сумматора

6 принудительного округления делителя блока 5 деления усеченных чисел, вход переноса сумматора принудитель45 ного округления делителя 6 блока 5 подключен к шине 24 логической единицы, а-выходы соединены с входами делителя первого и второго узлов 9 и

10 деления блока 5, входы делимого

50 которых соединены с выходами первого и второго вкчитателей 7 и 8 блока 5 соответственно, входы уменьшаемого первого и второго вычитателей 7 и 8 блока 5 соединены с выходами 27 старших разрядов первого регистра 1 остатка, их входи вычитаемого соединены с выходами 29 старших разрядов второго регистра 2 остатка, входы

09 зай.-а первого и pòîðëãо pê÷; òàòåëåé

7 и Я блока 5 пар ключенк к шинам 24 и 25 логической единицы и нуля соответственно, выходы первого и второго узлов 9 и 10 деления блока 5 соединены с информационнкми входами первой и нторой групп коммутатора II блока

5 соответственно, выход займа в старшие разряды 36 второго вкчитателя 14 соединен с управляющим входом коммутатора 11 блока 5, вкходы 33 которого,за исключением старшегo разряда, соединены с информационными входами первой группы блока 12 умножения и с информационными входами первой группы узла 18 коррекции частного, <=.íËîðèàöèoHíêå входы второй группы которого соединены с выходами 44 младших разрядов регистра 4 частного, выходи 45 узла коррекции частного соединены с информационными входами младших разрядон регистра 4 частного, выходы разрядов которого являются выходом 23 частного устройства, вход

21 синхронизации у тройстна соединен с синхровходом регистра 4 частного, первого и второго регистров 1 и 2 остатка и с первым входом блока 19 управления, второй нход которого соединен с первым управляющим входом узла

18 коррекции частного, управляющим входом второго коммутатора 17 и с выходом 37 займа старшего разряда третьего вычитателя 15, третий вход блока 10 управления соединен с выходом старнего разряда 34 коммутатора 11 блока

5, перва выход 46 блока 19 управления соединей с синхровходом регистра делителя 3 и с входом установки в нуль первого регистра l остатка, второй, третий и четвертый выходы 4850 блока 19 управления соединены с первым, вторым и третьим управляющими входами первого коммутатора 16 соответственно, пятый выход блока 19 управления является выходом сигнали" зации окончания деления устройства, шестой выход 47 блока 19 управления соединен с входом установки в нуль второго регистра 2 остатка, седьмой выход 51 блока 19 управления соединен с вторым управляющим входом узла 18 коррекции частного.

Первый регистр 1 остатка (и+1)разрядный, из которых один разряд расположен слева от занятой и п разрядов справа от занятой. В исходном состоянии в этом регистре хранится и-раз!

429!09 рядный двоичный код делимого без знака, а в процессе деления в него записываются значения разности очеред1 алых остатков, формируемых в устройстве в двухрядном коде (в виде двух чисел. первое число является разностью остатка, а второе — его займом). Второй регистр 2 остатка содержит и раз ядов, на которых один расположен сле- 0 а от занятой, а (п-1)-- справа. В сходном состоянии этот регистр обнуен, Регистры 3 и 4 делителя и частнооп-разрядные, причем в регистре 3 елителя все разряды расположены cnpa- а от занятой, а в регистре 4 частноо один разряд находится слева от анятой, а (n-1) разрядов — справа т занятой. В регистре 3 делителя в сходном состоянии хранится и-разряд- 2

ый двоичный код делителя беэ знака, егистр 4 частного в исходном остоянии не обнуляется. Разрядность казанных регистров и расположенные в них информации могут быть и несколько иными, Регистры 1 - 4 построеHbI на основе двухтактных синхронных

D-триггеров с асинхронными установочными входами. Регистр 4 частного имеет цепи однотактного сдвига влево на (К-.1) разрядов.

Блок 5 деления усеченных (малоразрядных) чисел предназначен для формирования по значению определенного числа старних разрядов делителя и остатка К цифр частного с точностью до единицы их младнего разряда, Все узлы блока 5 комбинационного типа. В сумматоре 6 осуществляется принудительное округление делителя путем прибавления к значению его старних разрядов, поступающих на входы сумматора 6 с выходов 31 регистра 3 делителя единицы в их младший разряд (сргнал логической единицы постоянно подается на вход переноса сумматора 6

15 с шины 24 устройства), На выходе сумматора 6 образуется значение старших разрядов делителя, увеличенное на единицу. Этим самым устраняется возможность получения на выходах 32 блока 5 из-за отбрасывания младних разрядов делителя значения К цифр частного с избытком. Но так как в блоке S при формировании К цифр частного используются старшие разряды не- 5 приведенного остатка (представленного в двухрядном коде), то становится возможным образование на выходах 32 блока 5 значения К цифр чястцого с избытком. Пля исключения этого в блоке 5 деления усеченных чисел предусмотрены два канала формирования цифр; частного. Первый канал образован сумматором 6, первым вычитятелем 7 и первым узлом 9 деления. На выходак первого узла 9 деления формируются К цифр частного в предположении, что после проведения остатка к однорядному коду в его старние разряды поступает единичный сигнал займа из младних разрядов {на вход займа первого вычитателя 7 подан с нины 24 устройства сигнал логической единицы). Второй канал включает тот же сумматор принудительного округления делителя 6, а также второй вычитатель 8 и второй узел 10 деления, На выходах второго узла 10 деления формируется К цифр частного B,ïðåäïoëoÿåíèè, что после приведения остатка к однорядному коду в его старшие разряды поступает нулевой сигнал займа из млядних разрядов (ня вход займя второго вычитятеля 8 подан с нины 25 устройства сигнал логического нуля). Выборка необходимого значения К цифр частного и подача его на выходы 32 блока 5 осуществляется с помощью коммутатора

11, который управляется сигналом на выходе 36 займа в стярние разряды второго вычитателя 14. Если сигнал

\ на выходе 36 второго вычитателя 14 соответствует логической единице, то коммутатор 11 передает на выходы 32 блока 5 значение К цифр частного, сформированных в первом узле 9 деле—

Ю ния, в противном случае на выходы 32 блока 5 передается значение К цифр ! частного, образованных с помощью BTo— рого узла 10 деления. Первый и второй вычитатели 7 и 8 преобразуют двухрядный код стярних разрядов остатка в однорядный с учетом возможного значения сигнала закма из младших разрядов в старние. Первый и второй узлы 9 и

10 деления могут быть реализованы самыми различными методами и средствами. Например, их можно синтезировать по соответствующим тяолицам истинности в виде быстродействующих логических преобразователей или же реализовать с применением ПЗУ. При больних значениях К целесообразна реализация их в виде однотактных делительных матриц, использующих алгоритмы деле1429109 ния с восстановленным или беэ восстановления остатков .

Определим какое число старших разрядов делителя и остатка необходимо обрабатывать и блоке 5 деления усеченных чисел, чтобы получить К цифр частного с точностью до единицы их младшего разряда ° Это число в первую очередь зависит от диапазона значений 10 делимого и делителя. Пусть делимое х и делитель у есть нормализованные положительные двоичные дроби, т.е.

1 1 — с х с 1 и —, c y с l, Это справедли15 во только на первом mare деления. В дальнейшем же, когда в роли делимого выступают промежуточные остатки, возможно нарушение нормализации делимого как влево, так и вправо, В общем случае делимое х в предлагаемом устройстве может изменяться в пределах

0=x с2у.

Покажем, что при принятых допущениях, для получения на выходах 32 блока 5 деления усеченных чисел двоичных цифр частного с точностью до единицы их младшего разряда, достаточно обрабатывать (K+2) старших разрядов делимого х (один разряд слева от занятой и (К+1)-й разряд справа от занятой) и (K+7) старших разрядов делителя у (все разряды находятся справа от занятой).

Действительно, пусть К, — значение старших (K+2) разрядов делимого х,у, значение старших (K+?) разрядов делителя у, х = х — х,, у = у — у„.Покажем, что максимальная абсолютная погрешность Я (разность между значением частного, полученным при делении иразрядных чисел и значением частного, получаемым при делении усеченных (K+?)-разрядных чисел) при этом будет заключаться в пределах

45 х Х! (к-!)

0 Е— (к 2) (? у Ф 2

Выполнение левого условия очевидно, поэтому ограничимся линь доказательством неравенства х х - (k-

> ! которое можно переписать в виде 55, -(к 1 2) (л-!)

x(», б 2 ) — х!ус2 у °

- (мб21

Л!л + ? ).. что максимальная абсть ", будет н том

О,те.у=у,;

> о

° - мЕк! етом этого пслучим:

Нетрудно видеть, солютная погрешно сГ!учае > когда у 2 х = х - 2-("")

2 Ямсллс — 2!, — . . ". С уч (!;2) -(к -!) - (<2) х ? + х,у,< 2 у,(у, +2 )1.(л 1 (кб!) -(к-!) (2v, -2 ) 2 +(2 - 2 )у,(2 (кб 2)

° у,(у,+2) Последнее неравенство будет выполняться, если cïðàâåäëèâî следующее (кбМ -(к !1 (i- 1 -(Кб2)

2v . 2 + v, 2 2»! {v +2 )

-(кб2) или 1(2 (у, + 2 ).

Последнее соотношение выполняется при всех значениях делителя у, зак1 люченных в пределах вЂ, с.у с 1 следовательно, значение К-разрядного частного, получаемого на выходах 32 блока 5 и ри делении в нем (K+2) — разрядных чисел, может быть либо равно значению старших К разрядов частного, получаемого при делении и-разрядных чисел, либо меньше его на единицу младшего

-(л-!) разряда с весом 2

В блоке умножения осуществляется перемножение (К-1) младших разрядов частного, сформированного на выходах

35 блока 5 деления усеченных чисел и поступающего на входы первой груп" пы блока 12 умножения, и и-разрядного делителя, хранимого в регистре 3 и поступающего на входы второй группы блока 12 умножения с выходов разрядов 30 регистра делителя 3. На выходах 40 и 41 первой и второй групп блока 12 образуется произведение в двухрядном коде (в виде двух чисел).

Блок 12 умножения комбинационного типа.

Первый нычитатель 13 комбинационного типа и выполнен по принципу запоминания заема. Как и н известном устройстве он содержит (и+1) одноразрядных вычитателей. В первом вычитателе 13 осуществляется вычитание из разности, сформированной на ныходах

39 второго коммутатора 17, произведения делителя на (K-1) цифру частного, образованного в двухрядном коде на .выходах 40 и 41 первой и второй групп

14291 блока 12 умножения. Результат этого вычитания„ являищийся очередным ос татком, получается на выходах 42 и 43 разности и заема вычитателя 13 в двухрядном коде.

Второй и третий вычитатели 14 и

15 комбинационного типа с ускоренным распространением заема. С помощьи вто:рого вычитателя 14 двухрядный код ос- 10 татка, хранящийся в первом и втором регистрах 1 и ? остатка в виде разности и заема, преобразуется в однорядный код. На выход 36 второго вычи" тателя 14 поступает сигнал заема, об- 15 разованный в разряде вычитателя с весом 2 . Этот сигнал заема посту, -(w+z) ,пает в разряд вычитателя 14 с весом .;2 " 1 . В третьем вычитателе 15 из однорядного кода остатка вычитается ! делитель хранящий в регистре 3.

В

С помощью второго коммутатора 17 осуществляется передача на входы уменьнаемого первого вычитателя 13 и на информационные входы третьей группы первого коммутатора 16 либо значения разности с выходом 36 второго вычитателя 14, когда на выходе заема старнего разряда 37 третьего вычитателя 15 присутствует сигнал логической единицы, либо значения разнос" ти с выходов 38 третьего вычитателя

15, когда на выходе заема старщего разряда 37 третьего вычитателя 15 присутствует сигнал логического нуля.

На информационных входах 39 вто35 рого коммутатора 17 формируется либо разность остатка в однорядном коде, получаемого на выходах 35 второго вычитателя 14 и делителя, хранимого в регистре 3, если остаток на выходе

35 второго вычитателя больне делителя, либо остаток, получаемый на выходах 35 второго вычитателя 14, если этот остаток меньне делителя, т.е. на выходах 39 второго коммутатора !7 формируется остаток такой, какой он получается в процессе деления при определении одной цифры частного.

С помощьи первого коммутатора 18 осуществляется передача на информаци»

50 онные входы первого регистра 1 остатка, либо значения делимого с входа

20 данных устройства, когда на втором выходе 48 блока 19 управления присутствует сигнал логической единицы, либо значение с разности с выходов 42 первого вычитателя 13, когда на третьем выходе 49 блока 19 управления

09 10 формируется сигнал логической единицы, или же значения выходов 39 разрядов второго коммутатора 17, когда на четвертом выходе 50 блока 19 управления присутствует сигнал логической единицы. Узел 18 коррекции частного предназначен как для коррекции, в случае необходимости, (К-1,1 мпадних разрядов частного, образованного в предыдущем такте работы устройства, так и для коррекции частного, сформированного в текущем такте. Коррекция (К-1)младиих разрядов частного, сформированного в предыдущем такте, осуществляется, если сигнал заема на выходе 37 старщего разряда третьего вычитателя 15 соответствует уровни логического нуля, а коррекция цифр частного, образованного в текущем такте, осуществляется, если сигнал на седьмом выходе 51 блока 19 управления соответствует уровня логического нуля, причем коррекция цифр частного,сформированного в текущем, также приводится в результате коррекции из вида 0ХХХ...Х к виду 100...0

К К

Блок 19 управления координирует работу узлов и блоков устройства при выполнении на нем операции деления чисел.

Устройство для деления чисел рабо» тает следувщим образом.

По первому синхроимпульсу на входе

21 синхронизации устройства на первом и шестом выходах 46 и 47 блока 19 управления формирувтся сигналы,по которым осуществляется запись п-разрядного делителя в регистр 3 делителя с входа 20 данных устройства, и обнуляется первый и второй регистры 1 и 2 остатка. По истечении действия первого импульса на входе 21 синхронизации устройства появляется потенциал логической единицы на втором выходе

48 блока 19 управления. Так как в первом и втором регистрах 1 и ? остатка хранятся нулевые коды, то на выходах

32 блока 5 деления усеченных чисел формируется нулевой код К-разрядного частного, на выходе 37 займа старг его разряда третьего вычитателя 10 обзуется сигнал логической единицы, на входах 39 разрядов второго коммутатора 16 формируется нулевой код, на выходах 42 и 43 разности и займа

1429109

12 первого вычитателя 13 формируются нупеные коды. С приходом второго импульса на вход 21 синхронизации устройства осуществляется зались с Вхо5 да 20 данными устройства п-разрядного кода делимого в первый регистр 1 остатка нулевого кода займа первого вычитателя 13 — во второй регистр 2 остатка и нулевого кода частного в 10 младшие разряды регистра 4 частного, По истечении действий второго импульса на входе 21 синхронизации устройства подготовительный этап, включающий два такта, заканчивается и далее выполняется собственно деление, в процессе которого за m тактов формируется m(K-1)+1 двоичных цифр частного.

25

50 ного частного н устройстве использует55 ного частного н устройстве используется значение К цифр частного, сформироРассмотрим более детально работу устройства в течение одного».-го такта (1 1 m) формирования К цифр частного. По значению старших разрядов текущего остатка, хранимого в регистрах

1 и 2 в двухрядном коде, и делителя, хранимого в регистре 3 делителя, на выходах первого узла 9 деления блока

5 деления усеченных чисел формируется

К двоичных цифр частного в предположении, что при проведении двухрядного кода текущего остатка в однорядный код образуется сигнал заема из младших разрядов остатка в старшие, а на выходах яторого узла 10 деления блока 5 деления усеченных чисел формируется К двоичных цифр частного в предположении, что при приведении днухрядного кода текущего остатка в однорядный код не образуется сигнал займа из младших разрядов остатка в старшие. Параллельно с работой блока

5 деления усеченных чисел работает второй нычитатель 14, который преобразует двухрядный код текущего остатка в однорядный код. По значению сигнала заема н старшие разряды на выходе 36 этого нычитателя осуществляется окончательное формирование К цифры частного на выходах 32 блока 5 деле-. ния усеченных чисел. Если этот сигнал займа соответствует сигналу логической единицы, то в качестве К-разрядся К цифр частного, образованных на выходах первого узла 9 деления блока деления усеченных чисел, а если сиг" нал заема соответствует сигналу логического нуля, то н качестве К-разряд30

45 ванного на выходах второго узла 10 деления блока 5 деления усеченных чисел. Сфор»»иронанные на выходах блока

5 деления усеченных чисел (К-1) младших разрядов частного 7. - " " поступают

1 в узел 18 коррекции частного и одновременно подаются на входы первой группы блока 12 умножения, на выхо," дах 40 и 41 которого образуется npo(k-1) изнедение у ° 7. н двухрядном коде.

На выходах 39 второго коммутатора 17

I I формируется разность r. = т;, -у7.; (т;, — значение текущего остатка в однорядном оде на выходах 35 второI го вычитателя 14; Z; — значение старшего разряда частного, который опреII деляется по знаку разности r;

= г;, — у, сформиронанной на ныходах36 третьего вычитателя 15). Если сигнал заема на выходе 37 заема старшего разряда третьего вычитателя 15 ранен

I логической единице, то 7. равно нулю, а если сигнал заема равен логическому ! нули, то 7. равно единице. На выходах

42 и 43 первого вычитателя 13 формируется н двухрядном коде разность (К -1» »к -11

r = т -vi . =-7. - 7. -v7., а

11( и

Если разность r ° — г;1 — у, сформированная на выходах 38 третьего вычитателя 15, положительна, т.е. старщий разряд / равен единице, старший разряд К-разрядного частного, сформированного в блоке 5 деления усеченных чисел, ранен нулю, то в -м также на седьмом выходе 51 блока 19 управления появляется сигнал логичес» кого нуля и в узле 18 коррекции частного образуется скорректированное Краарадное частное в виде 1ОО...О, а

К в качестве очередного остатка r пер-

1 ным коммутатором 16 устройства Bbl6Hрается разность r . Значение этой разt ности записывается в первый регистр ! остатка со сдвигом на (К-1) раэрядон нлево, а второй регистр 2 остатка при этом обнуляется. Во всех же других случаях в качестве очередного остатка выбирается разность г., значение которой в виде двух чисел записывается соответствующим образом со сдвигом влево на (К-1) разрядов в первый и второй регистры 1 и 2 остатка. При этом н узле 18 коррекции частного сформированное на выходах

32 блока деления усеченных чисел 5

К-разрядное частное не корректируется. Аналогичным образом работает уст13 14 29109 ройство во всех других тактах форми рования

К двоичных цифр ча .тихого.

Корректор K,Лелчик

Редактор В.Бугренкова Техред, !.. и."-.:ê

Заказ 51 25/45 т.ирах 704

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Ыосква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, уп, Проектí-р, 4