Генератор случайного процесса

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении моделирующей аппаратуры для решения задач исследования и оптимизации структуры сложных систем, для автоматизации испытаний на вибрационные, ударные и другие вчцы воздействия. Цель изобретения - упрощение генератора. Генератор содержит датчик 1 равномерно распределенных случайных чисел, два блока 2, 11 памяти, генератор 3 импульсов , два делителя 4, 12 частоты, три регистра 8, 9, 18, регистр 19 памяти, два триггера 13, 14, формирователь 17 импульсов, два счетчика 5,10 импульсов, два преобразователя 6,7 код - напряжение, элемент И 15, элемент ШШ 16, блок 20 сз мматоров по модулю два. Поставленная цель достигается за счет введения новых § блоков и функциональных связей, 1 ип. СО

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ. (2) ) 4129467/24-24 (22) 29.08.86 (46) 07.10.88. Бвл. № 37 (71) Минский радиотехнический институт

{72) А.С.Кобайло Ю.В,Корженевич. (53) 681.3 {088.8) .(56) Авторское свидетельство СССР № 517018; кл. G 06 F. 1/02, 1976.

Авторское свидетельство СССР № 102216), кл. С Об F 7/58, )982. (54) ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА (57) Изобретение относится к вычислительной технике и может быть использовано при построении моделируннцей аппаратуры для решения .задач исследования и оптимизации структуры слож„.Я0„„1429113 ц)) 4 С 06 Р 7/58 ных систем, для автоматизации испытаний на вибрационные, ударные и другие виды воздействия. Цель изобретения - упрощение генератора. Генератор содержит датчик 1 равномерно распределенных случайных чисел, два блока 2, 11 памяти, генератор 3 импульсов, два делителя.4, )2 частоты, три регистра 8, 9, 18, регистр 19 памяти, два триггера 13, 14» формирователь 17 импульсов, два счетчика

5, 10 импульсов, два преобразователя

6, 7 код — напряжение, элемент И 15, элемент ИЛИ 16, блок 20 сумматоров по модулю два. Поставленная цель достигается за счет введения новых ф блоков и функциональных связей. 1 ип.

1429! 13

Изобретение относится к вычислительной технике и может быть исполь, зовано при построении моделирующей аппаратуры для решения задач исследо- вания и оптимизации структуры сложных систем, для автоматизации испытаний на вибрационные, ударные, электрические и другие виды воздействий, Цель изобретения — упрощение гене-1Р ратора.

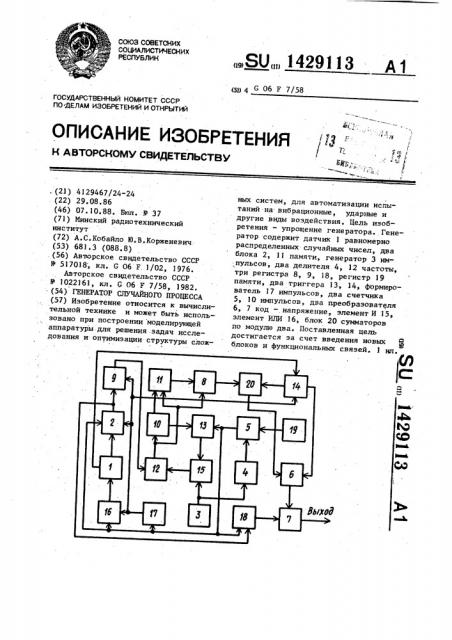

На чертеже представлена структурная схема генератора.

Генератор содержит датчик 1 равномерно распределенных случайных 15 чисел, блок 2 памяти, генератор 3 импульсов, делитель 4 частоты, счетчик 5 импульсов, преобразователи 6 и 7 коц — напряжение, регистры 8 и 9, счетчик 10, блок l! памяти, делитель 20

12 частоты, триггеры 13 и 14, элемент И 15, элемент ИЛИ 16, формирователь 17 импульсов, регистр 18, регистр 19 памяти, блок 20 сумматоров по модулю 2, 25

Генератор работает следующим образом.

На каждом цикле работы происходит развертывание во времени постоянного периода, формирование на этом пери- Зр оде импульса со случайной длителькостью, амплитудой и полярностью и определение случайных параметров импульса следующего цикла. Начало развертывания константы соответствует началу формирования импульса. Сигналом для начала очередного i-го цикла является установка триггера 13 в единичное состояние. В это время в регистр 9 заносится код, определяющий рр длительность х-го импульса выходного процесса, в регистр 19 — код, задающий амплитуду этого импульса, триггер

14 устанавливается в случайное равновероятное состояние, определяющее полярность -го импульса случайного процесса, а в счетчик 5 из регистра

19 заносится код константы, заданной на все время данного режима генерации и записанной в регистр 18 при настройке устройства.

Тактовые импульсы с выхода генератора 3 импульсов через делитель 4 частоты поступают. на вычитающий вход счетчика 5, производя последовательное вычитание единиц из этого счетчика. Единичное состояние триггера

13 обуславливает прохождение тактовых импульсов через элемент И 15 на информационный вход делителя !2 частоты, осуществляющего деление тактовой частоты с коэффициентом, код которого хранится в регистре 9. Счетчик 10 формирует последовательно адреса для блока ll памяти, по которым производится считывание кодов, задающих форму выходного импульса, считанные из блока !1 памяти коды заносятся в регистр 8. С выхода регистра 8 коды поступают на вход блока

20 и без преобразования поступают на младшие разрядные входы преобразователя 6 код — напряжение в том случае, если триггер 14 находится в единичном состоянии или инвертируется блоком

20, если триггер 14 установлен в нулевое состояние. Сигнал с прямого выхода триггера 14 поступает на старший разрядный вход преобразователя 6 код — напряжение, который работает в биполярном режиме. Нулевой уровень на выходе преобразователя 6 формируется при коде, содержащем единицу в старшем разряде и нули во всех остальных разрядах. Таким образом, при наличии нуля в старшем разряде, нули - po всех остальных разрядах.

Таким образом, при наличии нуля в старшем разряде преобразователя 6 на его выходе формируется отрицательное напряжение и для сохранения правильности формы выходного импульса коды, поступающие во все его остальные, кроме старшего разряды, должны быть в этом случае.проинвертированнымн..

На выходе преобразователя 7 код-напряжение формируется напряжение, пропорциональное напряжению на его входе опорного напряжения и усиленное в соответствии с кодом, хранящимся на протяжении данного цикла в третьем регистре 18.

Из блока 11 памяти последовательно считываются коды всех его ячеек, эти коды через первый регистр 8 и блок 20 поступают поочередно на вход преобразователя 6 и на выходе устройства формируется импульс, форма которого определяется значением кодов, считываемых из блока 11 памяти, амплитуда - кодом, хранящимся в регистре 18, длительность — коэффициентом деления делителя 12 частоты, код которого хранится в регистре 9, а полярность — состояние триггера 14.

В результате появления импульса на выходе переполнения r÷åò÷èêà 10

1429113 происходит установка нулевого состояния триггера 13, вследствие чего запрещается прохождение тактовых импульсов на вход делителя 12 часто5 ты и формирование импульса на выходе устройства заканчивается.

Далее следует формирование паузы в течение времени, равного интервалу между моментом появления сигнала на 10 выходе переполнения счетчика 5 и моментом формирования сигнала на выходе переполнения счетчика 10. В результате последовательного вычитания единиц счетчик 5 постепенно умень- 1$ шает свое состояние, При этом на выходе устройства устанавливается нулевой уровень, для этой цели в .последней ячейке блока 2 памяти должен быть записан нулевой код. При 20 достижении счетчиком 5 нулевого состояния по следующему тактовому импульсу на его выходе переполнения формируется сигнал, по которому происходит генерация случайного числа, 25 считывание по сформированному случайному адресу кода амплитуды для

+ 1-ro цикла работы из блока 2 памяти и занесение этого кода в регистр 18. По заднему фронту импульса, 30 появившегося на выходе переполнения счетчика 5 на выходе формирователя

17 импульсов формируется импульс, по которому происходит генерация нового случайного числа, считывание по сформированному случайному адресу из блока 2 памяти кода, задающего длительность импульса на i + 1-м цикле работы, занесение этого кода . в регистр 9, установка случайного 40 равновероятного состояния триггера

14 и запись в реверсивный счетчик 5 .кода константы из четвертого регистра 19.

Кроме того, происходит установка 45 единичного состояния триггера 13, в результате чего разрешается прохождение тактовых импульсов на вход второго делителя 12 частоты и начинается

+ 1 — и цикл работы устройства. 50

Формула изобретения

Генератор случайного процесса, содержащий датчик равномерно распределенных случайных чисел, генератор импульсов, выход которого соединен с входом первого делителя частоты, перBblH и второй регистры, первый и вторай счетчики импульcoR первый и R1Орой блоки памяти, третий регистр, выход которого соединен с информационным входом первого преобразователя код — напряжение, а т л и ч а ю шийся тем, что, с целью упрощения генератора Он содержит первый и второй триггеры, формирователь импульсов, элемент ИЛИ, элемент

И, второй делитель частоты, второй преобразователь кад — напряжение, регистр памяти, блок сумматоров по модулю два, причем выход первого разряда датчика равномерно распределенных случайных чисел соединен с ииформационным входом первого I p;II.гера, вход синхронизации которого соединен с выходом формирователя:мпульсав, первым входом элемента ИПИ.. Bõñäñò синхронизации первого регистра и пОдключен к перВОму вхОду -1тепие первого блока памяти., Выход первого регистра соединен с Входам задания кОэффициента деления, Вта.3c га дели— теля частоты, информационный В:.Од которого соединен с Выходам элемента

И, первый в;Од которого соеди пи с выходом генератора импульсов-:, Винер ный выход первого триггера соединен с первым входам блока сумматоров по модулю два, Выходь: котора"-"" саед.и:-.— ны с младшими разряцными ;.Ода:;и второго преобразователя ко. вЂ, — напря-жение старший разрядный ьхОд като рого соединен с прямым выходом первого триггера, Выход второго преобразователя кад — напряжение соединен с входом задания опорного напряжения первого преобразователя код — напряжение, выход которого является выходом генератора, выход датчика равномерна распределенных случайных чисел соединен с адресным Входом первого блока памяти, второй вход "ЧтеI ние" которого соединен с вторым входом элемента ИЛИ. выход -переполнения второго счетчика соединен с входом установки В "1" в-.араго триггера, входом синхронизации третьего регистра, входом формирователя импульсов и подключен к выходу переполнения второго счетчика, выход элемента ИЛИ соединен с входом Опрос" датчика равномерно распределенных случайных чисел, Выход первого блока памяти соединен с информационными входами первого и третьего регистров, выход второго делителя частоты сое1429113

Составитель И. Столяров

Редактор В.Бугренкова Техред Л.Сердюкова Корректор И.Иуска

Заказ 5127/46 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 динен с входом синхронизации второго регистра и второго блока памяти и . подключен к входу первого счетчика, информационный выход которого соединен с адресным входом второго блока памяти, выход которого соединен с ,информационным входом второго регист-! ра, выход переполнения первого счет чика соединен с входом установки в

"0" второго триггера, выход которого соединен с вторым входом элемента И, выход первого делителя частоты соединен с вычитающим входом второго счетчика, вход предварительной установки которого соединен с выходом регистра памяти, выход второго регистра соединен с вторым входом блока сумматоров по модулю два.