Многофункциональный преобразователь

Иллюстрации

Показать всеРеферат

СОВХОЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU 1429128 (51)4 С 06 F 15/353

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 403 3908/24-24 (22) 3 6.0),86 (46) 07.10.88. Бюл. У 37 (72) С.В. Казинов и А.А. Шляппо (53) 681.325 (088.8) (56) Авторское свидетельство СССР

В 1182539, кл. G 06 F 15j31, 1984.

Авторское свидетельство СССР

У 1241257, кл. G 06 F 151353, 1 984. (54) 11НОГОФУНКЦИОНАЛЬНБ1И ПРЕОБРАЗОBATEЛЪ (57) Изобретение относится к вычислительной технике, в частности к кусочно-ступенчатым функциональным преобразователям. Цель изобретения— сокращение аппаратурных затрат, повышение быстродействия преобразователя и расширение его функциональных возможностей за счет воспроизведения функций произвольного вида. Преобразователь содержит регистры 1, 2, блоки 3-6 памяти, счетчик 7, вычитатель 8, триггер 9, элемент И 10, коммутатор 11, блок 12 управления.

1 з.п. ф-лы, 2 ил.

1429128

25

Изобретение относится к вычислиельной технике, в частности к кусочно-ступенчатым функциональным преобразователям.

Цель изобретения — сокращение аппаратурных затрат, повышение быстродействия преобразователя и расшире ние его функциональных возможцостей за счет воспроизведения функций произвольного вида.

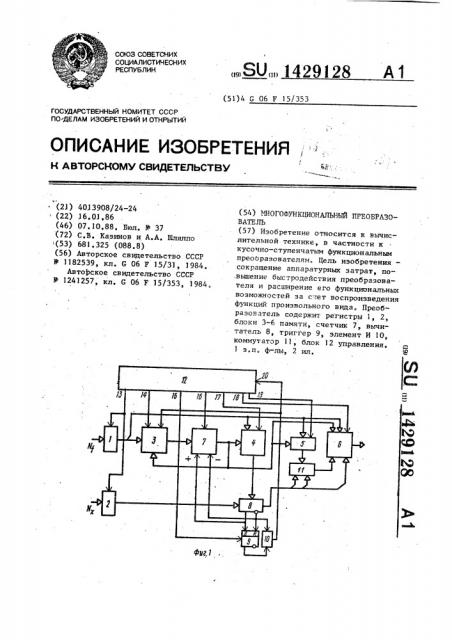

На фиг..l приведена схема преоб- . разователя; на фиг. 2 — возможный вариант выполнения блока управления.

Преобразователь (фиг.1) содержит регистры 1 и 2, блоки 3-6 памяти, счетчик 7, вычитатель 8, триггер 9, элемент И 10, коммутатор 11, блок

12 управления, содержащий выходы 1319, вход 20, счетчик 21 постоянный запоминающий узел 22, управляемый делитель 23 частоты, элемент И 24, триггер 25, выходы 26 и 27 узла 22, тактовый вход 28, вход 29 запуска, 1 выход 30 сигнала окончания преобразования.

Преобразователь .работает следующим образом.

В исходном состоянии регистры l и 2, счетчики 7 и 21 и триггеры 9 и

25 обнулены. В .блок 4 памяти занесены коды узловык значений абсцисс участков аппроксимации, в блок 6— коды выборочных значений ординат у функции.íà раэличнык участках апнрохсймации, в блоке 5 — коды управления коммутатором 11 (блоки 5 и 12 памяти перепрограммируемого тина). В блок 3 памяти, занесены коды предварительной установки текущих номеров участков аппроксимации (например, нули), Работа устройства начинается с подачи импульса запуска на вход 29 блока 12 управления. Этим импульсом триггер 25 устанавливается в единичное состояние и отпирает элемент И

24, Первый же импульс тактовой частоты f© проходит через элемент И 24, делитель 23 (на котором установлено минимальное время задержки) и устанавливает счетчик 21 в состояние 001. Узел 22 по состоянию адреснык входов 0001 (где первый 0 — сигнал на входе 20, а 001 - состояния первых трех разрядов счетчика 21) формирует единичный сигнал на выходе 13, который поступает на синхровходы регистров 1 и 2, В результате s регистр 2 заносится код текущего значения преобразуемого аргумента, а в регистр

1 (первое и второе поле данных регистра) — коды номера аргумента и номера функции.

По истечении времени записи даннык в регистры l и 2 на выходе делителя 23 появляется импульс тактовой частоты, который переводит счетчик

21 в состояние 020. Снимается сигнал с выкода 13 и устанавливается единичный сигнал на выходе 14 блока 12 управления, поступающий на вход "Выборка кристалла" блока 3 памяти. Так как нулевым сигналом с выхода элемента И 10 блок 3 памяти установлен в режим чтения, то импульсом с выхода

14 блока 12 управления осуществляется считывание кода предварительной

20 установки номера участка аппроксимации в счетчик 7, После установки кода в счетчике

7 на выкоде делителя 23 появляется очередной импульс, который переводит счетчик 21 в состояние 011. По этому состоянию снимается сигнал с выхода

14 и формируется единичный сигнал яа выходе 17 блока управления. Сигнал с выхода 17 поступает на вход разрешения чтения блока 4 памяти.

В результате на выходе блока 4 памяти устанавливается код узлового значения абсциссы участка аппроксимации.

Вычитатель 8 вычисляет разность между кодом текущего значения аргумента и кодом узлового значения абсциссы.

Если эта разность отрицательная, то единица устанавливается на прямом выходе знакового разряда вычитателя

8, если разность положительная, то единица устанавливается на янверсиом выходе. В обоих случаях состояние выходного сигнала элемента И 10 яе изменяется, так как триггер 9 был обнулен перед началом цикла преобразования.

По завершении установки -выходного кода вычитателя 8, счетчик 21 переводится в состояние 100 очередным импульсом с выхода делителя 23 частоты. В результате снимается сигнал с выхода 17 и формируются единичные сигналы на выходах 16 и 15 блока 12 управления. Импульсом с выхода 15 осуществляется запись в триггер 9 состояния знака разности вычитателя

8. Одновременно с этим импульс с выхода 16 изменяет состояние счетчика

7 на единицу младшего разряда, при-:! 429128

45 чем режим суммирования или вычитания в счетчике 7 определяется знаком разности вычитателя 8„ После установки нового значения кода счетчика 7 на вход счетчика 21 приходит очередной импульс с делителя 23 и в счетчике

21 устанавливается код 101. Узел 22 формирует единичный импульс на выходе 2б, по которому счетчик 21 сбрасывается в состояние 011.

Далее повторяется вышеуказанная последовательность действий по Обновлению выходного кода блока 4 памяти, формированию кода разности на выходе вычитателя 8, считыванию знака кода разности в триггер 9 и инкрементному изменению кода счетчика 7 до тех пор, пока не будут уст":HoBzieны единичные сигналы на инверсном выходе знакового разряда вычитателя

8 и прямом выходе триггера. Данное состояние свидетельствует о том, что в счетчике 7 установлен код номе а участка аппроксимации, соответствующий текущему значению преобразуемого аргумента. В результате на выходе элемента И 10 появляется едини гный сигнал, поступающий на вход 20 блока

12 управления и вход управления режи- З мом блока 3 памяти. При этом coñòñaние выходных сигналов блока 12 управления не изменяется, а блока 3 памяти переводится в режим записи данных.

После прохождения на счетный вход счетчика 21 очередного импульса с выхода делителя 23 состояние адресных входов узла 22 станет равным 1100

{где первая "1" определяется сигналом на входе 20 блока 12 управления).

По этому состоянию формируются единичные сигналы на выходах 14 и 19 блока 12 управления. Иьшульсом с выход-.

14 осуществляется запись в блок 3 па= мяти выходного кода счетчика 7, .Оответствующего текущему номеру уча«ттка аппроксимации. Импульс с выхода !9 разрешает выдачу на выход блока 5 памяти кода управления работой комму-татора 11. Коммутатор 11 подключает к четвертому адресному входу блока 6 памяти соответствующую группу выходных разрядов вычитателя Я в зависи-. мости от разрядности представления максимального значения разности на текущем участке аппроксимации.

Далее выходной код счетчика 21 адреса увеличивается на единицу младшегс разряда. IIo ссстояник адресных входов 1 1! 01 фс р;.Н»руетс т» ед1»-;1нт1нья!» ст»Г :àë на выхтде блок;- 12 yi»p;.вления.

11ьт!-тльс с выход,: разре1ттае-; B.,iiia y на —;ыхсд блока 6 памяти кода текущеГО знаттания фуНКДИН, При ЭТОМ На адрес!»ые зхст»ьт блока 6 памяти поступают; код нсмepa п..»eo>paaoBa!»I»s! с выхода ре Гистра 1, код нсьтера тек,-щего у -.астка a . HpoI»cèìa!II»:» с выхода счетчик2 H -.Од pa= »сст1» между те;ргумента и узловым

1(утцим 3 и а ч е I H e I » значением абс 111.::.= 1 ел!я Я

К ОД а 1 С Т PО . ".. т сы с тзьжсдсв Бьгчитатсра 1 1 тХС НO1 О

2д ".eс а т»с КО О "

$«Г! Т =: С Ь I.. П

С ян !12 т

5!")Ка

ПЕттЕХОЦ1»«Г B COC»a p:- -хо управле!

7Л л Ю 1»11 ! й

:.;Г1тал Обн

НИЛ тт::3 С6111Р т С Я григ; 9 32 с!1 г 321тнс - I Г." ссс=! C< ГО Я1»тта

«!» -. .Г1-1 та«12 на Bыха;е

15 пр»1 этсм :e .»çê-:ляется)« После заверитеHHsi cC»pc« -.: . p»»гге ра 9 счетч1»к

) т -т -т т, з т" а Т.т»,! т,-„ н те 1 - гт; «, с:с гттию Iqg»1тгру

"7 ется . 111-1»ал ".;-.- Bi:.-": -pe ., узл= чика z. -.; -.. риг::.- 2 25 - vc-: ансзку

Н2 цт -, - Л. 3 К -т ца;.-,т»1»тр:;-! т-Сй 3адер:: .и, Сигнал с прямого вь1-.;сца трнггера 23 запир:тьз-. элем:.1 т 24»т,. а это 1

СИГНСЛ С I!HBeРС .,1 »ГЛ BI тХСДа ГСНГГЕра э псс- пает 112 в,-.с-. д»0. разре-.

1IIaS BI 1От!»e»1 е ттт! Нкn»OI!a IBI»OrO ПРЕОбразования следующего аргумента, ФОрмул а изобретения

1. т11»СГСфу1»кц;:=ОН21тъНЬ ПресбраЗОватель, содержа.». : -:.=.- ".,-.»о-..- управления, первый и втс сй рог.";стры, первый и второй блоки па ;1"г1.„- ст»етчик григгеР элемент 1 .:-. — зьтт»итательт ннвеРсньгй вь сод 3 -:=- к:.вo::o ра-.р;-:,а котсрОго соединен с вход:.::: сбргса триггера, ВЫХОД КОТОРОГО Соец-т1С1» С ПЕРВЫМ ВХОДОМ ЭЛЕМЕНТа V: 3 !oi»II КОДОВ ТЕКУЩЕГО значения аргум:=т-;:-.a,. номера реализуе" и-й функции преобразователя ссединеНЫ С И1»ЙО Тт таПИС - .. -. "т".H БХСЦ21. 1» ПЕРВОГО

H в гсрсгс oeI Hc .. :Ов ООстветствсннс выход первого ре -1»с ра co.-.ди»»ен с входом уменьшен мсго в =;- итателя, вход вычитаемо-о кстсрсгс соединен с выходо.. ; !epBo! o ;:.o:ca памяти., HepB тт .

ТО:H . I 3-" = . .СЬСГ О Р23РЯД 2 ззгтт»т ТЕ ля 8., Г ре зуль гете с--»ï,;!ac òca ед»»т11»нный сигнал» ". вк: а 0 б o:a . управ5 14291 адресный вход которого соединен с выкодом второго регистра и адресным входом второго блока памяти, выход которого соединен с входом начальной установки счетчика, выход которого

Соединен с вторым адресным входом первого блока памяти, о т л и ч а юи и с я тем, что, с целью сокраения аппаратурных затрат, повышения

ыстродействия преобразователя И рас- 1О ширения его функциональных возможнос,тей за счет воспроизведения функций

;произвольного вида, в него введены третий и четвертый блоки памяти и

1 коммутатор, первый выход блока управ- 15 ,ления соединен с синхровходами пер вогоо и второго регистров, второй

1 выход блока управления соединен с входом "Выборка кристалла" второго блока памяти, вход управления режимом 20 которого соединен с одноименным входом блока управления и выходом элемента И, второй вход которого соединен с инверсным выходом знакового разряда вьтчитателя, прямой и инверсный выходы знакового разряда которого соединены с соответствующими входами управления реверса счетчика, выход которого соединен с входом данных второго блока памяти и первыми адресными входами третьего и четвертого блоков памяти, вторые адресные входы которых соединены с выходом второго регистра, третий выход блока управления соединен с тактовым 35 входом триггера, вход установки которого соединен с прямым выходом знакового,разряда вычитателя, выходы разрядов кода разности которого соединены с информационными входами ком- 1О мутатора и третьим адресным входом третьего блока памяти, выход которого является выходом преобразователя, с четвертого по седьмой выходы блока управления соединены с синхро28 входами счетчика первого, третьего и четвертого блоков памяти соответственно, выход последнего соединен с управляющим входом коммутатора, выход которого соединен с четвертым адресным входом третьего блока памяти.

2. Преобразователь по и.1, о тлич ающийс я тем, что блок управления содержит постоянный запоминающий узел, счетчик, управляемый делитель частоты, элемент И и триггер, вход установки которого является входом запуска преобразователя, вход сигнала конца преобразования которого соединен с инверсным выходом триггера, прямой выход которого соединен с первым входом элемента И, выход которого соединен с информационным входом управляемого делителя частоты, выход которого соединен со счетным входом счетчика, выход которого соединен с первым адресным входом постоянного запоминающего узла, выходы с первого по третий разрядов которого являются с первого по третий выходами блока управления соответственно, вход управления режимом ко орого соединен с вторым адресным входом постоянного запоминающего узла, выход четвертого разряда которого соединен с входом сброса старшего..разряда счетчика, вход сброса которого соединен с входом сброса триггера и выходом пятого разряда постоянного запоминающего узла, выходы с шестого по девятый разрядов которого являются с четвертого по седьмой выходами блока управления, тактовый вход которого соединен с вторым входом элемента И, выход кода коэффициента деления постоянного запоминающего узла соединен с управляющим входом управляемого делителя частоты.

1429128

1У 74 1$ fb 77 Ю 1У

Фиг.Z

Составитель Н. Матвеев

Техред Л. Сердюкова Корректор А. Обруч ар

Редактор В. Бугренкова

Заказ 5)27/46

Тщ аж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4