Устройство для анализа электрокардиограмм

Иллюстрации

Показать всеРеферат

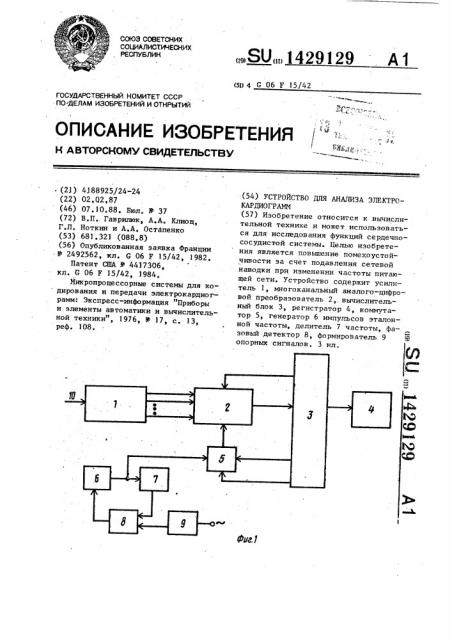

Изобретение относится к вычислительной технике и может использоваться для исследования функций сердечнососудистой системы. Целью изобретения является повьшение помех;оустойчивости за счет подавления сетевой наводки при. изменении частоты питающей сети. Устройство содержит усилитель 1, многоканальный аналого-цифровой преобразователь 2,, вычислительный блок 3, регистратор 4, коммутатор 5, генератор 6 импульсов эталонной частоты, делитель 7 частоты, фазовый детектор 8, формирователь 9 Ш опорных сигналов. 3 ил„

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 G 06 F 15/42

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО;ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Н д BTOPCKOMV СВИДЕТЕЛЬСТВУ

° (2) ) 4) 88925/24-24 (22) 02,02,87 (46) 07.)0.88. Бюл. У 37 (72) В.П.. Гаврилюк, А.А. Клиоц, Г.Л. Ноткин и А.А. Остапенко (53) 68).32) (088.8) (56) Опубликованная заявка Франции

В 2492562, кл. С 06 F 15/42, 1982.

Патент США У 44)7306, кл. 0 06 F 15/42, )984.

1фикропроцессорные системы для ко дирования и передачи электрокардиограмм: Экспресс-информация Приборы и элементы автоматики и вычислительной техники", 1976, В )7, с. 13, реф. 108.

„„80„„1429129 A 1 (54) УСТРОЙСТВО ДЛЯ АНАЛИЗА ЭЛЕКТРОКАРДИО ГРАММ (57) Изобретение относится к вычислительной технике и может использоваться для исследования функций сердечнососудистой системы. Целью изобретения является повьппение помехоустойчивости эа счет подавления сетевой наводки при изменении частоты питающей сети. Устройство содержит усилитель 1, многоканальный аналого-цифровой преобразователь 2,, вычислительный блок 3, регистратор 4, коммутатор 5, генератор 6 импульсов эталонной частоты„ делитель 7 частоты, фазовый детектор 8, формирователь 9 Ж опорных сигналов. 3 ил.

1429129

Изобретение относится к вычисли ельной технике и может использовать.я для исследования функций сердечнососудистой системы.

Цель изобретения — повышение помехоустойчивости за счет подавления сетевой .наводки при изменении частоты питающей сети.

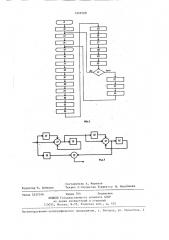

На фиг. 1 представлена блок-схема стройства; на фиг, 2 — блок-схема алгоритма функционирования устройства; на фиг. 3 — блок-схема. алгоритма работы цифрового фильтра.

Устройство содержит усилитель 1, ! .,многоканальный аналого-цифровой пре-! образователь (АЦП) 2, вычислитель ный блок 3, регистратор 4, коммутатор 5, генератор 6 импульсов зталон1 ной частоты, делитель 7 частоты, фа- 20

1 зовый детектор 8, формирователь 9 опорных сигналов, вход 10 устройства,, шаги 11-42 алгоритма, В качестве вычислительного блока может быть использована, например, ЭВИ "Ириша", Код АЦП 2 поступает в оперативную память через первый порт параллельного интерфейса, Через, второй порт осуществляется переключение групп отведений усилителя 1, переклю- 30 чение каналов АЦП 2, управление коммутатором 5 и выдача импульсов программного пуска АЦП 2. Через третий порт .параллельного интерфейса производится вывод. обработанных кривых

ЭКГ из оперативной памяти на регистратор.

Устройство работает в соответствии с алгоритмом (фиг. 2), шаги которого обозначены следующим образом: д0

11 — Начало; 12 — Инициализация интерфейса; 13 — Включение АЦП на первый канал; 24 - Переключение коммутатора на запуск АЦП; 15 — Состояние ожидания прерывания по концу пре- gg образования; 16 — Считывание результатов преобразования; 17 — Запись отсчета в задержку 38; 18 — Округление до 8 бит; 19 — Запись отсчета в задержку. 35; 20 — Вычитание задержанного задержкой 35 отсчета из входного округленного значения, 21 — Суммирование с содержимым задержки 38;

22 - Запись результата в задержку 38;

23 — Округление до 8 бит; 24 — Запись в задержку 40; 25 — Вычитание задержанного задержкой 40 отсчета из округленного результата вычислений на первом звене; 26 — Суммирова-! ние с содержимым задержки 42; 27

3 апись в 3 аде ржк у 42; 28 — Ок ругление до 10 бит; 29 — Вычитание из входного отсчета, задержанного задержкой 41; 30 — Вывод результата;

31 — Проверка: подвергался ли отработке третий канал; 32 — Переключение АЦП на следующии канал; 33—

Переключение коммутатора на программный запуск; 34 — Программный запуск

АЦП.

Кроме того, обозначены задержка

35 на 512 отсчетов, задержка 36 на

504 отсчета, сумматор-вычитатель 37, задержка 38 на 8 отсчетов, вычитатель 39, задержка 40 на 512 отсчетов, сумматор-вычитатель 41, задержка 42 на 8 отсчетов (фиг. 3).

Устройство работает следующим образом.

После включения устройства блок

3 производит программирование параллельного интерфейса для реализации связей, переключает АЦП 2 на первый канал, коммутатор на запуск преобразования и переходит в состояние ожидания прерывания, Генератор 6 вырабатывает импульсы с частотой, в 8 раз превышающей частоту сети, которые после деления иа восемь поступают на вход фазового детектора 8. На другой вход последнего поступает опорный сигнал сетевой частоты с формирователя 9, Фазовый детектор 8 вырабатывает сигналошибку, пропорциональный разности фаз импульсной последовательности и опорного сигнала. Этот сигнал-ошибка подстраивает частоту генератора

6 таким образом, что разность фаз сигналов на обоих входах фазового детектора 8 равна нулю. Этим обеспечиваетсц стабильность временного положения импульсов, запускающих АЦП, внутри периода сетевой частоты, Импульс запуска через коммутатор

5 поступает на АЦП 2, включая аналбго †цифров преобразование. По его окончании формируется сигнал запроса прерывания, под воздействием которого вычислительный блок начинает обработку текущего отсчета. Обработка отсчета заключается в выполнении операций алгоритма (фиг. 3).

Блок 3 считывает отсчет ЭКГ. Считанный отсчет записывается в буфер задержки 36 на 504 oiсчета. После этого производятся вычисления для

3 142 первого звена фильтра, отсчет округляется до 8 бит и записывается в буфер задержки 35 на 512 отсчетов. После этого, отсчет, задержанный задержкой 35 íà 512 отсчетов, вычитается из входного отсчета, суммируется с содержимым буфера задержки 38 на 8 отсчетов, а результат без округления снова записывается s буфер задержки 38. Округленный до 8 бит результат вычислений на .первом этапе используется в качестве входного отсчета для вычислений при реализации второго звена фильтра.

Вычисления, проводимые на втором этапе аналогичны с той лишь разницей, что действия производятся над содержимым задержки 40 на 512 отсчетов и задержки 42 на 8 отсчетов. Результат вычислений на втором этапе округляется до 10 бит и вычитается из отсчета, задержанного на 504 периода дискретизации задержкой 36, а результат выводится на регистратор.

После этого блок 3 переключает

АЦП 2 на следующий канал, коммутатор в положение, обеспечивающее программный запуск АЦП и собственно его за, пуск. При обработке данных по второму каналу производятся аналогичные действия.

После обработки отсчета по третьему каналу повторяются все действия, начиная с квадрата 13 алгоритма. Задержки 35, 36, 38, 40.и 42 реализованы в оперативном запоминающем устройстве блока З.смещением адресов отсчетов при каждом обращении к буфе.ру.

9129

Фо рмула из об ре тения

l !

Устройство для анализа электрокардиограмм, содержащее многоканальный аналого-цифровой преобразователь, вход разрешения считывания и выход которого соединены с выходом считывания и информационным входом вычислительного блока соответственно, выход данных вычислительного блока является выходом устройства, информационные входы которого соединены с информационными входами многоканального аналого-цифрового преобразователя, о т л и ч а ю щ е е с я тем, что, с целью повьппения помехоустойчивости за счет подавления сетевой наводки при изменении частоты питающей сети, в него введены формирователь опорного сигнала, фазовый детектор, генератор импульсов эталонной частоты, делитель частоты и коммутатор, выход которого соединен с управляющим вхоI

25 дом многоканального аналого-цифрового преобразователя, стробирующий и

"информационно-управляющие входы коммутатора соединены с выходом генератора импульсов эталонной частоты и

30 выходами команд вычислительного блока соответственно, выход генератора импульсов эталонной частоты соединен с входом делителя частоты, выход которого соединен с первым .входом фазоBoI o детектора, BTopoH Bxop KQToporo соединен с выходом формирователя опорного сигнала, выход фазового детектора соединен с входом подстройки частоты генератора импульсов эта4р лонной частоты.

1429129

Составитель А. Жеренов

Техред Л. Сердюкова Корректор N. Васильева

Редактор Н. Бобкова

Заказ 5127/46 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4