Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к электронной технике и может быть использовано в приборах для обработки или преобразования аналоговой информации. Цель изобретения - повьппение точности , стабильности и быстродействия устройства . Поставленная цель достигается за счет устранения влияния коммутации ключевого элемента на утечку заряда с запоминающего элемента (уменьшение погрешности запоминания) и устранения токов утечки ключевого элемента (уменьшение погрешности хранения ) . Быстродействие устройства повьш1ается за счет малого времени коммутации токовых переключателей и использования запоминающего элемента меньшей емкости. 1 ил. СЛ

А1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (S1)4 G 11 С 27 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ HoM)STET cccp

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4189487/24-24 (22) 30,01.87 (46) 07.10.88. Бюл. )) 37 (71) Всесоюзный научно-исследовательский, проектно-конструкторский институт геологических, геофизических и геохимических информационных систем и Московский инженерно-физический институт (72) В.А.Королев, Б.В .Михайленко и В.А.Цыганков (53) 681.327.66 (088.8) (56) Титце У., Шенк. К. Полупроводниковая схемотехника. - М.: Мир, 1983, с.286, рис.17-19.

Авторское свидетельство СССР

Ф 881866, кл. С 11 С 27/00, 1980. (54) АНАПОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к электронной технике и может быть использовано в приборах для обработки или преобразования аналоговой информации.

Цель изобретения - повышение точности, стабильности и быстродействия устройства. Поставленная цель достигается за счет устранения влияния коммутации ключевого элемента на утечку заряда с запоминающего элемента (уменьшение погрешности запоминания) и устранения токов утечки ключевого элемента (уменьшение погрешности хранения). Быстродействие устройства по- ф вышается за счет малого времени коммутации токовых переключателей и использования запоминающего элемента меньшей емкости. 1 ил.

1429173

Изобретение относится к электрон ной технике и может быть использовано в приборах и узлах для обработки или преобразования аналоговой информации.

Целью-изобретения является повышение точности, стабильности и быстродействия устройства.

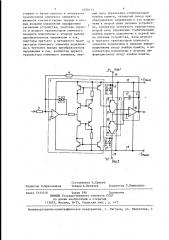

Ца чертеже показано аналоговое за-10 поминающее устройство.

Устройство содержит преобразо1 ватель 1 напряжения в ток, ячейку 2 ! памяти, элементы 3 и 4 обратной связи на резисторах, ключевой элемент 5., or-f5, раничительные элементы 6 и 7, первый, второй, третий и четвертый биполярные . транзисторы 8-11 ключевого элемента !

5, первую и вторую шины 12 и 13 питания.и входы 14 и 15 управления уст- 20 ройства.

Ячейка 2 памяти содержит операционный усилитель 16 и накопительный ! элемент 17 на конденсаторе, обкладки которого подключены соответственно к 25

1 инвертирующему входу и выходу операционного усилителя, неинвертирующий вход которого подключен к шине нулевого потенциала.

Устройство работает следующим образом.

В режиме "Выборка" транзисторы 9 и 10 элемента 5 открыты и через них течет сквозной ток преобразователя 1, задаваемый элементами 3 и 4, базы

35 транзисторов 9 и 10 заземлены, а коллекторы находятся под потенциалом виртуального нуля, поэтому разность потенциалов между коллектором и базой у этих транзисторов равна напряжению

40 смещения нуля усилителя 16 и близка к нулю. При переходе устройства в состояние "Хранение" проводят ток транзисторы 8 и 11. При этом переключении транзисторы 9 и 10 закрываются по цепи эмиттера.

Таким образом, при коммутации разность потенциала между коллектором и базой не меняется и остается равной нулю следовательно, параэитная утеч9

50 ка заряда с элемента 17 через эти емкости не происходит. Изменение разности потенциалов между заземленными базами и эмиттерами транзисторов .также не вызывает паразитной утечки заряда с элемента 17, поскольку токи

55 перезарядки емкостей эмиттерных переходов замыкаются через корпусной провод и не протекают в цепи заряда элемента 17. Параэитная утечка заряда на элементе 17 воэникает эа счет нзменения потенциалон между коллекторами и эмиттерами трензисторов 9 и 10.

Однако емкость коллектор — эмиттер имеет чисто конструктивную природу и, следовательно, не зависит ни от режима работы транзистора, ни от температуры. К тому же из-за парафаэного изменения потенциалов на эмиттерах транзисторов 9 и f0 при переключении происходит частичная (иэ-за неравенства емкостей коллектор - эмиттер транзисторов 9 и 10) компенсация паразитной утечки заряда с элемента 17. Таким образом достигается минимизация ошибки запоминания.

1 .При запертом состоянии транзисторов потенциалы всех трех электродов каждого иэ транзисторов близки к нулю, при точном равенстве нулю этих потенциалов токи через транзисторы отсутствуют. Поэтому утечка через запертые транзисторы вызывается лишь малыми остаточными потенциалами на эмиттерах транзисторов 9 и 10 и напряжением смещения нуля элемента 17.

Таким. образом достигается минимизация ошибки хранения.

Формула изобретения

Аналоговое запоминающее устройство, содержащее преобразователь напряжения в ток, ячейку памяти, первый и второй элементы обратной связи на резисторах, первые выводы которых подключены к входу преобразователя напряжения в ток, второй вывод резистора первого элемента обратной связи является информационным входом устройства, второй вывод резистора второго элемента обратной связи подключен к выходу ячейки памяти и является информационным выходом устройства, первый выход формирователя напряжения в ток подключен к первой шине пита" ния устройства, о т л и ч а ю щ ее с я тем, что, с целью повьппения точности, стабильности и быстродействия устройства, в него введены ключевой элемент на первом, втором, третьем и четвертом биполярных транзисторах, первый и второй ограничительные элементы, первые выводы которых подключены к шине нулевого потенциала, вторые выводы подключены соответит

Улр 2

Составитель А.Ершова

Техред А.Кравчук

Корректор Л.Пилипенко

Редактор О.Юрковецкая

Заказ 5133/49 Тираж 590 Подписное.

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная, 4 з

1429173 ственно к баэам первого и четвертого вый вход управления стабилизацие транзисторов ключевого элемента и ячейки памяти, четвертыи выход пре являются соответственно первым и вто- образователя напряжения в ток подклюP ым входами управления парафазными чены к второй шине питания устройстсигналами устройства, эмиттеры перво- ва, коллектор четвертого транзистора, го и второго транзисторов ключевого второй вход управления стабилизацией элемента подключены к второму выходу ячейки памяти подключены к первои шипреобраэователя напряжения в ток, не питания устройства, базы второго эмиттеры третьего и четвертого тран- 1О и третьего транзисторов ключевого зисторов ключевого элемента подключе- элемента подключены к первому инфор" ны к третьему выходу преобразователя мационному входу ячейки памяти, а их напряжения в ток, коллектор первого коллекторы подключены к второму интранзистора ключевого элемента, пер- формационному входу ячейки памяти.