Формирователь синусоидальных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике . Цель изобретения - повышение точности формирования выходных сигналов . Формирователь содержит задающий г-р 1, RS-триггер 2, эл-ты 2И-НЕ 3 и 15, реверсивный счетчик 4, ДАЛ 5, блок коммутируемых весовых сопротивлений (ВВС) 6, дешифратор 7, управляемьш источник 8 тока, усилитель 9, управляемый инвертор 10, эл-т ИЛИ П, эл-т НЕ-И-НЕ 12, счетный триггер 13, ключ 14 и резистор 16. На выходе ЦАП 5 формируется ступенчатое напряжение . При последовательном шунтировании выхода ЦАП 5 соответствующим резистором ВВС 6 уменьшается величина ступеней аппроксимации соответствующей хорды синусоиды, т.е. угол наклона аппроксимируемой прямой, и в устройстве осуществляется последовательное формирование хорд синусоиды . При переключении счетчика 4 из ( режима суммирования в режим вычитания ключи ВВС 6, источника 8 и ЦАП 5 . начинают переключаться в обратном порядке и, следовательно, угол наклона хорд синусоиды изменится на отридательный. Т. обр., осуществляются циклы формирования периода синусоидального напряжения. 4 ил. Si (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (Ю4 НОЗ В !900

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕКНЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4084806/24-09 (22) 09.07.86 (46) 07.10.88. Бюл. № 37 (71) Чувашский государственный университет им. И.Н.Ульянова (72) В.А.Борисов, В.Г.Гришанов, В.В. Казаков и В. И. Никитин (53) 621.373.421(088.8) (56) Авторское свидетельство СССР

¹ 813677, кл. Н 03 В 19/00, 07.06.79.

В.В.Смеляков. Цифровая измерительная аппаратура инфранизких частот, М.: Энергия, 1975, с. 124. (54) ФОРМИРОВАТЕЛЬ СИНУСОИДАЛЬНЫХ

СИГНАЛОВ (57) Изобретение относится к радиотехнике. Цель изобретения — повышение точности формирования выходных сигна-. лов ° Формирователь содержит задающий

r-p 1, RS-триггер 2, эл-ты 2И-НЕ 3 и 15, реверсивный счетчик 4, ЦАП 5, блок коммутируемых весовых сопротив„„Я0„„1429281 А1 лений (БВС) б, дешифратор 7, управляемый источник 8 тока, усилитель 9, управляемый инвертор 10, эл-т ИЛИ 11, эл-т HE-И-НЕ 12, счетный триггер 13, ключ 14 и резистор б. На выходе

ЦАП 5 формируется ступенчатое напряжение. При последовательном шунтировании выхода ЦАП 5 соответствующим резистором БВС б уменьшается величина ступеней аппроксимации соответствующей хорды синусоиды, т.е. угол наклона аппроксимируемой прямой, и в устройстве осуществляется последовательное формирование хорд синусоиды, При переключении счетчика 4 из режима суммирования в режим вычитания ключи БВС 6, источника 8 и ЦАП 5 . начинают переключаться в обратном порядке и, следовательно, угол наклона хорд синусоиды изменится на отри". цательный. T. обр,, осуществляются циклы формирования периода синусоидального напряжения, 4 ил.

1429281

Устройство относится к радиотехнике и может быть использовано в устройствах технической диагностики для формирования синусоидальных сигналов. 5

Целью изобретения является повышеНие точности формирования выходных сигналов.

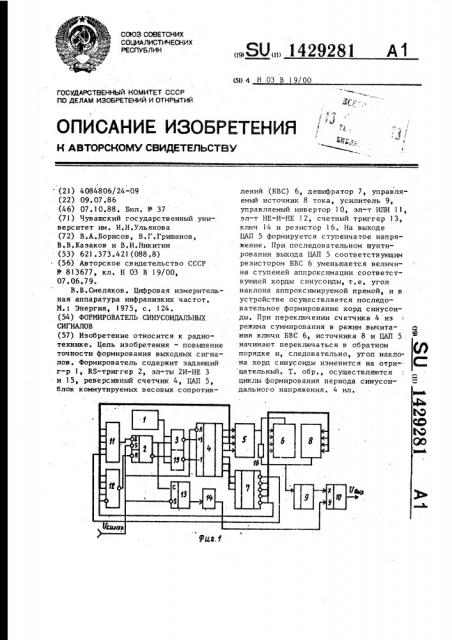

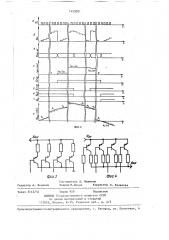

На фиг. 1 представлена структурная электрическая схема формирователя си- 10 нусоидальных сигналов; на фиг. 2 ременные диаграммы, поясняющие рабо ту формирователя синусоидальных curt

1яалов; на фиг. 3 и 4 - примеры прак-!

;тической реализации блока коммутиру, емых весовых сопротивлений и управляемого источника тока соответственно.

Формирователь синусоидальных сиг .;налов (фиг. 1) содержит задающий ге, нератор 1, RS-.òðèããåð 2, первый эле мент 2И-НЕ 3, реверсивный счетчик .РС 4, цифроаналоговый преобразова, тель (ЦАП) 5, блок 6 коммутируемых весовых сопротивлений (БВС), дешифратор 7, управляемый источник 8 тока (УИТ), усилитель 9, управляемый инвертор !О,. элемент ИЛИ 11, элемент

НЕ-.И-НЕ 12, счетный триггер 13, ключ

14, второй элемент 2И-НЕ 1 5, резистор 16, 30

Формирователь синусоидальных сигналов работает следующим образом.

В момент появления потенциала 1 и на входе синхронизации формирователя синусоидальных сигналов, обнуляется PC 4, а счетный триггер 13 и

RS-триггер 2 устанавливаются в единицу. В исходном состоянии на выходе

ЦАП 5 в соответствии с двоичным кодом, поступающим с выхода PC 4, на" пряжение равно нулю. На выходе дешифратора 7, кроме выхода младшего раз. ряда, устанавливаются уровни логической единицы, следовательно, все ключи БВС 6 (фиг. 3) и УИТ 8 (фиг. 4) заперты. Поэтому отсутствует шунтирование выхода ЦАП 5 резисторами БВС 6, а величина добавочного тока, поступающего с выхода УИТ 8 на вход усилителя 9, равна нулю. Аппроксимируется первая хорда синусоиды. С прямого вы«50 хода RC-триггера 2 логическая единица поступает на второй вход первого элемента 2И-HE 3 и импульсы с выхода задающего генератора (фиг, 2 а) поступают на суммирующий вход PC 4, На выходе ЦАП 5 формируется ступенчатое напряжение (фиг. 2 б) . Поскольку

ЦАП 5 обладает внутренним сопротивлением, шунтируя его выход резисторами БВС 6 (фиг. 3), можно уменьшить величину ступеней напряжения прямо пропорционально углам наклона хорд аппроксимируемой синусоиды. После заполнения PC 4 до установки единицы на первом. выходе сигнала старшего разряда (фиг. 2 в) появляется уровень логического нуля на соответствующем выходе дешифратора 7, который вызывает подключение соответствующих резисторов в БВС 6 и УИТ 8. В момент начала аппроксимации второй хорды синусоиды суммарный ток, втекающий в усилитель 9, равен току

УИТ 8 и соответствует первой ступени второй хорды синусоиды (фиг. 2 г), при этом соответствующий резистор

БВС 6 шунтирует выход ЦАП 5, уменьшая величину ступеней аппроксимации второй хорды, т.е. угол наклона аппроксимируемой прямой (фиг. 2 и).

Аналогично формируются остальные хорды синусоиды до момента заполнения выходов сигналов младших разрядов PC 4 и появления логического нуля на выходе старшего разряда дешифратора 7 (фиг. 2 е). Это вызывает появление логического нуля на выходе элемента НЕ"И-НЕ 12, что приводит к появлению логической единицы на инверсном выходе RS-триггера 2 (фиг. 2 ж). РС 4 переходит в режим вычитания, поскольку на вычитающий вход PC 4 начинают поступать импульсы с выхода задающего генератора 1 через второй элемент 2И-НЕ 15. Ключи

БВС Ь и УИТ 8 и ЦАП 5 начинают переключаться в обратном порядке, следовательно, угол наклона хорд сменяется на отрицательный. При обнулении дешифратора 7 и выхода сигналов младших разрядов PC 4 на выходе элемента ИЛИ 11 появляется логический ноль, возвращающий К8-триггер 2 в единичное состояние (фиг. 2 ж), что переводит

PC 4 в режим суммирования. В момент переключения RS-триггра 2 в единичное состояние происходит изменение логического уровня-на выходе счетного триггера 13 (фиг. 2 з). При этом ключ 14 запирается и управляемый инвертор 10 переходит из режима инвертирования в режим повторения. В момент окончания формирования периода синусоидального напряжения следующее переключение RS-триггера 2 из нулевого в единичное состояние возз 142 вращает счетный триггер )3 в исходное состояние. Последующие циклы формирования синусоидального напряжения аналогичны.

Резистор 16 предназначен для уменьшения втекающего в усилитель 9 тока иэ ЦАП 5, что позволяет снизить влияние внутренних нелинейных сопротивлений ключей БВС 6 за счет увеличе" ния сопротивления резисторов БВС 7, а также снизить влияние нагрузки на выходное напряжение ЦАП 5 и УИТ 8.

Формула изобретения

Формирователь синусоидальных сиг" налов, содержащий задающий генератор, RS-триггер, реверсивный счетчик, цифроаналоговый преобразователь, дешифратор, управляемый источник тока, усилитель и управляемый инвертор, причем выходы сигналов старших разрядов реверсивного счетчика соединены с соответствующими входами дешифратора, выходы сигналов младших разрядов реверсивного счетчика соединены с соответствующими входами цифроаналогового преобразователя, выход которого ,через резистор подключен к входу усилителя, выходы дешифратора, кроме выхода младшего разряда, соединены с соответствующими входами управляемого источника тока, о т л и ч а ю щ и й— с я тем, что, с целью повышения.. точности формирования выходных сигналов, введены первый и второй элементы 2И-НЕ, элемент ИЛИ, элемент

НЕ-И-НЕ, счетный триггер, блок ком,мутируемых весовых сопротивлений и ключ, причем выход задающего генератора подключен к первьм входам перво928,1-4 го и второго элементов 2И-НЕ, выходы первого и второго элементов 2И-НЕ соединены соответственно с входами

5 суммирования и вычитания реверсивного счетчика, выход младшего разряда дешифратора соединен с одним входом элемента ИЛИ, другие входы которого соединены с соответствующими входами цифроаналогового преобразователя и неинвертирующими входами элемента

НЕ-И-НЕ, инверсный вход элемента

НЕ-И-НЕ подключен к выходу старшего разряда дешифратора, входы блока коммутируемых весовых сопротивлений объединены с соответствующими входами управляемого источника тока, выход блока коммутируемых весовых сопротивлений объединен с выходом цифро20 аналогового преобразователя, выходы элемента ИЛИ и элемента НЕ-И-НЕ сое цинены соответственно с первым S входом и R-входом RS-триггера, прямой и инверсный выходы которого сое26 динены соответственно с вторым входом первого элемента 2И-НЕ и вторым Входом второго элемента 2И-НЕ, счет ный вход счетного триггера соединен с прямья выходом RS-триггера, выход

3р счетного триггера соединен с входом ключа, выход которого соединен с уп- . равляющим входом управляемого инвертора„ выход усилителя соединен с сигйальньм входом управляемого ин- вертора, выход которого является выходом формирователя синусоидальных сигналов,.второй S-вход RS-триггера, вход обнуления реверсивного счетчиka u S-вход счетного триггера объе40 динены и являются входом сигнала синхронизации формирователя синусоидальных сигналов . 42928 I

ЦРиг 4

Составитель А. Иьппакин

Техрец М.Дидык Корректор О. Кравцова

Редактор А. Борович

Заказ 5142/54 Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4