Умножитель частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и связи и может использоваться в измерительной технике для синтеза опорного сигнала. Цель изобретения - уменьшение времени установления частоты выходного сигнала. Умножитель частоты содержит вычитатель 1, накапливающие сумматоры (не) 2, 3, ЦАП 4, фильтр 5 нижних частот, управляемьй генератор 6, дешифратор 7, ключи 8, 9. На НС 2, 3 подаются коды чисел N,, N соответственно. Эти коды определяют коэф. умножения умножителя част оты tL (). По импульсам входного снгнала, поступающим через ключ 8, в НС 2 происходит накопление с шагом N,. В НС 3 по импульсам выходного сигнала , поступающим через ключ 9, происходит накопление с шагом N. В вычитателе I происходит вычитание накопленных сумм. Код разности (КР) d. по импульсу входного сигнала увеличивается на величину N,, а по импульсу выходного сигнала уменьшается на величину N2. По КР происходит перестройка частоты управляемого генератора 6. Перестройка происходит до тех пор, пока не выравняются скорости накопления в НС 2, 3. КР может изменяться в пределах О d , М, где п - число разрядов на выходе вычитатепя 1. Дешифратор 7 закрывает ключ 8 и открывает ключ 9 при .M, закрывает ключ 9 и открывает ключ 9 при О d; NI и открывает ключи 8, 9 при . N d.M-K,. Такое формирование КР исключает срыв синхронизма на границах диапазона скачкообразного умень-. шения КР. 1 ил. (Л 0 со to 00 со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5g 4 Н 03 В 19/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, " :

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4194092/24-09 (22) 13.02,87 (46) 07.10.88. Бюл. У 37 (71) Белорусский государственный университет им. В.И.Ленина (72) Н.Н.Скриган и О.Э.Шукело (53) 621.374.4(088.8) .(56) Авторское свидетельство СССР

11 1229944, кл. H 03 В 19/00, 22.10.84.

Авторское свидетельство СССР

У 1095345, кл. Н 03 В 19/00, 03.06.82. (54 ) УИНОЖИТЕЛЬ ЧАСТОТЫ (57) Изобретение относится к радиотехнике и связи и может использоваться в измерительной технике для синтеза опорного сигнала. Цель изобретения — уменьшение времени установления частоты выходного сигнала. Умножитель частоты содержит вычитатель 1, накапливающие сумматоры (НС) 2, 3, ЦАП 4, фильтр 5 нижних частот, управляемый генератор 6, дешифратор 7, ключи 8, 9. На НС 2, 3 подаются коды чисел N, N соответственно. Эти коды определяют коэф. умножения умножителя частоты..SU„„1429283 А1 (K=N1/N2) . По импульсам входного сигнала, поступающим через ключ 8, в

НС 2 происходит накопление с шагом

N,. В НС 3 по импульсам выходного сигнала, поступающим через ключ 9, происходит накопление с шагом N . В вычитателе 1 происходит вычитание накопленных сумм. Код разности (КР) d. no

1 импульсу входного сигнала увеличивается на величину N,, а по импульсу выходного сигнала уменьшается на величину Nz По KP происходит перестройка частоты управляемого генератора б.

Перестройка происходит до тех пор, пока не выравняются скорости накопления в НС 2, 3 ° KP может изменяться в пределах 0 й; (М, где М=2"; ив число разрядов на выходе вычитателя 1.

Дешифратор 7 закрывает ключ 8 и открывает ключ 9 при М-N, (8.(M, закрыва.ет ключ 9 и открывает ключ 9 при

0 d 6N< и открывает ключи 8, 9 при

Nz 66 (М-N,. Такое формирование KP исключает срыв синхронизма на границах диапазона скачкообразного уменьшения KP. 1 ил.

1429283

20

N)

К е

1,1

По каждому импульсу входного сигнала, поступающему через первый ключ

8 на управляющий вход первого накапливающего сумматора 2, последний осуществляет суммирование ранее накопленного числа с числом N т.е.

35 накопление с шагом N . По каждому импульсу выходного сигнала, поступающему через второй ключ 9 на управляющий вход второго накапливающего сумматора 3, в нем производится накопление с шагом И2. Вычитатель 1 вычитает из первой накопленной суммы вторую, тогда каждый импульс входного сигнала увеличивает текущее значение кода разности d; на выходе вычитателя 1 на величину N, а каждый импульс выходного сигнала уменьшает его на величину N<. Код разности после преобразования цифроаналоговым преобразователем 4 в аналоговое напряжение через фильтр 5 поступает на управляющий вход управляемого генератора 6 и перестраивает его частоту до тех пор, пока не выравняются скорость накопления в первом и втором

55 накапливающих сумматорах 2 и 3, т.е.

- у 11 t bed) 1 2

Изобретение относится к радиотехНике и связи и может быть использоцано в измерительной технике для син21еза опорного сигнала в синхронных системах контроля состояния роторных машин, Целью изобретения является уменьШение времени установления частоты выходного сигнала.

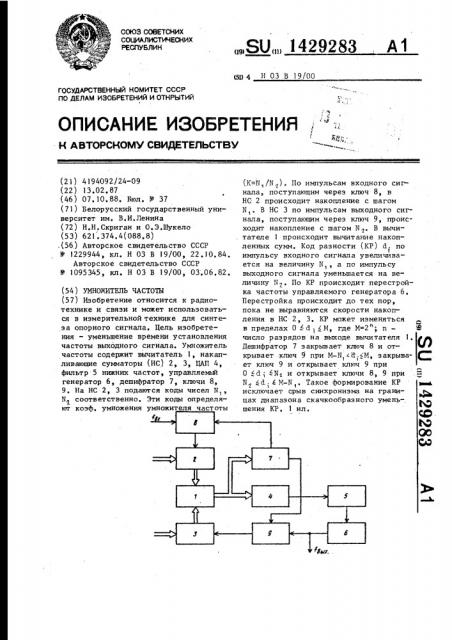

На чертеже приведена структурная электрическая схема умножителя частот ы.

Умножитель частоты содержит вычита 21ель 1, первый и второй накапливаю- 15 плие сумматоры 2 и 3, цифроаналоговый феобразователь 4, фильтр 5 нижних ч астот, упр авляемый генератор 6, дешифратор 7„первый ключ 8 и второй ключ 9.

Умножитель частоты работает слеДующим образом.

На информационные входы первого

И второго накапливающих сумматоров

2 и 3 подаются коды чисел соответственно N, и И, определяющие коэффициент умножейия умножителя частоты или

N и N 6х д

Код раэности d, на выходе вычитателя 1 может изменяться в пределах

0(d с М, где И=2, п — количество разрядов на выходе вычитателя 1, Дешифратор 7 осуществляет управление первым и вторым ключами 8 и 9 таким образом, что при M-N, c d, (М первый ключ 8 закрыт, а второй ключ

9 открыт, при 0 d; N2 второй ключ

9 эакрыт, а первый ключ 8 открыт, при

И d; < М-И„ открыты первый.и второй ключи 8 и 9. Таким образом, íà границах диапазона скачкообразного изменения кода разности, приводящего к срыву синхронизма, не происходит, что способствует сокращению времени установления частоты выходного сигнала при изменениях частоты сигнала на входе умножителя частоты.

Формула из о брет ения

Умножитель частоты, содержащий последовательно соединенные первый накапливающий сумматор, вычитатель и цифроаналоговый преобразователь, последовательно соединенные фильтр нижних частот и управляемый генератор, а также второй накапливающий сумматор, выход которого соединен с вторым входом вычитателя, о т л и ч а юшийся тем, что, с целью уменьшения времени установления частоты выходного сигнала, введены дешифратор, а также первый и второй ключи, при этом выходы первого и второго ключей соединены с управляющими входами соответственно первого и второго накапливающих сумматоров, управляющие входы первого и второго ключей соединены соответственно с первым и вторым выходом дешифратора, вход которого соединен с выходом вычитателя, выход цифроаналогового преобразователя соединен с входом фильтра нижних частот, информационный вход второго ключа соединен с выходом управляемого генератора, а информационный вход первого ключа является входом умножителя частоты.