Синхронный детектор

Иллюстрации

Показать всеРеферат

Изобретение относится к элек тронным измерительным устройствам в автоматике. Цель изобретения - повьппение точности демодуляции при случайных фазовых сдвигах. Устройство содержит динамическое запоминающее устр-во 1, формирователь импульсов 2, дифференцирующую цепь 3, двухполупериодный выпрямитель 4, г-р опорного сигнала 5, фазовращатель 6. Для достижения цели введены фазовый детектор 7, нуль-компаратор 8 и D-триггер 9. Нуль-компаратор 8 в данной схеме является по существу формирователем широких (длительностью полупериода) импульсов из выходного напряжения фазовращателя 6. Если случайный фазовый сдвиг между входным и опорным сигналами не превышает t90 , то с помощью фазового детектора 7 и фазовращателя 6 компенсируется и на входах D-триггера 9 сохраняется первоначально установленное смещение фаз поступающих сигналов. Если фазовый сдвиг превышает t90°, но не достигает fl80 , то устойчивая работа устр-ва обеспеа D чивается за счет большой длительноети (равной полупериоду входного сигнала ) разрешающих импульсов, поступакацих на D-вход D-триггера 9. 3 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU 1429287 А 1 (gl) 4 H 03 D l /22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

$ gM 4

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО«ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2 1) 4102937/24-09 (22) 13.08.86 (46) 07.10.88. Бюл. N -37 (71) Институт экспериментальной метеорологии (72) В.М ° Чекрыжов (53) 621,376,23(088.8) (56) Авторское свидетельство СССР

1l 647839, кл. Н 03 D 1/22, 1975. (54) СИНХРОННЫЙ ДЕТЕКТОР (57) Изобретение относится к электронным измерительным устройствам в автоматике, Цель изобретения — повышение точности демодуляции при случайных фазовых сдвигах. Устройство содержит динамическое sапоминающее устр-во 1, формирователь импульсов 2, дифференцирующую цепь 3, двухполупериодный выпрямитель 4, r-p опорного сигнала 5, фаэовращатель 6. Для достиже ния цели в вед ены фа э о вый дет е ктор 7, нуль-компаратор 8 и D-триггер

9. Нуль-компаратор 8 в данной схеме является по существу формирователем широких (длительностью полупериода) импульсов из выходного напряжения фазовращателя 6. Если случайный фазовый сдвиг между входным и опорным сигналами не превышает +90, то с поо мощью фазового детектора 7 и фаэовращателя 6 компенсируется и на входах

D-триггера 9 сохраняется первоначально установленное смещение фаз поступающих сигналов. Если фазовый сдвиг превышает +90, но не достигает 180, о о то устойчивая работа устр-ва обеспе- д чивается эа счет большой длительнос-тн (ранней полуперноду нходного онг- (/) нала) разрешающих импульсов, поступающих íà D-вход D-триггера 9. 3 ил. С

1429287

Изобретение относится к электронным измерительным устройствам в автоматике и предназначено для преобразования высокочастотных амплитудно-мо5 дулированных сигналов различных датчиков в низкочастотные, воспринимаемые инерционными измерительными или исполнительными устройствами, Цель изобретения — повышение точ- 10 ности демодуляции при случайных фазо:вых сдвигах.

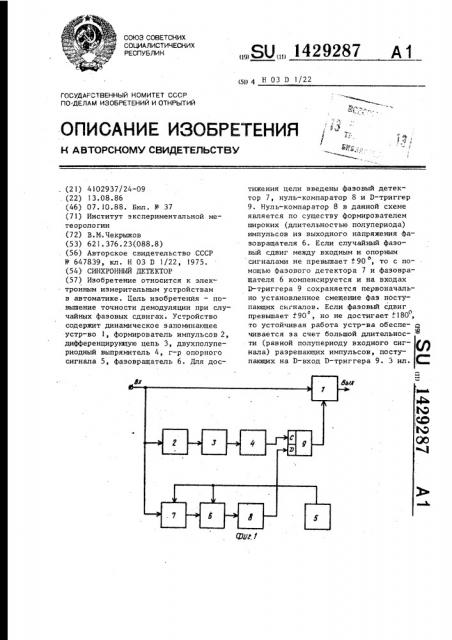

На фиг.1 изображена структурная, электрическая схема синхронного детектора; на фиг.2 — временная диаг- 15 paMMa его работы; на фиг.3 — переда точная характеристика фазовращателя, Синхронный детектор содержит дина:мическое запоминающее устройство . (ДЗУ) 1, формирователь 2 импульсов, 20 дифференцирующую цепь 3, двухполупериодный выпрямитель 4, генератор 5 опорного сигнала, фазовращатель 6, . фазовый детектор 7, нуль-компаратор

8, D-триггер 9. 25

Синхронный детектор работает следующим о бр аз ом .

Входной сигнал (фиг. 2а) подается на сигнальный вход ДЗУ 1 и одновременно на схему, состоящую из после- 30 довательно соединенных формирователя

2 импульсов, дифференцирующей цепи

3 и двухполупериодного выпрямителя 4.

Основным назначением укаэанной схемы является формирование иэ входного сигнала узких импульсов, возникающих в моменты перехода входного напряжения через нуль (фиг.2в) . Эти импульсы подаются на тактирующий С-вход

D-триггера 9, который срабатывает, 40 если в это время íà его D— - входе установлен высокий потенциал (фиг.2г).

На управляющем входе ДЗУ (фиг.2д) появляется высокий потенциал, который разрешает прохождение входного сигна- 45 ла в момент его перехода через нуль.

Следующий импульс на С-входе D-триггера 9 возвращает 11-триггер в исходное состояние, так как к этому времени на его D-входе устанавливается ну50 левой потенциал. На управляющий вход

ДЗУ 1 вследствие этого тоже подается нулевой потенциал, который запрещает дальнейшее прохождение входного сигнала через него. Таким образом D— триггер 9 разрешает прохождение через ДЗУ 1 только одной положительной или отрицательной полуволны входного сигнала, причем точно в те моменты времени, когда входной сигнал меняет свою полярность и по величине практически равен нулю. В результате на выходе синхронного детектора выделяется медленно меняющийся сигнал положительной или отрицательной полярности, несущий информацию об амплитудных изменениях входного сигнала (фиг,2е). Смена полярности выходного сигнала синхронного детектора вызывается обычно скачкообразным изменеа нием фазы входного сигнала на 180 что при нормальной работе схемы свидетельствует о равенстве в данный момент величины измеряемого физического параметра ее эталонному значению. Устойчивая работа синхронного детектора возможна при условии, что сигналы на входах D-триггера 9, сформированные из входного и опорного сигналов (фиг.2б), имеют между собой сдвиг фаз, не превышающий +90, при фактических сдвигах фазы входного сигнала относительно опорного, колебв лющихся в пределах О. + 180 . Для это— го на первый вход фазового детектора

7 подается входной сигнал синхронного детектора, а на второй вход— опорный сигнал той же частоты от генератора опорного сигнала S. Выходное напряжение фазового детектора 7 поступает на управляющий вход фазовращателя 6, на сигнальный вход которого подается напряжение генератора опорного сигнала 5. На выходе фазовращателя 6 вырабатывается переменное напряжение, сдвинутое по фазе относительно опорного на величину, определяемую уровнем выходного напряжения фазового детектора 7. Нуль-компаратор 8 в данкой схеме является формирователем широких (длительностью полпериода) импульсов из выходного напряжения фазовращателя 6. Если под действием каких-либо возмущающих факторов появляются значительные сдвиги фаз входного сигнала относительно опорного, то прежде всего они с помощью фазового детектора 7 преобразуются в пропорциональное напряжение на

его выходе, которое поступает на управляющий вход фазовращателя 6. Сдвиг фазы выходного напряжения фазовращателя 6 изменяется линейно в зависимости от управляющего напряжения о только до 90, а далее остается постоянным (фиг.3). Таким образом, если случайный фазовый сдвиг между вход1429287

15 е.ным и опорным сигналами не превышает

+90, то он с помощью фазового детектора 7 и фазовращателя 6 компенсируется и на входах D-триггера 9 сохраняется первоначально установленное смещение фаз поступающих сигналов.

Если под действием возмущений сдвиг фазы между входным и опорным сигналами превышает + 90, но не достигает

+180, то устойчивая работа синхронного детектора обеспечивается sa счет большой длительности (равной полпериода входного сигнала) разрешающих импульсов, поступающих на 0вход D-триггера 9. Временные диаграммы для сдвига фаз ЛЦ = 135 приведены на фиг.2ж,з,и,к,л,м соответст. венно.

Фор мула и з о бр е т ения

Синхронный детектор, содержащий динамическое запоминающее устройство, сигнальные вход и выход которого яв- 25 ляются входом и выходом синхронного детектора соответственно, последовательно соединенные формирователь импульсов, дифференцирующую цепь и двухполупериодный выпрямитель, а также генератор опорного сигнала и фазовращатель, отличающийся тем, что, с целью повышения точности демодуляции при случайных фазовых сдвигах, в него введены фазовый детектор, нуль-компаратор и D-триггер, причем вход формирователя импульсов и первый вход фазового детектора соединены с входом синхронного детектора, а выход фазового детектора через последовательно соединенные фазовращатель и нуль-компаратор соединен с информационным входом D-триггера, тактирующий вход которого соединен с выходом, двухполупериодного выпрямителя, а выход соединен с управляющим входом динамического запоминающего устройства, причем выход генератора опорного сигнала соединен с вторым входом фазового детектора и сигнальным входом фазовращателя.

1429287

Составитель А.Колосов

Редактор Н.Лазаренко Техред "1..Дидык Корректор В.Романенко

Заказ 5142/54 Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Проиэводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4