Генератор импульсов ступенчатой формы

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной текинке и может найти применение в радиолокации для формирования управляющих напряжений. Цель изобретения - повышение быстродействия устройства при одновременном расширении функциональных возможностей. Устройство содарткит генератор 1 тактовых импульсов, блоки 2.1. 2.2. ключей, рвзист1шные матрицы 3.1. 3.2, операционный усилитель 4. В устройство введены блоки ключей 2.3...2.К, резистивные матрицы 3.3...3.К, регистр 5 числа и блоки 7.1....7.К. памяти. В регистр 5 записывается информация в двоичном коде. На выходе каждой резистивной матрицы З.1.. З.К формируется ступенчато изменяющийся сигнал, если в соответствующем разряде регистра 5 записана единица. Знаковые разряды регистра 5 определяют знак изменения выходного напряжения . Быстродействие повьппается благодаря тому, что в блоках памяти 7.1... 7.К отсутствуют переходные процессы. 1 -з.п. ф-лы, 3 ил. X ., щтргтр (Л с 4 to со 00 о САЭ

СОЮЗ СОВЕТСКИХ

COUHAЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (!9) (11) (51) 4 Н 03 К 4 02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТЯЕННЫЙ КОМИТЕТ СССР

flo делАм изоБРетений и ОткРытий (21) 4213051/24-21 (22) 19.03.87 (46) 07.10.88. Бюл. У 37 (72) Л.И.Грибанов, Г.С.Колос и В.С.Никитин (53) 621.397 (088.8) (56) Авторское свидетельство СССР

У 729824, кл. Н 03 К 4/02, 1979.

Авторское свидетельство СССР

У 875600, кл. Н 03 К 4/02, 1980. (54) ГЕНЕРАТОР ИИПУЛЬСОВ СТУПЕНЧАТОЙ

ФОРМЫ (57) Изобретение относится к импульсной технике и может найти применение в радиолокации для формирования управляющих напряжений. Цель изобретения — повышение быстродействия устройства при одновременном расширении функциональных возможностей.

Устройство содержит генератор 1 тактовых импульсов, блоки 2.1. 2.2. ключей, резистивные матрицы 3.1. 3.2, операционный усилитель 4. В устройство введены блоки ключей 2.3...2.К, резистивные матрицы 3.3...3.К, регистр 5 числа и блоки 7.1....7.К. памяти. В регистр 5 записывается информация в двоичном коде. На выходе каждой резистивной матрицы 3.1..

3,К формируется ступенчато изменяю" щийся сигнал, если в соответствующем разряде регистра 5 записана единица.

Знаковые разряды регистра 5 определяют знак изменения выходного напряжения. Быстродействие повышается благодаря тому, что в блоках памяти

7.1...7.К отсутствуют переходные процессы. 1 з.п. ф-лы, 3 ил.

1 429303 2

Изобретение относится к импульсной технике и может быть использоиано в радиолок ации для фо рмиров ания управляющих напряжений.

Целью изобретения является повышение быстродействия устройства при одновременном расширении функциональных возможностей.

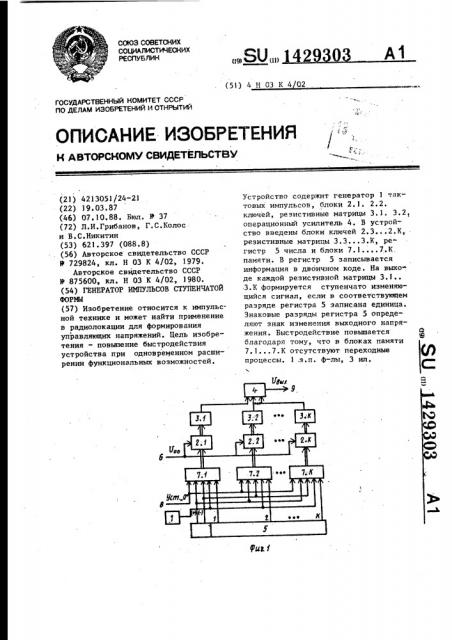

На фиг.l приведена структурная схема устройства; на фиг.2 - струкурная схема блока памяти; на фиг.3— ременные диаграммы.

Генератор содержит генератор 1 актовых импульсов, с первого по К-й

° ° ° ° ° ° локи 2 ° )...2.К ключей, с первой по

-ю резистивные матрицы 3.1....3.К, операционный усилитель 4, регистр 5 числа, шину 6 опорного напряжения, первого по К-й блоки 7.1...7.К 20 памяти, шину 8 установки "О" и выходную шину 9.

Входы сброса всех блоков 7.1...7.Ê соединены с шиной,8, основные входы— с выходом генератора 1, знаковые 25

Входы †.со знаковыми выходами регистРа 5. Управляющий вход каждого блока

7.i соединен с соответствующим выходом регистра 5, а выход — через блок 2.i и резистивную матрицу З.i — - 30

С соответствующим входом операционного усилителя, выход которого соединен с выходной шиной 9. Входы опорного напряжения всех блоков 2.1..2.К соединены с шиной 6.

Каждый блок 7.(фиг.2) содержит с первого по Б-й элементы 10.1...10.N памяти, с первого по N H суммирующие

Элементы И 11.1...11.N,. с первого по

Я-й вычитающие элементы И !2.1..12.N, с первого по N-й элементы ИЛИ 13, 1..

)З.N, триггер 14, с первого по девя тый элементы И )5-23 и (N+))-A элемент ИЛИ 24.

ПРямые выходы элементов 10.1..10.0 45 образуют разряды выхода блока 7 и сое 1инены кроме элемента IО.N, с первыми входами суммирующих элементов И следующего разряда. Инверсные выходы

Элементов 10. 1... 10. N соединены через суммирующие элементы И 11.1..11.N того жеразряда сосвоим же единичным . входом и, кроме элемента 10.), через

9ычитающий элемент И 12.1...12.N-! с нулевым входом предыдущего элемента

10. 1... 10. N-1 ° Вторые входы элементов ИЛИ 13.1...)З.N объединены и об)фазуют вход сброса блока 7. Прямой выход первого !О.! и инверсный выход

N-ro IО.N элементов соединены с первым и вторым входами первого элемента И 15, Инверсный вьиод первого

)0.1 и прямой выход И-ro )Î.N элементов соединены с первым и вторым входами второго элемента И 16. Выходы первого 15 и второго 16 элементов И соединены с первыми входами третьего 17 и четвертого 18 элементов И, вторые входы которых являются знаковыми входами блока 7, а выходы соединены с единичным и нулевым входами триггера 14, прямой и инверсный выходы которого соединены с первыми входами соответственно пятого

19 и шестого 20 элементов И, вторые входы которых объединены и соединены с синхронизирующими входами всех элементов 10.1...)О.М памяти и вьиодом седьмого элемента И 21, первый и второй входы которого являются соответственно тактовым и управляющим входами блока ?. Первые входы восьмого 22 и девятого 23 элементов

И соединены соответственно с прямым и инверсным выходами N-ro элемента .

IО.N вторые входы объединены и соединены с инверсным выходом триггера 14, а выходы соединены с входами (N+))-ro элемента ИЛИ 24, выход которого соединен с первым входом

N-го вычитающего элемента И )2.

Выход пятого элемента И 19 соединен с вторым входом первого суммирующего элемента И Il.l и третьими входами остальных суммирующих элементов И

il.2...11.N. Выход шестого элемента

И 20 соединен с вторыми входами вы.читающих элементов И 12.1...12.N, Каждая из К резистивных матриц

3.1...3.К представляет собой набор из N резисторов. Номинал резисторов первой матрицы 3.1, например, соответствует R номинал резисторов второй матрицы — 2R и так далее, или номинал резисторов первой Матрицы

3.1 соответствует R, а номиналы нагрузочных резисторов в других разрядах отличаются на величину, кратную основанию выбранной системы счисления. Количество разрядов регистра 5 и количество элементов памяти в блоках 7, а также номиналы резисторов резистивных матриц 3 определяются диапазоном изменения величины выходного сигнала и требуемой точностью представления напряжения з 142 в аналоговой форме (ступенчатого на. пряжения).

Генератор работает следующим образом.

Генератор обеспечивает работу в двух режимах: управления и генерации.

Перед началом работы все триггеры в блоках. 7 и регистре 5 обнуляются.

Процессы рассматриваем, используя положительную логику, когда более высокому уровню соответствует логическая единица. В исходном состоянии в регистр 5 записывается информация в двоичном коде. В режиме управления команда "Сложение" или Вычитание" формируется по признакам знаковых разрядов регистра 5, которые передаются на вторые входы элементов И 17 . и 18, При формировании команды "Сложение" (это соответствует коду знаковых разрядов 10 ) высокий логичес- кий уровень прикладывается к второму входу элемента И 17. Все элементы

10.1...10.N находятся в нулевом состоянии, поэтому к входам элемента И

15 прикладывается высокий уровень.

Выходной сигнал элемента И 15 (вьсокий логический уровень) воздействует на первый вход элемента И 17, на выходе которого также формируется высокий логический уровень, который, воздействуя на единичный вход триггера 14, устанавливает последний в единичное состояние, разрешающее напряжение прикладывается по первому входу к элементу И 19. Если в данном

i-M разряде регистра 5 записана единица, то высокий уровень прикладывается к второму входу первого элемента И 21. Первый импульс генератора 1 (фиг. За) поступает через элементы И 21 и 19 и воздействует на один из входов элементов И 11.1..-.

11Л. Этот импульс проходит только через элемент И 11.1 остальные, ука-: занные элементы И закрыты низким уровнем с прямого выхода предыдущего элемента памяти и устанавливает первый элемент 10.1 в единичное состояние. На синхронизирующий вход элементов 10.1...10Л при этом поступают импульсы генератора I с выхода элемента И 21. Высокий уровень с прямого выхода элемента 10.1 воздействует на управляющий вход соответствующего ключа блока 2, на второй вход которого подается напряжение с шины 6. При этом на соответствующем

9303 4 резисторе резистняной матрицы З.i c.îðмируется ступенька напряжения.

Высокий уровень с прямого выхода элемента 1 С.l воздействует на один из входов элемента И Il.2, ïðè этом второй импульс генератора 1 обеспечивает переключение только второго элемента 10.2 в единичное состояние, в результате формируется вторая ступенька нарастающего ступенчатого напряжения (фиг. Зб). Третий импульс генератора l устанавливает в единичное состояние следующий элемент 10.3 памяти, N-й импульс генератора 1 элемент IО.N в единичное состояние.

Таким образом, все элементы памяти рассматриваемого блока 7.i находятся в единичном состоянии, Аналогичным образом происходят процессы в других блоках 7 при условии, когда к данному блоку 7 с регистра 5 прикладывается высокий уровень. Отличие заклю"; чается в том, что амплитуда ступенек

25 формируется в )-й резистивной матрице в соответствии с номиналами резисторов данной матрицы (фиг.3, h u

hz), Если к j-му блоку 7 j с регистра

5 прикладывается низкий уровень, то

ЗО данный j-й блок 7 j «е принимает участия в работе устройства. Объединенные выходы резисторов резистивных матриц 3.1...3.К подключены к входам операционного. усилителя 4, на выходе

35 которого формируется результирующее возрастающее напряжение ступенчатой формы.

В режиме управления при формировании команды "Вычитание" 1это соответствует коду знаковых разрядов OI) высокий логический уровень прикладывается к второму входу элемента

И 18, Все элементы 10.1..10.N находятся в единичном состоянии, высокий

4 логический уровень прикладывается к

45 элементу И 16, выходной высокий уровень которого воздействует на первый вход элемента И 18, высокий уровень с выхода которого устанавливает триггер 14 в нулевое состояние, и раз50 решающее напряжение с его инверсного выхода прикладывается к одному из входов элементов И 20, 22 и 23. Высокий уровень с прямогб выхода элемента IО.N воздействует через элементы

И 22 и ИЛИ 24 на один из входов элемента И 12,N. Импульс генератора 1 через элементы И 21 и 20 воздействует на элементы И 12.1...12Ë и обеспе5 14 чивает переключение через элементы

И 12.N и ИЛИ 13Л только одного элемента 10.N в.нулевое состояние.

Очередной импульс генератора 1 переключает следующий элемент 10.N-1 йамяти в нулевое состояние и так: далее,, после N-ro импульса генератора 1 переключается в нулевое состояние элемент 10.1, а все элементы памяти блока 7.i находятся в нулевом состоянии. Аналогично по команде "Вычитание" происходят процессы и в дру1 их блоках 7.1...7.К при наличии дцницы в соответствующем разряде регистра 5. В итоге на выходе onePàöèoííoãî усилителя 4 формируется результирующее убывающее напряжение ступенчатой формы (фиг. 36). Длительность ступеньки в данном случае опре- деляется периодом следования импульсов генератора 1.

Рассмотрим режим генерации. В этом ежиме в знаковых разрядах регистра записывается код 11 и к вторым входам логических элементов И 17 и 18 прикладывается высокий логический уровень. Импульсом сброса все элементы 10.1...10.N в блоках 7,1...7.К обнуляются, а в регистр 5 записывает<>я определенный двоичный код. Высокие уровни с инверсных выходов элементов

10.1 и 10.N, воздействуя на элементы

И 15 и 17,-обеспечивают переключение ч, риггеров 14 в единичное состояние.

При наличии единицы (выооного уровняу в данном разряде регистра 5 в рассматриваемый блок 7.i каждым импульсом генератора 1 обеспечивается поа чередное установление элементов памяти в единичное состояние, начиная с элемента 10.1. Когда N-й элемент

1 О.N N-м импульсом генератора 1 уста навливается в единичное состояние, высокие уровни прямых выходов элементов 10.1 и 10.N через элементы И 16

al 18 осуществляют переключение триггера 14 в нулевое состояние. При э том поочередно, начиная с элемента

10.N устанавливаются под воздействием импульсов генератора 1 в нулевое состояние ace элементы 10.1...10.N.

Дуралее процессы повторяются, формируется нарастающее напряжение, .затем убывающее ступенчатое напряжение и т.д. Изменяя двоичный код в регистре

5, можно s широких пределах изменять величину ступеньки (фиг. Зв, hz II Ьд) что расширяет функциональные возмож29303 что, с целью повыщения быстродействия устройства при одновременном расширении функциональных возможностей, в.

25 ности. Форма выходного напряжения в режиме генерации отличается от формы выходного напряжения в режиме управления отсутствием верхнего пьедестала. На фиг.3 условно изображено только семь ступенек. установление многоразрядного двоичного кода в регистр 5 происходит, например, с выходного устройства ЭВМ либо с помощью па-.;ели набора параметров.

Известные устройства осуществляют преобразование кода в аналоговое напряжение, а двоичный код получают путем вычислений в накопительных элементах, например счетчиках, сумматорах. Одним из недостатков указанн . х устройств является то, что быстродействие ограничено временем переходных процессов, протекающих при вычислениях. В предлагаемом устройстве в блоках 7 переносы из младших разрядов в старшие отсутствуют, благодаря чему быстродействие вышее.

Ф о р м у л а и з о б р е т е н и я

1. Генератор импульсов ступенчатой формы, содержащий генератор тактовьх импульсов, первый и второй блоки ключей, входы опорного напряжения ксторых соединены с шиной опорного напряжения, а выходы соответственно через первую и вторую резистивные матрицы подключены к первому и второму входам операционного у силителя, выход которого соединен с выходной шиной, отличающийся тем, него введены с третьего по К-й блоки ключей, с третьей по К-ю резистивные матрицы, с первого по К-й блоки памяти и регистр числа, каждый из знаковых выходов которого подключен к знаковому входу соответствующего блока памяти, а выход каждого разряда соединен с управляющим входом соответствующего блока памяти, вы- . ход каждого третьего по К-й блока памяти через последовательно включенные соответствующий блок ключей и резистивную матрицу подключены к соответствующему входу операционного усилителя, выходы первого и второго блоков памяти соединены с входами пер вого и второго блоков ключей соответственно, причем входы опорного на1429303

Уст.„О"

tu,а2

I \ пряжения с третьего по К-й блоков ключей соединены с шиной опорного напряжения, а выход генератора тактовых импульсов подключен к так"".овым

1 входам всех блоков памяти, входы сброса которых соединены с шиной устаHGBKH "0 °

2. Генератор по, п.1, о т л и— ч а ю шийся тем, что каждый из блоков памяти содержит с первого по N-й элементы памяти, суммирующие и вычитающие элементы И и элементы

ИЛИ, причем прямой выход каждого из элементов памяти является выходом соответствующего разряда блока памяти и для всех разрядов, кроме N-го, подключен через суммирующий элемент

И следующего разряда к единичному входу следующего элемента памяти, а инверсный выход каждого из элементов памяти соединен через вычитающий элемент И того же разряда с их же прямыми входами и для всех разрядов, кроме первого, через вычитающие элементы И и элементы ИЛИ с нулевыми входами младшего на единицу элемента памяти, вторые входы элементов ИЛИ объединены и образуют вход сброса, а прямой выход первого и инверсный выход N-го элементов памяти соединены с первым и вторым входами первого элемента И, инверсный выход первого !

: и прямой выход N-го элементов памяти соединены с первым и -вторым входами второго элемента И, выходы первого и второго элементов И соединены с первыми входами третьего и четвертого элементов И, вторые входы которых являются знаковыми входами блока памяти, а выходы соединены с.единичным и нулевым входами триггера, прямой и инверсньп) выходы которого соедине" ны с первыми входами соответственно пятого и шестого элементов И, вторые входы которых соединены с синхронизирующими входамч всех элементов памяти и выходом седьмого элемента И, первый и второй входы которого являются соответственно тактовым и управляющим входами блока памяти, при этом первые входы восьмого и девятого элементов И соединены соответст- венно с прямым и инверсным выходами

И-ro элемента памяти, вторые входы объединены и соединены с инверсным

2Б выходом триггера, а выходы соединены с входами (Я+1)-го элемента ИЛИ, выход которого соединен с первым входом N-го вычитающего элемента И, выход пятого элемента И соединен с

ЗО вторым входом первого и третьими входами остальных суммирующих элемен" тов И, а выход шестого элемента И соединен с вторыми входами всех вычитающих элементов И.

1429303

Составитель А. Смирнов

Редактор И.Шулла Техред,Л. Сердюкова Корректор О. Кравцова

Заказ 5143/55

Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5!!роизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4