Матричный коммутатор

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой коммутационной технике и может быть использовано в устройствах многоканальной коммутации с запомина нием управляющих программ. Целью :- изобретения является расширение функциональных возможностей и увеличение производительности коммутатора. Для достижения поставленной цели в устройство , содержащее-матрицу коммутационнйх элементов I, каждый из которых содержит К триггеров и МДП-транзисторов, дополнительно введены входное 2 и выходное 3 устройства выбора , а в каждый коммутационный элемент 1 введено дополнительно (К-2-) D-триггера и (К-1) МДП-транзисторов. При этом входное устройство выбора содержит М групп по К элементов 2И 10, а выходное устройство выбора со г ( (Л с

союз СОВетсних соцИАлистичЕсних

ЖСПУВЛИН (o H 03 К 17/00

Я

Д р, ГОсудАРстВенный ИОмитет сссР по-делив изОБРетений и ОтнРытий

{21) 4180994/24"21 (22) 13. 01. 87 (46) 07.10.88. Бюл. Р 37 (72) К.А.Дедюлин, А.В.Каляев, P.Ñ.Кильметов, Е.Б.Механцев, P.À.Лашевский, Г.В.Рысухин, В.С.Хорин, В.П.Цветов и А.Г.Краснопольский (53) 621.382 (088.8) (56) Авторское свидетельство СССР

В 1075409, кл. Н 03 К 17/00, 15.0Э.82.

Авторское свидетельство СССР

У 1102038, кл. Н 03 К 17/04, 21.04.83. (54) МАТРИЧНЫЙ КОММУТАТОР (57) Изобретение относится к цифровой коммутационной технике и может быть использовано в устройствах мнс, гоканальной коммутации с запомина» нием управляющих программ. Целью: изобретения является расширение функциональных воэможностей и увеличение производительности коммутатора. Для достижения поставленной цели в устройство, содержащее матрицу коммутационньтх элементов l каждый иэ которых содержит К триггеров и МДП-транзисторов, дополнительно введены входное 2 н выходное 3 устройства выбора, а в каждый коммутационный элемент 1 введено дополнительно (К-2-)

0-триггера и {K-1) МДП-транзисторов.

Ф

Прн этом входное устройство выбора р содержит М групп по К элементов 2И

10, а выходное устройство выбора со!

429308 держит H логических элементов К 2И/

/ИЛИ 13. Благодаря введению дополнительных запоминающих и коммутирующих элементов переход от одного состояния настройки матрицы к другому осуЩествляется за один такт с возмож1

Изобретение относится к области цифровой коммутационной техники и может быть использовано в устройствах многоканальной коммутации с запоминанием управляющих программ.

Цель изобретения — расширение ф нкциональных возможностей и увелич ние производительности коммутатора

I п .тем введения входного и выходного устройств выбора, а также введения 1С: в коммутационный элемент матрицы дополнительных запоминающих и коммутирующих элементов, благодаря которЫм переход от одного. состояния матрицы к другому осуществляется за один15 та кт с возможностью сохранения информации о предыдущем состоянии, вы бор программы настройки осуществляется произвольно, а сама настройка производится во время работы коммута- 20 тора по одной из программ настройки.

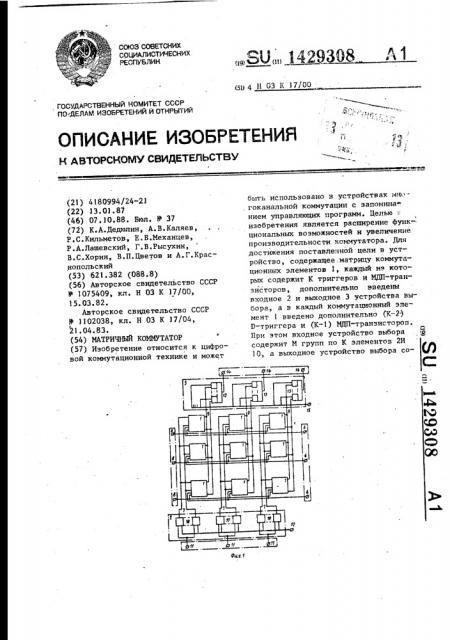

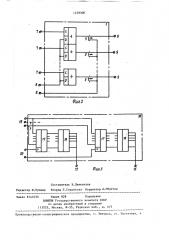

На фиг.l приведена функциональная схема матричного коммутатора; на фиг.2 -. принципиальная схема коммутационного элемента; на фиг.3 — прин- 25 ципиальная схема блока управления.

Матричный коммутатор содержит матрицу NyN коммутационных элементов

1, входное 2 и выходное 3 устройства выбора.

Коммутационный элемент I содержит

К D -триггеров 4 .и соответствующее число МДП-транзисторов 5. D-входы

D-триггеров 4 объединены и подключе" ны K соответствующей шине 6 выбора З5 строки, а выходы — к затворам соответствующих МДП-транзисторов 5. С-входы 9-триггеров 4 подключены к соответ< .твующим входным шинам 7 столбца, число которых в каждом столбце равно 40 числу D-триггеров в каждом коммутационном элементе 1, т.е. равно К.

Истоки МДП-транзисторов 5 в каждой строке объединены и подключены к ностью сохранения информации о предыдущем состоянии, при этом выбор программы настройки осуществляется произвольно, а сама настройка производится во время работы коммутатора., 1 з.п. ф-лы, 3 ил. соответствующей входной шине 8 комму-. татора, а стоки каждого из МДП-транзисторов 5 коммутационных элементов

1 в каждом столбце матрицы подключены к соответствующей выходной шине

9 столбца, число которых в столбце также равно К.

Выходное устройство 2 выбора содержит М групп по К элементов 2 И

10 в каждой, первые входы которых в каждой группе объединены и подключены к соответствующим шинам 11 выбора столбца. Вторые входы одноименных элементов 2И всех групп объединены и подключены к соответствующим входным шинам 12 настройки. Выходное устройство 3 выбора содержит М логи" ческих элементов Кх2И/ИЛИ 13, выходы которых подключены к выходным шинам 14 коммутатора. Первые входы одноименных элементов 2И всех М логи.ческих элементов 13 объединены и подключены к соответствующим выходным шинам 15 настройки, число которых . также равно К. Вторые входы тех же элементов 2И каждого из М логических элементов 13 подключены к соответствующим выходным шинам 9 столбца.

Блок 16 управления содержит два параллельных регистра 17 и два дешифратора 18. Входы регистров 17 подключены к шинам 19 номера матрицы, а выходы — к входам дешифраторов 18. скисло входов и выходов регистров 17 и дешифраторов 18 равно 1ng

Коммутатор работает следующим образом.

В режиме настройки в регистр 17 записывается код коммутации. Для

142

9308 этого на шины 19 номера матрицы подается двоичный код, а на один из командных входов 20 — сигнал разрешения. При этом одна из K входных шнн 12 настройки переходит в единичное состояцие. Этот сигнал открывает в к-.-,ждой группе элементов 2И !0 один иэ элементов 2И, разрешая прохожде.-..ие сиги;::ла выбора . толбца шин на входные шины ? . толбца. C помощью этого сигнала и сигнала с шины 6 выбора строки в один из К триггеров данного столбца записывается логическая "1", а в остальные — логический "0".

Таким образом, устанавливается соединение с помощью МДП-транзистора 5 одной из входных шин 6 строки с одной из выходных шин 9 столбца.

Данная процедура повторяется К раэ для каждой строки матрицы.

В режиме передачи во второй параллельный регистр 17 также записы-. вается нбмер коммутационной матрицы, через которую будет осуществляться передача коммутируемых сигналов. При этом одна из К выходных шин 15 настройки переходит в единичное состояние, что позволяет передать сигнал логической "1" с соответствующего

D-триггера 4 коммутационного. элемента 1 через один и К элементов 2И логического элемента 13 на выходную шину 14 коммутатора.

Таким образом, в режиме передачи реализуется только одна из К комбинаций коммутации. Переход к другой комбинации коммутирующихся шин 8 и

14 осуществляется за один такт путем изменения кода на шинах 19 номера матрицы. При этом информация о соединениях в других комбинациях коммутации сохраняется, возможно повторное обращение через любое число тактов.

Настройка матрицы на коммутацию в новой комбинации шин 8 и 14 может осуществляться одновременно с режимом передачи.

Формула изобретения

1. Матричный коммутатор, содержащий матрицу НхИ коммутационных элементов, каждый из которых содержит два D-триггера и ИДП-транзистор, исток которого соединен с входной шиной данной строки, а затвор подключен к выходу первого D-триггера, отличающийся тем, что, с целью расширения функциональных возможностей и увеличения производительности коммутатора, в него H .çåäå ы входное и выходное устройства выбора, а в катльп коммутационнь и злеменT o o HHT ;i h BBeäåíû (K-2)

13- григгеров и (К-1) ИДП-транзисторов, затвор каждого нз которых соединен с вь-ходом соответствующего D òðèãгера, вк.;юная уже имеющийся D-триггер, а истоки которых соединены с входной шиной соответствующей строки, D-входы всех триггеров коммутационных элементов данной строки подключе" ны к соответствующей шине выбора данной строки, входное устройство вы4

15 число которых также равно К, а вторые входы тех же элементов 2И каж40 дого иэ М логических элементов

Кх2И/ИЛИ подключены к соответствующим выходным шинам столбца каждая иэ которых соединена со штоками соответствующих ИДП-транзисторов коммутационных элементов данного столбца, при" чем К равно или больше двух.

2. Коммутатор по п.1, о т л и— ч а ю шийся тем, что входные и выходные шины настройки являются выходами соответствующих дешифраторов, 45

50 входы которых соединены с выходами соответствующих параллельных регистров, одноименные входы которых объединены и подключены к шинам номера матрицы, число которых равно 1о8 К, а входы,разрешения записи в параллельные реI гистры соединены с соответствующими командными входами. бора содержит И групп по К элементов

2И в каждой; первые входы элементов

2И в каждой группе объединены и под20 ключены к соответствующей шине выбора столбца, вторые входы сдноименных элементов 2И всех групп объединены и подключены к соответствующим входным шинам настройки, число которых

25 также равно К, выходы К элементов

2И каждой группы подключены к соответствующим входным шинам столбца, каждая из которых соединена с С-входом одного из К D-триггеров коммутационных элементов данного столбца, выходное устройство выбора содержит

И логических элементов Кх2И/ИЛИ, выходы которых подключены к выходным шинам коммутатора, причем первые входы одноименных элементов 2И всех

И логических элементов Кх2И/ИЛИ объединены и подключены к соответствующим выходным шинам настройки, 1429308

12

Составитель В.Лементуев

Редактор Н.Тупица Техред Л.Сердюкова Корректор A.06py ap

Заказ 5143/55 Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r, Ужгород, ул. Проектная, 4