Усилитель-инвертор

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в качестве передатчика импульсных сигналов через кабельную магистраль. Цель изобретения - повьшение надеж- iHOCTH работы устройства. Устройство содержит входной каскад, выходной каскад, инвертор 21. Схема защиты от перегрузки по току вьтолнена на диодном оптроне 15. Время заря - да второго конденсатора 23 определяет время -присутствия режима перегрузки по выходу, а время его разряда определяет время выключенного состояния устройства. Схема защиты обеспечивает снижение общего тока, потребляемого устройством в режиме перегрузки, и автоматическое восстановление работоспособности при снятии режима короткого замыкания на выходе устройства. Второй диод 9, одиннадцатый и двенадцатый резисторы 11 и 10 обеспечивают S защиту устройства от наводок напряжения в линии связи. 1 ил. (О С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН ход

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4184589/24-21 (22) 19,01;87 (46) 07.10 ° 88. Вюл. Р 37 (72) О.И. Зайцев, Ф.О. Коньков и В.P. Шварцберг (53) 621,377(088.8) (56) Патент Франции Р 2484740, кл. Н 03 К 17/08, 1981, Патент США 9 3958136, кл. Н 03 К 17/00, 18.05.76. (54) УСИЛИТЕЛЬ-ИНВЕРТОР (57) Изобретение относится к импульсной технике и может быть использовано в качестве передатчика импульсных сигналов через кабельную магистраль.

Цель изобретения - повышение надеж ности работы устройства. Уст- .,„,SU„„1429310 А 1 (д!1 У Н 03 К 17/08, 19/092 роиство содержит входной каскад, вы" ходной каскад, инвертор 21. Схема защиты от перегрузки по току выполнена на диодном оптроне 15. Время заря да второго конденсатора 23 определяет время .присутствия режима перегрузки по выходу, а время его разряда опре" деляет время выключенного состояния устройства. Схема защиты обеспечивает снижение общего тока, потребляемого устройством в режиме перегрузки, и автоматическое восстановление работоспособности при снятии режима короткого замыкания на выходе устройства.

Второй диод 9, одиннадцатый и двенадцатый резисторы 11 и 10 обеспечивают ф защиту устройства от паводок напряжения в линии связи. 1 ил.

1429310

Изобретение относится к импульсной технике и может быть использованФ в качестве передатчика импульсных сигналов через кабельную магистраль.

Бель изобретения - повышение надежности работы устройства за счет введения сх емы защиты от перегрузки по току и наводок напряжения без

УМеньшения нагрузочной способности устройства при согласовании с ТТЛ с семами по входу.

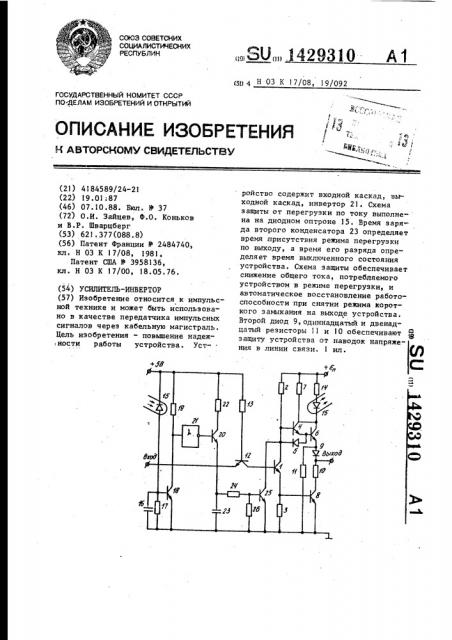

На чертеже приведена электрическая

qxeMa усилителя-инвертора со схемой защиты от перегрузки по току. 15

Усилитель-инвертор содержит первый транзистор 1, коллектор которого через первый резистор 2 соединен с первой шиной питания, а эмиттер через второй резистор 3 соединен с об- 20 фей шиной. К коллектору первого тран-, зистора 1 подключена база второго транзистора 4 и катод первого диода

5..Коллектор второго транзистора 4 объединен с коллектором третьего 25 транзистора 6 и через четвертый ре.зистор 7 подключен к первой шине пи1 тания. Эмиттер второго транзистора 4 подключен к базе третьего транзистора 6 и аноду первого диода 5. База 30 четвертого транзистора 8 подключена к эмиттеру первого транзистора 1, а эмнттер подключен к общей шине. К эмиттеру третьего транзистора 6 под- . ключен анод второго диода 9„катод 35 которого соединен с выходной клеммой. Между катодом второго диода 9 и коллектором четвертого транзистора

8 включен двенадцатый резистор 10, а между эмиттером третьего транзис- 40 тора 6 и общей шиной включен одиннадцатый резистор 11. К базе первого транзистора 1 подключен коллектор пя. того транзистора 12, база которого через третий резистор 13 подключена к второй шине питания (+5 В), а эмиттер — к входной клемме. К первой шине питания подключен первым выводом пятый резистор 1 4, второй вывод которого подключен к аноду светодиода диодного оптрона 15, катод которого подключен к коллекторам второго 4 и третьего 6 транзисторов, Катод фотодиода диодного оптрона 15 подключен к второй шине питания (+5 В), а анод фото- 55 диода через первый конденсатор l6 и шестой резистор 17 подключен к общей шине. К аноду фотодиода диодного опт-. рона 15 подключена база шестого транзистора 18, эмиттер которого подключен к общей шине, а коллектор — через седьмой резистор 19 — к второй шине питания (+5 В). Между коллектором шестого транзистора 18 и базой седьмого транзистора 20 включен инг. вертор 21, вход которого подключен к коллектору шестого транзистора 18, а выход - к базе седьмого транзистора 20, Коллектор седьмого транзистора 20 через восьмой резистор 22 подключен к второй шине питания (+5 В), а эмиттер — через второй конденсатор

23 - к общей шиче. К эмиттеру седьмого транзистора 20 подключен первым выводом девятый резистор 23, а вторым выводом девятый резистор 24 подключен к базе восьмого транзистора

25, эмиттер которого подключен к общей шине, а коллектор - к коллектору первого транзистора 1. Между эмиттером и базой восьмого транзистора 25

4. включен десятый резистор 26.

Усилитель-инвертор работает следующим образом.

При приходе на вход напряжения логической "1" напряжением 2,4-5 В первый транзистор 1 открывается и открывает четвертый транзистор 8, а второй

4 и третий 6 ранэисторы закрыты. На выходе устанавливается напряжение низкого уровня., близкое к 0 В. При приходе на вход напряжения логического "0" напряжением 0 - 0,4 В первый транзистор 1 закрывается, закры" вается четвертый транзистор 8, а второй 4 и третий 6 транзисторы от" крываются, на выходе устанавливается напряжение, близкое к напряжению Е .

В выходной цепи при этом протекает ток Е, определяемый напряжением пи.тания и сопротивлением нагрузки.

Этот ток создает на четвертом реэис" торе 7 падение напряжения, равное

I R>, где R> - номинал напряжения 7, Пока это напряжение меньше порогового напряжения светодиода диодного оптрона 15, равному 1, 2 В, ток через светодиод не течет, фотодиод диодного оптрона 15 закрыт, закрыт шестой транзистор 18, на коллекторе которого создается напряжение высокого уровня, которое поступает на вход инвертора 21, на выходе которого создается напряжение низкого уровня, величиной 0-0,4 В, седьмой транзистор 20 закрыт, второй конденсатор 23 разряжен и восьмой транзистор 25

1 429310 закрыт, что не мешает прохождению сигнала.

При повышении тока нагрузки падение напряжения на четвертом резисто5 ре 7превышает пороговую величину в

1,2 В, часть тока нагрузки начинает протекать через светодиод диодного аптрона 15 и пятый резистор 14. Ток светодиоца вызывает ток фотодиода, который открывает шестой транзистор

18. На входе инвертора 21 устанавливается низкое напряжение, а на выходе — напряжение, близкое к напряжению +5 В. Второй конденсатор 23 быст- 15 ро заряжается через низкоомное восьмое сопротивление 22. Напряжение с выхода эмнттера седьмого транзистора

20, до которого заряжается второй конденсатор 23, открывает восьмой 20 транзистор 25, на коллекторе которого, соединенного с коллектором закрытого первого транзистора 1 и базой второго транзистора 4, создается низкое напряжение, близкое к 0 В. Вто- 25 рой транзистор 4 и третий транзистор

6 закрываются, ток нагрузки прекращается. Светодиод диодного оптрона

15 закрыт, следовательно на выходе инвертора 21 устанавливается низкое 0 напряжение и седьмой транзистор 20 закрывается. Однако заряженный второй конденсатор 23 начинает разряжаться через высокоомный девятый резистор 24 и базу восьмого транзисто35 ра 25, не давая возможности измениться состоянию на выходе и появиться току нагрузки, На выходе присутствует напряжение низкого уровня на все время разряда второго конденсатора

23, После окончания разряда второго конденсатора 23 и, если на входе присутствует напряжение-логического "0", второй 4 и третий 6 транзисторы от"" крываются и появляется ток. нагрузки. 45

Если на выходе присутствует режим короткого замыкания или ток превышает рабочий, то схема опять отключается, если короткого зайакания или перегрузки нет, схема продолжает нормально работать. Время заряда второго конденсатора 23 определяет время присутствия режима перегрузки по выходу и не превышает 1 мкс, а время его разряда определяет время выключенного со-5 стояния усилителя-инвертора и составляет не менее 100 мкс, таким образом в режиме короткого замыкания или перегрузки на выходе схемы возникают импульсы тока перегрузки длительностью не более 1 МКс и со скважностью не менее 100, Это обеспечивает снижение общего тока, потребляемого схемой, до 30-40 мА по сравнению с рабочим током 180-200 мА и автоматичес" кое восстановление работоспособности при снятии режима короткого замыкания на выходе. Указанньй режим, возникающий при коротком замыкании, не превышает допустимого в работе транзисто-. ров и не влияет на надежность схемы.

Первый конденсатор 16 служит для устранения ложного срабатывания схемы зашиты от короткого замыкания при работе устройства на емкостную нагруз ку, что представляет из себя кабельную магистраль. Второй диод 9, одиннадцатый 11 и двенадцатый 10 резисторы служат для защиты устройства от наводок напряжения в линии связи, Формула изобретения

Усилитель-инвертор, содержащий входной каскад, подключенный между входной клеммой и базой первого тран" зистора, коллектор которого подклю чен через первый резистор к первой шине питания, а эмиттер - через второй резистор к общей шине, к коллектору первого транзистора подключена база второго транзистора и катод первого диода, анод которого подклю чен к эмиттеру второго транзистора, коллектор второго транзистора подключен к коллектору третьего транзистора, а эмиттер второго транзистора подключен к базе третьего транзистора, база четвертого транзистора подключена к эмиттеру первого транзистора, а эмиттер четвертого транзистора подключен к общей шине, о т л ич а ю шийся тем, что, с целью повышения надежности работы, в него введена схема защитц от перегрузки по току, входной каскад выполнен на пятом транзисторе, эмиттер которого подключен к входу входного каскада, база через третий резистор — к второй шине питания, а коллектор — к выходу входного каскада, схема защиты от ne" регрузки по току. состоит иэ диодного оптрона, четвертого, пятого, шестого, седьмого, восьмого, девятого и десятого резисторов, первого и второго конденсаторов, шестого, седьмого и восьмого транзисторов и инвертора, Составитель А. Цехановский

Техред Л.Сердюкова Корректор С. Шекмар

Редактор Г. Волкова

Заказ 5143/55 Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5 1429310 6 причем между коллектором третьего коллектор которого через восьмой pes, ðàHçHñòoðà и .первой шиной питания зистор подключен к второй шине пита веден четвертый резистор, к первой ния, а эмиттер через второй конденcàшине питания подключен первый вывод тор — к общей шине, к эмиттеру седь"

Мятого резистора, второй вывод кото- 5 мого транзистора подключен первый вырого подключен к аноду светодиода вод девятого резистора, второй вывод днодного оптрона, катод светодиода которого подключен к базе восьмого соединен с коллектором третьего тран- транзистора, эмиттер восьмого транзисэистора, като 1 фотодиода диодного тора подключен к общей шине, а коллекоптрона подключен к второй шине пита- 10 тор — к коллектору первого транзис" ия, а анод через первый конденсатор тора, между базой и эмиттером восьмошестой резистор подключен к общей ro транзистора включен десятый резисне, к аноду фотодиода диодного on- - тор,одиннадцатый резистор подключен

Ф она подключена база шестого тран- между эмиттером третьего транзистора зистора, эмиттер которого подключен 15 и общей шиной, анод второго диода к общей шине, а коллектор через седь- подключен к эмиттеру третьего транМой резистор - к второй шине питания, зистора, а катод — к выходной клемме, к коллектору шестого транзистора под- . двенадцатый резистор включен между к1лючен вход инвертора, выход которого выходной клеммой и коллектором четг1одключен к базе седьмого транзистора,20 вертого транзистора.