Нормализатор уровня

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике, а именно к многозначным элементам с инжекционным питанием, и .может быть использовано для построения цифровых логических устройств, Цель изобретения - сокращение площади при реализации на кристалле и уменьшение потребляемой мощности. Нормализатор уровня содержит входной транзистор, включенный по схеме токового отражателя, два транзистора, включенных по схеме порогового Детектора , пять переинжектирую1цих транзисторов и питающий транзистор. Питающий транзистор задает в эмиттеры переинжектируюп{их транзисторов соответственно 0,5 1„, 2 1„, 1,5 1„, 1 и 2 IP , где (, - единичный уровень тока . Введение переинжектирующих транзисгоров с соответствующими величина- 3 ми змиттерных токов позволяет обеспечить работоспособность нормализатора уровня при меньшем количестве компонентов . 1 ил.

СО)ОЭ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСИИХ

РЕСПУБЛИК (19) (11) (5)) 4 H 03 К 19/091

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

g.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /

Н А BTOPCHGMV СВИДЕТЕЛЬСВ Т ВУ (21) 4 196095/24-2 1 (22) 17,02,87 (46) 07. 10.88. Вюл. К - 37 (71) Таганрогский радиотехнический институт им. В.Д, Калмыкова (72) А.B. .Ерохин (53) 621.374(088.8) (56) Tich Dao Treshold I L and its

applications to binary symme tric

functions and multivalued logic,ХЕЕЕ, Journal off Solid — State Circuits., 1977, v. SC-12, Ф 5, р. 470, - ig 11.

Авторское свидетельство СССР

К 1088129, кл. Н 03 К 19/091, 1983. (54) НОРМАПИЗАТОР УРОВ НЯ (57) Изобретение относится к импульсной технике, а именно к многозначным элементам с инжекционным питанием, и .может быть использовано для построения цифровых логических устройств.

Цель изобретения — сокращение площади при реализапии на кристалле и уменьшение потребляемой мощности. Нормализатор уровня содержит входной транзистор, включенный по схеме токового отражателя, два транзистора, включенных по схеме порогового детектора, пять переинжектирующих транзисторов и питающий транзистор, Питающий транзистор задает в эмиттеры переинжектирующих транзисторов соответственно 0 5 I„2 Х, 1,5 I0, Iä и

2 I, где Ia — единичный уровень тока. Введение переинжектирующих транзисторов с соответствующими величина- щ ми э)плттернцх токов позволяет обеспечить работоспособность нормализатора уровня при меньшем количестве компонентов. 1 ил.

142931

Изобретение относится к импульсной технике, а именно к многозначным элементам с инжекционным питанием, и может быть использовано для построения цифровых логических устройств.

Цель изобретения - сокращение площади при реализации на. кристалле и уменьшение потребляемой мощности.

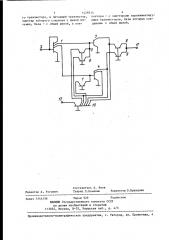

На чертеже приведена электричес. кая функциональная схема нормализато: :ра уровня.

Нормализатор уровня содержит вход: :;ной транзистор 1, включенный по схеме

: токового отражения, эмиттер которого соединен с общей пииной, один коллектор соединен с базой и входной шиной

2, транзисторы Э и 4, включенные по схеме порогового детектора, эмиттеры которых соединены с общей шиной, базы 20 соединены с первым и вторым коллекто..рами входного транзистора 1, пять переинжектирующих транзисторов 5-9

:и питающий транзистор 10, базы которых объединены с общей шиной, коллекторы транзисторов 5 и 6 соединены с базой транзистора 3, коллектор транзистора

7 соединен с базой транзистора 4, коллекторы транзисторов 8 и 9 — с выходной шиной 11, эмиттеры транзисто« 30 ров 8, 9 и 6 соединены с коллектором транзистора Э, с первым и вторым коллектором транзистора 4 соответственнб, соответствующие коллекторы транзистора 10 соединены с соответствующими эмиттерами транзисторов 5- 9, а, эмиттер транзистора 10 - с шиной 12 питания.

Нормализатор работает следующим образом.

Входной транзистор 1, включенный по схеме токового отражения, имеет коэффициент усиления, равный единице.

Это обеспечивается соотношением площадей областей выходного коллектора и коллектора обратной связи. Питающий транзистор 10 задает в эмиттеры переинжектирующих транзисторов 5-9 и соответственно 0,5Т„, 2Х„, 1,5Х„, Io u

2?„, где I - единичный уровень тока.

Это обеспечивается геометрией и взаимным расположением эмиттера и коллекторов питающего транзистора 10.

При подаче входного тока в входную шину 2 устройства в зависимости от

его величины: О,SI» (0,5-1,5) I, 55 (1,5-2,5) Т„, ) 2,5I, на выходе нормализатора ток соответствует OI», 2IO, о

4 2

Если входной ток Т, (Î,SIб, входЬУ ной транзистор 1 отводит не весь ток, задаваемый в базы транзисторов 3 и 4, которые открьггы, поэтому отводят токи, задаваемые питающим транзистором 10 в эмиттеры транзисторов 8 и 9, последние. эакрьггы. В выходе устройства нулевой уровень тока.

Если входной ток 03SIo6?ьм(1.5ТЬФ транзистор 4 открыт, шунтирует транзисторы 6 и 9, а транзистор 3 закрыт, так как ток 0,5I задаваемый в его базу транзистором 5, полностью отводится входным транзистором 1. Транзистор 8 открыт и задает в выходную шину ток, равный I .

Если входной ток 1,5Х, (? „(2,51, транзистор 4 закрыт, а транзистор 3 открыт, так как и его базу транзисторы 5 и 6 задают суммарный ток 235I и шунтируют транзистор 8, последний закрыт. Открытый транзистор 9 задает в выходную шину ток, равный 2I,.

Если входной ток Т „ 2,5Х„, тран зисторы Э и 4 закрьггы, а транзисторы

8 и 9 открыты и задают в выходную шину 11 суммарный ток, равный 3I .

Формула изобретения

Нормализатор уровня, содержащий входной транзистор, включенный по схеме токового отражения, база которого соединена с входной шиной, а эмиттер — с общей шиной, первый и второй транзисторы, включенные по схеме порогового детектора, эмиттеры которых соединены с общей шиной, причем коллекторы входного транзистора соединены соответственно с базами первого и второго транзисторов, о т— л и ч а ю шийся тем, что, с це" лью сокращения площади при реализации на кристалле и уменьшения потребляемой мощности, в него введены первый и второй переинжектирующие транзисторы, коллекторы которых соединены с базой первого транзистора, третий переинжектирующий транзистор, коллектор которого соединен с базой второго транзистора; четвертый и пятый переинжектирующие транзисторы, коллекторы которых соединены с выходной шиной, а эмиттеры - с, коллектором первого и первым коллектором второго транзистора соответственно, второй коллектор второго транзистора соединен с эмиттером второго переинжектирующеСоставитель А. Янов

Техред Л.Олийнык Корректор О.Кравцова

Редактор А. Рогулич

Тираж 929 Подписное

BHKgIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5144/56

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

3 1429314 4 го транзистора, и питающий транзистор, лекторы — с эмиттерами переикжектиру.эмиттер которого соединен с шиной пи- ющих транзисторов, базы которых сое" тания, база — с общей шиной, а кол- динены с общей шиной.