Логический элемент исключающее или

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано при построении универсальных и специализированных цифровых устройств. Цель изобретения - расширение функциональных возможностей логического элемента. Логический элемент содержит р-транзисторы 1, .2, 7...9 транзибторы 3, 4, 10, 12, 13. Введение МДП-транзистора 17 п-типа позволяет логическому элементу формировать полный уровень Лог.О на дополнител выходе (функции И-НЕ) 18, 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИН

„Л0„„1429 1 (я) 1 Н 03 К 19/094

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1072264 (21) 4098684/24-21 (22) 08.08.86 (46) 07.10.88. Бюл. Р 37 (72) А.Е. Заболотный, В.А.- Максимов, и Я.Я. Петричкович (53). 621.374(088 ° 8) (56) Авторское свиде:z ельство СССР

У 1072264, кп. Н 03 К 13/094, 1982. (54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ИСКЛЮЧАЮ1ЦЕЕ

ИЛИ (57) Изобретение относится к импульсной технике и может быть использовано при построении универсальных и специализированных цифровых устройств.

Цель изобретения — расширение функциональных возможностей логического элемента. Логический элемент содержит р-транзисторы 1, 2, 7...9 и птранзисторы 3, 4, 10, 12, 13. Введение МДП-транзистора 17 и-типа позволяет логическому элементу формироват полный уровень "Лог.0" на дополнител т выходе (функции И-НЕ) 18. 1 ил.

1429315

Составитель А. Кабанов

Техред Л.Олийнык Корректор С.Черни

Реда кт ор Н . P or улич

Заказ 5144/56

Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва, -35, Раушская наб;, д. 4/5 Производственно"полиграфическое предприятие, г. Ужгород, ул. Проектная, 4, Изобретение относится к импульснрй технике, может быть использовано п и построении универсальных и спец иалиэированных цифровых устройств, в частности схем сравнения, сумматоров, и является усовершенствованием устройства по авт. св..11" 1072264.

Цель изобретения — расширение функциональных возможностей путем ормирования полного уровня "Лог.0" дополнительном выходе функции

И,-НЕ.

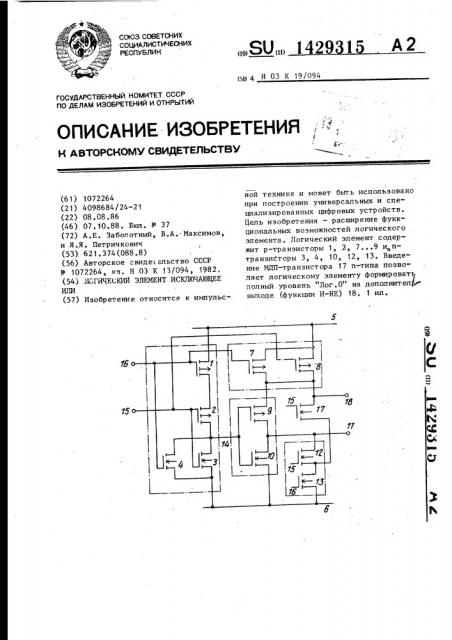

На чертеже представлена принципи4льная электрическая схема логического элемента ИСКЛ10ЧАЮЩЕЕ ИЛИ.

Элемент содержит последовательно

Соединенные первый и второй р-транисторы 1 и 2, первый и-транзистор второй и-транзистор 4 включен араллельно первому п-транзистору 3, сток первого р-транзистора 1 соеди, ен с шиной 5 питания, исток второго -транзистора 4 соединен с общей шийой 6> третий и четвертый р-транзисторы 7 и 8 соединены параллельно, третий р-транзистор 7, шестой р-транзистор 9 и третий и-транзистор 10 включены последовательно между шиной питания и общей шиной 6, сток пятого р-транзистора 9 соединен с пер ой выходной шиной 11 .и через последовательноо соединенные четвертый и йятый и-транзисторы 12 и 13 с общей

Ыиной 6, затворы пятого р-транзистора

9 и третьего и-транзистора 10 соединены с истоком второго и-транзистора

4 и второй выходной шиной 14, первая входная шина 15 соединена с затворами второго и четвертого р-транзисторов

3 и 13, вторая входная шина 16 соеди5 нена с затворами второго и четвертого

n"òðàHçèñòoðoâ 4 и 12 и первого и третьего р-транзисторов 1 и 7, дополнительный МДП-транзистор 17 n-ro типа . включен между истоком пятого р-транзистора 9 и третьей выходной шиной

18 и стоком четвертого и-транзистора

12, затвор которого соединен с затвором дополнительного МДП-транзистора 17.

При входной комбинации "11" логичес кий ур овень "О" обеспечивается открытыми и-транзисторами 13 и 17, что позволяет сформировать на выходной шине 18 (функции И-НЕ) уровень шины 6. При других входных комбинациях устройство функционирует аналогично известному.

Формула изобретения

Логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ по авт. св. 9 1072264, о т л и ч а ю шийся тем, что, с целью расширения функциональных возможностей, в него введен дополнительный IIтранзистор п-типа, включенный между источником первого нагруэочного р( канального транзистора и общей точкой соединения первого и второго выходного транзисторов п-типа, затвор дополнительного Mfa-транзистора и-типа подключен к затвору второго выходного транзистора п-типа.