Умножитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в автоматике, радиотехнике и системах средств связи. Целью изобретения является уменьшение времени установления выходной частоты за счет грубой настройки. Устройство содержит генератор 1 импульсов, пере-г счетный блок 2 частоты, фазовый детектор 3, элементы И 4-6, реверсивный счетчик 7, преобразователь 8 коднапряжение, триггеры 9 и 10, входную шину 11, выходную шину 12, Для достижения поставленной цели в устройство дополнительно введен элемент ИЛИ 13, первый вход которого соединен с инверсным выходом второго триггера 10, второй вход.соединен с четвертым выходом фазового детектора 3, а вькод - с вторым входом первого элемента .И 4. При синхронизации триггеры переключаются в состояние 1, тем самьм обеспечивая точную подстройку ф&зы формируемых импульсов кольцом фазовой АПЧ относительно импульсов, , поступающих на вход 11 устройст а. 2 ил (Л с:

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 ив>s ци (51) 4 Н 03 К 23/00//Н 03 В 19/00

/ /уи

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

4 ки- с

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4128696/ 24-21 (22) 17.06.86 (46) 07.10.88. Бюп. У 37 (72) Г.А. Томилов и Ю.С. Пономарев (53) 621. 374 (088.8) (56) Авторское свидетельство СССР.

У 1279058, кл. Н 03 К 5/156, 1985.

Авторское свидетельство СССР

У 1119165, кл. Н 03 К 5/156, 1983.

Авторское свидетельство СССР

У 1261110, кл. Н 03 К 23/00//Н 03 В

19/00, 1984. (54) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ (57) Изобретение относится к импульсной технике и может быть использовано в автоматике, радиотехнике и системах средств связи. Целью изобретения является уменьшение времени установления выходной частоты за и счет грубой настройки. Устройство содержит генератор 1 импульсов, пересчетный блок 2 частоты, фазовый детектор 3, элементы И 4-6, реверсивный счетчик 7, преобразователь 8 коднапряжение, триггеры 9 и 10 ° входную шину 11, выходную шину 12. Для достижения поставленной цели в устройство дополнительно введен элемент

ИЛИ 13, первый вход которого соединен с инверсным выходом второго триг« гера 10, второй вход соединен с четвертым выходом фазового детектора 3, а выход — с вторым входом первого зле. мента И 4. При синхронизации триггеры переключаются в состояние "1", тем: у

C. самым обеспечивая точную подстройку фьеы формируемых импульсов кольцом ь/е фазовой АПЧ относительно импульсов, С поступающих на вход 11устройства. 2 ил

1429316

Изобретение относится к импульсной технике и может быть использовано в автоматике, радиотехнике и системах средств связи.

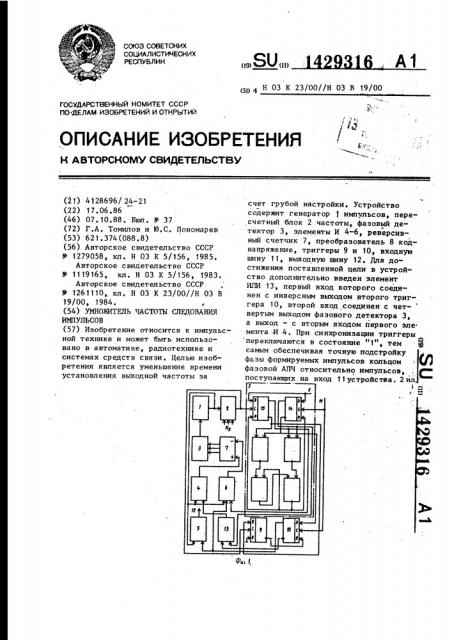

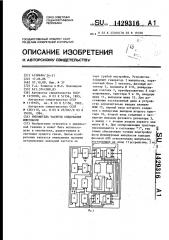

Пель изобретения — уменьшение времени установления въ|ходной частоты за счет грубой настройки. На фиг. 1 показана структурно° ° ° лектрическая схема устройства; на иг. 2 — временные диаграммы, поясющие работу "устройства.

Устройство содержит генератор 1 мпульсов, пересчетный блок 2 частоы, фазовый детектор 3, первый., вто рой и третий элементы И 4-6, ревер;сивный счетчик 7, преобразователь 8 .код-напряжение, первый D-триггер 9

:и .второй D-триггер 10, С -вход кото:рого соединен с входной шиной 11 20

:устройства и первым входом фазового детектора, второй вход которого сое;динен с выходом пересчетного блока 2 частоты и С-входом первого D-триггера 9, С-вход которого соединен с вы- 5 ходом генератора 1 импульсов и входом пересчетного блока 2 частоты, R-вход— с земпяной шиной, 9-вход - с первым входом фазового детектора 3, а инверсный выход - c R-входом второго Dтриггера 10, 0-вход которого соединен . с вторым выходом фазового детектора

3 прямой выход — с вторым входом, второго элемента И 5, выход которого соединен с выходной шиной 12 устройства. Выход первого элемента И 4 соединен с входом суммирования реверсивного счетчика 7, выходы которого соединены с входами преобразователя

8 код-напряжение выход которого соеI

40 динен с управляющим входом генерато-. ра 1 импульсов. Выход последнего соединен с входом пересчетного блока

2 частоты, вторым входом второго элемента И 5 и первыми входами первого 4

45 и третьего 6 элементов И, второй вход последнего соединен с третьим выходом фазового детектора, а третий входс первым входом второго элемента И 5.

Кроме того, устройство содержит элемент ИЛИ 13, первый вход которого соединен с инверсным выходом второго

D-триггера 10, второй вход — с четвертым .выходом фазового детектора 3, 55 а выход — с вторым входом первого элемента И 4, при этом выход третьего элемента И 6 соединен с входом вычитания реверсивного счетчика 7.

Устройство работает следующим образом.

В исходном состоянии в пересчетный блок 2 ввддится требуемый коэффициент умножения. Минимальное и максимальное значения кода реверсивного счетчика 7 соответствуют минимальной и максимальной частоте следования импульсов генератора 1 соответственно и равны полосе захвата кольца ФЛПЧ.

В синхронном .режиме, т.е ° когда импульсы на входы фазового детектора

3 поступают поочередно (режимы I u

II на фиг. 2), устройство работает следующим образом.

Пусть на первом входе фазового детектора 3 появляется импульс входной частоты, тогда триггер 14 переключается в состояние "1" и появившийся на втором входе импульс с выхода блока 2 переключает триггер 14 в состояние "0". Импульс с прямого выхода триггера 14 поступает на первый вход элемента ИЛИ 13 и с его выхода на второй вход элемента И 4, тем самым обеспечивая прохождение импульсов с выхода генератора 1 на вход суммирования реверсивного счетчикЫ 7. Сигналы с выхода последнего поступают на преобразователь 8, его выходное напряжение увеличивается, что приводит к возрастанию частоты следования импульсов, формируемых генератором 1. Следующий импульс с выхода блока 2 появляется раньше, чем в предыдущем случае, что приводит к уменьшению разности фаэ сравниваемых частот. Этот процесс продолжается до тех пор, пока разность фаз сравниваемых частот не равна нулю.

Если импульс с выхода блока 2 по- . является на втором входе фазового, детектора 3 раньше, чем импульс на

его первом входе, триггер 15 переключается в состояние "f" и формирует импульс на прямом выходе, который поступает на второй вход элемента

И и при наличии напряжения на прямом выходе триггера 10 обеспечивает прохождение импульсов с выхода генератора 1 на вход вычитания реверсивного счетчика 7. В синхронном режиме кольца ФАПЧ D-триггеры 9 и 10 находится в состоянии "1", обеспечивая наличие напряжения на третьем и втором входах соответственно элементов

И 5 и 6. Сигналы с выхода реверсивного счетчика 7 поступают на преобра1429316 зователь 8, его выходное напряжение уменьшается, что приводит к уменьшению частоты следования импульсов генератора 1. Указанные циклы повто5 ряются до тех пор, пока разность фаз сравниваемых частот не станет равна нулю, при этом сформированная последовательность импульсов генератором 1 через элемент И 5 поступает на выход- 10 ную шину 1 2 устр ойства .

При нарушении синхронизации (режимы III u IV на фиг, 2) включаются элементы грубой настройки, например, на С-вход триггера 14 поступает подряд два импульса с входа 11 устройства. Тогда триггеры 14 и 10 переключаются под воздействием второго импульса в состояние "0" и импульсы на выходе элементов И 5 и 6 отсутствуют, а появление напряжения на инверсном выходе триггера 10 обеспечивает напряжения через элемент ИЛИ 13 на втором входе элемента И 4 независимо от состояния четвертого выхода фазо- 25 вого детектора 3, что приводит к появлению импульсов, формируемых генератором 1 на входе суммирования реверсивного счетчика 7, эа счет чего возрастает частота следования импульсов генератора 1 до тех пор, пока не происходит синхронизация кольца ФАПЧ, тогда триггеры 14 и 10 переключаются в состояние "1" и устройство переходит в режим фазовой подстройки частоты. .35

Если за рассматриваемый цикл синхронизация не происходит, в конечном счете происходит переполнение ревер сивного счетчика 7 и он переключает,ся в нулевое состояние, в результате 40 чего частота следования импульсов с выхода генератора 1 уменьшается до минимальной, и по мере поступления очередных импульсов на вход суммиро вания реверсивного счетчика 7 повтор45 но происходит увеличение частоты следования импульсов генератора 1 до момента синхронизации кольца ФАПЧ.

При синхронизации триггеры 14 и 10 переключаются в состояние "1", обеспечивая точную подстройку фазы форми50 руемых импульсов генератором 1 через элементы И 4 и Ь и появление этих импульсов на выходе элемента И 5.

Работа устр ойст ва в данном р ежиме аналогична описанной.

При нарушении синхронизации, когда на С-вход триггера 15 поступают подряд два импульса с выхода пересчетного блока 2, триггеры 15, 9 и 10 переключаются под воздействием второ" го импульса в состояние "0" и работа элементов грубой настройки осуществляется аналогично, как и в предьщу" щем случае. При синхронизации триггеры 15, 9 и 1 0 переключаются в состояние "1", тем самым обеспечивая точную подстройку фазы формируемых импульсов кольцом ФАПЧ, относительно импульсов, поступающих на вход 11 устройства..

Формула изобретения

Умножитель частоты следования импульсов, содержащий- генератор импульсов, выход которого соединен с входом пересчетного блока и с первыми входами первого, второго и третьего элементов И, выход последнего из которых соединен с выходной шиной, второй," вход — с прямым выходом первого триггера, информационный . вход которого соединен с первым выходом фазового детектора, первый вход которого соединен с входной шиной и тактовым входом первого триггера, вход. сброса ко" торого соединен с инверсным выходом второго триггера, информационный вход которого соединен с вторым выходом фа.зового детектора, второй вход кото" рого соединен с выходом пересчетного блока и тактовым входом второго триггера, вход сброса которого соединен с общей шиной, реверсивный счетчик импульсов, входы суммирования и вычитания которого соединены с выходами соответственно первого и второго эле" ментов И, выходы — поразрядно с входами преобразователя код — напряжение, выход которого соединен с входом генератора импульсов, о т л и ч а ю— шийся тем, что, с целью уменьшения времени входа в режим, в него введен элемент ИЛИ, выход которого соедйнен с вторым входом первого элемента И, первый вход — с инверсным выходом первого триггера, второй вход — с третьим выходом фазового детектора, четвертый выход которого соединен с вторым входом вто.рого элемента И, третий вход которого соединен с прямым выходом первого триггера.

° ВИМА

° ЯМИМ

ШЯВИЙПИ » ивиини

142931 6

Тираж 929

П одпис ное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5, Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

Редактор Н. Рогулич

Заказ 5144/56

Составитель А.Чистякова

Техред Л.Олийнык Корректор В.Романенко