Цифровой функциональный преобразователь

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И1

О963 А1 (51)4 G 06 F 15 31

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

llO.ÄÅËÀM ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3902139/24-24 (22) 27.05.85 (46) 15.10,.88. Бюл. У 38 (71) Ленинградский электротехнический институт им. В.И.Ульянова (Ленина) (72) И.В.Герасимов, А.В.Гетров .и Н.М.Сафьянников (53) 681.325(088.8) (56) Мельников А.А. и др. Обработка частотных и временных импульсных сигналов М.: Энергия, 1976, Авторское свидетельство СССР

У 741263, кл. G 06 Р 7/55, 1978, (54)(57) ЦИФРОВОЙ ФУНКЦИОНАЛЪНИИ ПРЕОБРАЗОВАТЕЛЬ, содержащий счетчик, элемент И, блок вычитания, двоичный умножитель частоты, о т л и ч а ю— шийся тем, что, с целью расширения функциональных возможностей sa счет воспроизведения степенной функции, в преобразователь дополнительно, введены два элемента ИЛИ, два элемента И, выходы первого и второго элемента И соединены с входом вычитаемого блока вычитания и вычитающим входом счетчика соответственно, выход второго элемента И соединен с первым входом первого элемента ИЛИ соответственно, информационный вход преобразователя соединен с первым входом третретьего элемента И и с входом уменьшаемого блока вычитания, выход которого соединен с входом суммироврния счетчика, второй вход третьего элемента И и первый вход второго элемента ИЛИ являются входами первой и второй опорных частот преобразователя соответственно, выход первой и второй опорных частот преобразователя соединены с входами первого и второго элементов И, вторые входы первого и второго элементов И соединены с 3 выходом двоичного умножителя частоты„ информационный вход которого сое- lsd/ динен с выходом второго элемента ИЛИ, С вход управления частотой двоичного умножителя частоты соединен с выходом ф счетчика, выход третьего элемента И соединен с вторыми входами первого и второго элементов ИЛИ, выхЬд первого элемента ИЛИ является выходом преобразователя.

1430963

Изобретение относится к автоматике и вычислительной технике и может найти применение в устройствах обработки информации, представленной в виде числа импульсов или интервалов времени, Цель изобретения - расширение функциональных возможностей преобразователя при одновременном noBbHIIeHHH 1O помехоустойчивости. ъ

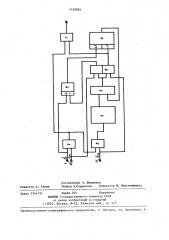

На чертеже изображен предлагаемый преобразователь.

Сущность изобретения состоит в создании помехоустойчивого цифрового функционального преобразователя для. вычитания натурального логарифма и степенной функции вида Х /, периодически преобразующего число-импульсные сигналы с использованием итерационного метода реализации оператора усреднения путем функционального обобщения двоичного умножителя частоты эа счет совмещения фазирования и модуляции импульсных последо- 25 вательностей и создания благодаря этому возможностей аппроксимирующего вычисления функций натурального логарифма и функции вида Х / .

Преобразователь, содержит информационный вход 1, элемент И 2, счетчик

3, двоичный умножитель 4 частоты, блок 5 вычитания, элементы ИЛИ 6 и

7 и элементы И 8 и 9.

Преобразователь работает следующим образом.

Пусть в начальный момент времени разряды счетчика 3 обнулены. На информационный вход 1 поступает периодически повторяющийся с периодом

Т число-импульсный код с опорной частотой f . На входы 10 и 11 поступают последовательности импульсов со средними опорными частотами fz, и

Ер, меньшими f0 первая иэ которых синхронизирована импульсами чис .ло-импульсного кода, поступающими по фазе 1, а вторая синхронизирована импульсами фазы 2. При,этом импульсы, поступающие с входа 1 запаздывают относительно импульсов, поступающих с входа 10 на время задержки логического элемента. Таким образом, импульсы, поступающие с входа 10 с опорной частотой f, пройдут на выход элемента И в течение промежутка времени t каждого периода поступления число импульсного кода Т вЂ” N /f где N — коэффициент пересчета счетчиков устройства. Средняя частота периодически повторяющейся последовательности импульсов., формируемой на выходе элемента И 2, определяется следующим образом:

f

o N (1)

Учитывая, что за время t каждого периода повторения число-импульсного кода по входу 1 поступает fpt импульсов аргумента, выражение fz t/N > представляет собой нормированное значение х аргумента N„

Следовательно о 1х

На суммирующий вход блока 5 вычитания с входа 1 в среднем за период поступления кода аргумента поступает частота f N „. Благодаря фазированию опорных последовательностей, поступающих с входом 10 и 11, на выходе элемента ИЛИ 6 будет сформирована импульсная последовательность со средней частотой f,N „,+ f поступающая на вход двоичного умножителя частоты.

На суммирующий вход счетчика 3 поступают импульсы аргумента с выхода блока 5 вычитания, на вычитающем входе которого импульсы отсутствуют в момент начальной установки.

Под воздействием растущего управляющего кода счетчика 3 на входы элементов И 8 и 9 начнут поступать импульсы со средней частотой

fg Nx

N где И вЂ” число, соответствующее коду счетчика 3.

На выходе элементов И 8 и 9 будут сформированы из входной последовательности импульсов двоичного умножителя частоты две последовательности импульсов, поступающие на вычитающий вход блока 5 вычитания и вычитающий вход счетчика 3 синхронно с импульсами, проходящими на первый и второй входы элемента ИЛИ 6 по фазе 1 и 2 со средними частотами

f a> Nх fee

---- "-Б и — -Б

Нь

В основу работы преобразователя положен принцип автоматической компенсации импульсных последовательностей с использованием частотно-импуль.ср1 Nx Nc fo Ne

f N о х< т) 1п

30 откуда

Nefo Nx

N =

fo„Nx + fo2 (2) Отсюда определяется выражение средней частоты импульсной последовательности, поступающей на вычитающий вход счетчика 3, fofo 11 х о о1 х о2

Сумма частот последовательностей импульсов, поступающих по фазе I и 2 на входы элемента ИЛИ 7 и формируемая на выходе этого элемента, определяет результат функционального преобразования:

f foo. Хх я ) + =9-==== о1 11х + о 50 (3) Р=F+Р= fo)

2 2

f Nx fog(fo + fo

f„N„, + f,2

Nx л

e1X + из (3) получим

Обозначив х

Есс(Е о, + о)х 55 х

Р2 f

Fz макс

f о1 = f а1 /Fz макс, I где йо = f.o/F-. з 14309 сной следящей системы при наличии импульсного потока, объединяемого и разделяемого в процессе формирования сигналов прямой и обратной связи, в результате чего воспроизводится дроб5 но-рациональное выражение с частотным представлением выходной информации, причем перестройка вычисляемой элементарной функции осуществляется путем изменения значений частот опорной и импульсных последовательностей.

В качестве схемы сравнения, вырабатывающей сигнал рассогласования, используется реверсивный счетчик 3. Ус- 15 ловием динамического равновесия преобразователя является равенство приращений кодов суммирующих и вычитающий цепей в реверсивном счетчике 3 в течение периода повторения число-им- 20 пульсного кода, поступающего с входа

1, т.е. равенство средних частот импульсных последовательностей, поступающих на суммирующий и вычитающий входы реверсивного счетчика 3. С уче- 25 том функционирования элементов 2 — 9 условием динамического равенства будет

1 0 0 /Р2 макс — максимальное значение час2 масс тоты выходной импульсной последовательности.

При выполнении следующих условий:

f, = 0,82505;

f, = 0,17372; и 0 29624 получим рациональную функцию

Fz (0 17372х + 1 7015х которая аппроксимирует функцию

pn(lax), х е f0; 11 с относительной погрешностью, не превосходящей 0,014Х

При задании величины

fo = О 25928 1 02 1

О! йо2 = Ов91857 10 в получим рациональную дробь

Fz, 0 71009xf + 0 42729x аппроксимирующую функцию х, хеf0; 11

2/3 с относительной приведенной погрешно-. стью, не превосходящей 0,1Х.

Таким образом, предлагаемый функциональный преобразователь имеет расширенные функциональные возможности в сравнении с прототипом. Кроме того предлагаемый преобразователь является более помехоустойчивым, так как появление единичных. сбоев не приводит из-за реализации onератора усреднения к окончательному искажению результата. К числу достоинств предлагаемого преобразователя можно отнести его относительную простоту, позволяющую отказаться от использования узла сложения и блока управле" ния прототипа, реализация которых, очевидно, сложнее вводимых четырех логических элементов, а также возможность построения двоичного умножителя частоты в интегральном исполнении на базе микросхем К 155 ИЕ8, выпускаемых промышленностью.

Таким образом, предлагаемый преобразователь является к тому же более технологичным и надежным, а при сопоставимой конструкторско-технологической среде проектирования имеет меньшие габариты и вес.

1430963

Составитель 3, Шершнева

Техред Л.Сердюкова Корректор М. Максимишинец

Редактор А. Ревин

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Заказ 5344/51

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4