Устройство для определения показателей надежности объектов

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может ть использовано при анализе и прогнозировании надежности объектов на основе показателей структурной надеясности. Устройство решает задачу повышения быстродействия расчета показателей надежности объектов за счет исключения необходимости перебора всех возможных состояний объекта для каждого из минимальных путей успешного функционирования. Устройство содержит блок 1 памяти, счетчик 2 адреса , элемент ИЛИ-НЕ 3, генератор 4 тактовых импульсов, блок 5 ассоциативного запоминающего устройства, блок 6 сумматоров, адресную шину 7, информационну шину 9, улравяяюций выход 0, регистр 14, элементы памяти , элементы ИЛИ, элементы И, сумматоры . Коды минимальных путей из блока 1 памяти последовательно подаются на входы блока 5 ассоциативного запоминающего устройстве, с быхода которого снимаются работоспособные состояния объекта, соответствующне данному минимальному пути. Указанные состояния объекта накапливаются в регистре 14 и в конце работы устройства преобразуются блоком 6 сумматоров в количестве работоспособных состояний объекта, соответствующих числу исправленных элементов. 1 з.п. ф-лы, 1 табл. 3 ил. (Л 4ii Од О UD

СС ОЗ COBETCHHX

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (su4 G06 F 15 46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4199557/24-24 (22) 23.02.87 (46) 15.10.88. Бюл. У 38 (72) M.H. Штовба, А.И. Павлов, А.Г. Гутник и С.П. Полковников (53) 684.3(088.8} . (56) Авторское свидетельство СССР

9 1072058, кл. С 06 F 15/46, }981.

Авторское свидетельство СССР

Ф 708359, кл. G 06 F 15/46, 1976. (54) УСТРОЙСТВО ДГЯ ОПРЕДЕЛЕНИЯ ПОКАЗАТЕЛЕЙ НАДЕЖНОСТИ ОБЪЕКТОВ (57) Изобретение относится к области вычислительной техники и может быть использовано при анализе и прогнозировании надежности объек-ов на основе показателей структурной надежно- сти, Устройство решает задачу повышения быстродействия расчета показателей надежности объектов за счет исключения необходимости перебора всех возможных состояний объекта дпя каждого из минимальных путей успешно„„БО„„ИЗО968 А1 го функционирования. Устройство содержит блок 1 памяти, счетчик 2 адреса, элемент ИЛИ-НЕ 3, генератор 4 тактовых импульсов, блок 5 ассоциативного запоминающего устройства, блок 6 сумматоров, адресную шину 7, информационную шину 9,- управляющий выход 10, регистр 14, элементы памяти, элементы ИЛИ, элементы И, сумматоры. Коды минимальных путей из блока 1 памяти последовательно подаются на входы блока 5 ассоциативного запоминающего устройства, с выхода которого снимаются работоспособщие состояния объекта, соответствующие данному минимальному пути. Укаэанные. 3 состояния объекта накапливаются в регистре 14 и в конце работы устройства преобразуются блоком 6 сумматоров s количестве работоспособных состояний объекта, соответствующих числу исправленных элементов. 1 s.è. ф-лы, 1 табл. 3 ил.

1430968

Номер мини мального пути

В свою очередь что эквивалентно Х- ° + Х.

g мп t! sn ип где F;

1, и.

Изобретение относится к вычислительной технике и может быть использовано при анализе и прогнозировании надежности объектов на основе покаS зателей структурной надежности.

Цель изобретения — повышение быстродействия устройства.

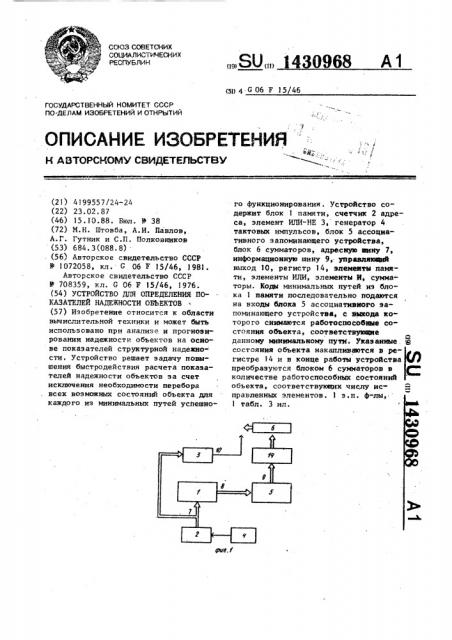

На фиг. 1 и 2 изображена структурная схема предлагаемого устройства! 1О на фиг. 3 — структурная схема многовходового сумматора.

Устройство содержит блок 1 памяти, счетчик 2 адреса, элемент ИЛИ-НЕ 3, генератор 4 тактовых импульсов, блок 15

5 ассоциативного запоминающего устройства, блок 6 сумматоров, адресную шину 7, информационную ши" ну 8, информационную шину 9, управэлементы ИЛИ 12, элементы И 13, ре" 20 гистр 14 и сумматоры 15.

Блок 1 памяти предназначен для хранения кодов минимальных путей. Например, для мостиковой схемы, состоя<ей иэ элементов х1,х,х,,х4 и х (х

25 в диагонали), содержимое блока 1, т.е. коды минимальных путей, представлено в табл ице.

Признак работоспособности элементов х2. хъ х4

1 0 0 1 1

0 1 1 0 1

0 1 0 0 40

0 1 0 0

Из данных таблицы следует, что на- 45 личие "1" в соответствующем разряде показывает наличие и исправность элемента в цепи, а "0" - отсутствие ипи отказ элемента.

В данном случае число элементов

n 5, число минимальных путей m 4.

Pasрядность блока определяется числом элементов в исследуемом объекте, а емкость - числом минимальных путей . начетчик 2 адреса содержит Р Разря дов и предназначен для формирования адреса ячейки блока 1 памяти.

Элемент ИЛИ-НЕ 3 íà P входов предназначен для формирования сигнала об окончании, работы устройства и возбуждения управляющего выхода 10.

Блок 5 ассоциативного запоминающего устройства (АЗУ) предназначен для хранения всех и-разрядных кодов, выполнения операций сравнения кодов минимальных путей, поступающих из блока 1 памяти с хранимыми кодами, фиксации фактов совпадения кодов и выдачи результатов сравнения через регистр 14 в блок б сумматоров. Сравнение осуществляется по схеме импликаций. При этом возбуждение соответствующего выхода блока 5 A3У проис— ходит в том случае, если единичные. значения кода минимального пути являются подмножеством единичных значений кода состояния объекта.

Совокупность элементов ИЛИ 12, подключенных к элементам памяти од-. ной ячейки и одному элементу И 3„ образуют схему поразрядного сравнения, Сравнение осуществляется по схеме импликаций, Правило сравнения состоит в следующем. На выходе элемента И 13 единичный сигнал должен формироваться только при совпадении единичных значений разрядов кода минимального пути с единичными значениями содержимого соответствующих элементов

11 памяти ячейки АЗУ. Тогда

Е;„= 1, если Х ) мп1 Х;; „= 1 или Х м„= О, — значение функции на выходе элемента И 13"; — значение функции на выходе элемента ИЛИ 12 ); — значение содержимого элемента 11 1; — значение )-го разряда кода минимального пути;

i 430968

Х +Х.

11 jgn !ма"

Np а

После минимизации выражения óñëîвие возбуждения выхода элемента И 13 имеет вид

На основе этого соотношения построены схемы поразрядного сравнения каждой ячейки памяти, а разрядные линии информационной шины 8 подключа" ются к инверсным выходам блока 1 памяти.

Регистр 14 предназначен для записи результатов сравнения кодов минимальных путей с кодами тех состояний объекта, которые накрываются данными путями.

Блок сумматоров 6 предназначен для подсчета числа N< рабочих состоя- 2б ний объекта при К исправных элементах.

Устройство работает следующим образом.

В исходном состоянии в блок 1 па- 25 мяти заносятся коды минимальных пу-. тей, а в вычитающий счетчик 2 адреса число ш+1. В блок 5 ассоциативного запоминающего устройства записывается 1 2 двоичных кодов, соответст-- Зб

1 вующих всем возможным состояниям объекта.

При запуске устройства сигнал с генератора 4 тактовых и.лтульсов по-. ступает в счетчик 2 адреса и уменьша- ЗБ ет его содержимое на единицу. В блок ! памяти поступает адрес ш-ro минимального пути. После считывания инверсный код этого пути по информационной шине 8 передается в блок 5

40 ассоциативного запоминающего устройства и одновременно становится доступным схемам сравнения всех ячеек памяти блока 5 АЗУ. Код поразрядно подается на первые входы элементов 4

ИЛИ 12, на вторые входы которых поступает содержимое элементов 11 па- мяти. В результате поразрядное сравнение содержимого всех ячеек памяти с инверсным кодом минимального пути.

При совпадении единичных разрядов инверсного кода минимального пути и кода, хранимого в ячейке памяти, схема сравнения такой ячейки формирует на выходе единичный сигнал, который записывается в соответствующий триггер регистра 14.

Таким образом, в регистре 1 4 в "1 " будут установлены те разряды, которые соответствуют ячейкам памяти, хранящих коды, накрываемые данным минимальным путем. С выходов 14 записаннь.е единицы через информационную шину 9 поступают на соответствующие входы блока 6 сумматоров, где происходит их арифметическое сложение. В следующем такте сигналом с генератора 4 тактовых импульсов вновь происходит уменьшение содержимого счетчика 2 адреса. В блок 1 памяти выдается адрес т-1 минимального пути.

Инверсный код этого пути поступает в блок 5 АЗУ, и вышеописанные действия повторяются.

Аналогичным образом происходит офработка кодов всех остальных минимальных путей.

После подачи в блок 5 АЗУ кода последнего (минимального) пути модификация счетчика 2 адреса приводит к его обнулению. Код "О" по адресной шине 7 воздействует на входы элемента ИЛИ-НЕ 3. В результате на выходе элемента ИЛИ-НЕ формируется сикнал

"l" регистрация которого с выхода

10 устройства свидетельствует об окончании работы устройства.

Содержимое на выходе блока 6 сумматоров соответствует количеству работоспособных состояний И < объекта при K исправных элементах.

Ч, = . Е NÄ.

К- "<

На основе информации, полученной в результате работы устройства, можно рассчитать следующие показатели: общее число работоспособных состоянийй; степень гибкости системы (показатель совершенства структуры), равную где No и. функцию P надежности объекта произвольной структуры.при известной вероятности P исправной работы эле ментов по формуле

Формула из обретения

1. Устройство для определения показателей надежности объектов, содержащее генератор тактовых импульсов, ! +30968

Ю фиг 7 счетчик адреса и блок памяти, выход генератора соединен с входом счетчика адреса, выходы которого соединены с адресными входами блока памяти, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок ассоциативного запоминающего устройства, регистр, блок сумматоров и элемент до

ИЛИ-НЕ, информационные входы блока ассоциативного запоминающего устройства подключены к информационным выходам блока памяти, входы элемента

ИЛИ-НЕ соединены с выходами счетчика адреса, выход элемента ИЛИ-НЕ и выхо ды блока сумматоров подключены соответственно к управляющему и информационным выходам устройства, информационные выходы блока ассоциативного запоминающего устройства соединены поразрядно с установочными входами триггеров регистра, выходы которого подключены к входам блока сумматоров, причем блок ассоциативного запоминаю- 25 щего устройства состоит из ячеек по числу состояний объекта, каждая из которых содержит группу элементов

ИЛИ, группу элементов памяти и элемент И, число элементов в группах равно числу элементов объекта в ячейке, выходы элементов памяти группы соединены с первыми входами одноименных элементов ИЛИ группы, вторые входы и выходы которых соединены соответственно с одноименными разрядами информационных входов блока и входам элемента И ячейки, выходы которых подключены к соответствующим разрядам информационных выходов блока.

2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок сумматоров содержит группы сумматоров, объединенные в древовидную структуру, причем выходы каждых двух сумматоров предыдущих групп попарно соединены с входами сумматора последующих групп, выходы сумматора по-. следней группы подключены к выходам блока, а входы одноразрядных сумматоров первой группы соединены с входами блока.

1430968

Составитель А. Андерсон

Техред Л.Сердюкова Корректор M. Васильева

Редактор А. Ревин

Тираж 704 Подписное

ВПИИПИ Государственного комитета СССР по делам изобретений и открытий

li3035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5344/51

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4