Устройство выборки-хранения

Иллюстрации

Показать всеРеферат

Изобретение относится к аналоговой вычислительной технике, к устройствам выборки и хранения, в частности к устройствам обработки выходного сигнала микросхем с зарядовой связью (МСЗС). Цель изобретения - повышение точности и быстродействия устройства. Поставленная цель осуществляется за счет подачи в противофазе на вход усилителя 2, в том числе через элемент 6 в режиме хранения напряжения , ошибок, вызванных зарядом переключения сквозным прохождением сигнала, токами утечки ключевых МОП-структур. Точная компенсация этих эффектов позволяет значительно снизить емкость элементов 6, 7 и повысить быстродействие устройства. Устройство содержит ключевые элементы 1, 2, буферные усилители 3, 4, 5, накопительные элементы 6, 7 на конденсаторах. I ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУ БЛИН

„„SU„„1430989 A 1 (59 4 11 С 7 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4212315/24-24 (22) 16.03.87 (46) 15.10.88. Бюл. № 38 (71) Московский инженерно-физический институт (72) Ю. А. Зубец и В. Я. Стенин (53) 681.327.66 (088.8) (56) Авторское свидетельство СССР № 803013, кл. G 11 С 27/00, 1979.

Авторское свидетельство СССР № 894795, кл. G ll С 27/00, 1980. (54) УСТРОЙСТВО ВЫБОРКИ-ХРАНЕНИЯ (57) Изобретение относитСя к аналоговой вычислительной технике, к устройствам выборки и хранения, в частности к устройствам обработки выходного сигнала микросхем с зарядовой связью (МСЗС) . Цель изобретения — повышение точности и быстродействия устройства. Поставленная цель осушествляется за счет подачи в противофазе на вход усилителя 2, в том числе через элемент 6 в режиме хранения напряжения, ошибок, вызванных зарядом переключения сквозным прохождением сигнала, токами утечки ключевых МОП-структур. Точная компенсация этих эффектов позволяет значительно снизить емкость элементов 6, 7 и повысить быстродействие устройства. Устройство содержит ключевые элементы 1, 2, буферные усилители 3, 4, 5, накопительные элементы 6, 7 на конденсаторах. ил.

30989

10

Фор.)(ула изо(5)ре) ени. k

l4

Изобретение относится к аналоговой вычислительной технике, к устройствам обработки выходного сигнала микросхем с зарядовой связью (МСЗС) .

Цель изобретения — повышение точности и быстродействия устройства.

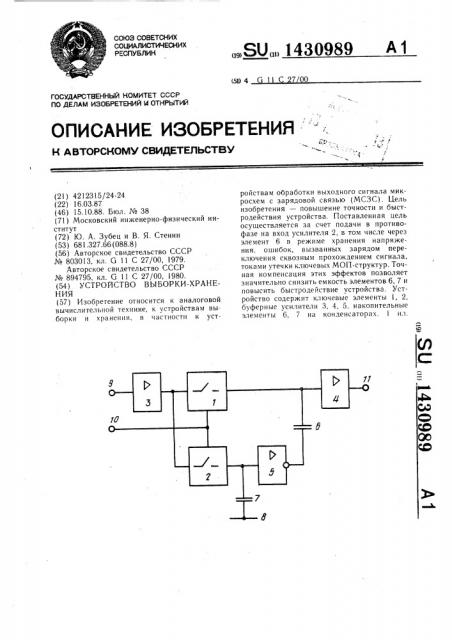

На чертеже представлена функциональная схема устройства.

Устройство содержит первый, второй аналоговые ключевые элементы 1, 2, йервый, второй буферные усилители 3, 4, третий инвертирующий буферный усилитель 5, первый, второй накопительные элементы 6, 7, на конденсаторах, шину 8 нулевого потенциала устройства, входы 9, 10 информационный и управляющий, информационный выход I.

Устройство работает следующим образом.

В режиме выборки при высоком значении логического сигнала на входе 10 устройства э.:)ех)е)(ть! 1, 2 открыты, потенциалы иа первом и втором выводах элементов 6, 7 уравниваются с потенциалом на выходе усилителя 3. На выходе усили-

1 еля 4, !) Ixo 1c 1! устрой(ства (1)()рх! ир(ется напряжение. соответствующее вь)ход)(оиру напряжени)о y(:H.fèr(!1я 1 )! напряжению на входе 9 устройсгва. Н3 выходе усилителя 5 втором выводе элемента 6 формируется иаltðÿæollèå, величина которого определяется коэффициентом передачи и напряжением сдв)и.! ин(к!)1ирующсго усилителя 5. H3llpBже!)Яем иа втором выводе элем IITd 7.

Б режим(«ранения при низком значеif!ill .!оп!(I(.ского сигнала на входе 1О устро()с в;! э. !ем(и I ы 1, 2 закрь(! ы. э,)емсltThl !), ((. ()XPtiil»kO! 3dlld(ННЫИ tl3 ftlt!(.Pва Ic врем ill! выборки заряд. поэтох)(потенциалы в! (ходов элементов 1, 2 (>ста)отея равIII Ixlff ()ото(ц(и()г)(H3 IIHT(. ðâ3 !(. времеtlll выборки. В режиме xpakfekfftsl напряжение

II3 выходе !! устройства также соответс !.вус потсll kkll Злу »3 первом выводе элемента 6 и. следовательно. напряжению на интервале времени выборки.

В рсжиме выборки иапря>кение сдвига устро)((тв(! определяется только суммой напряжений сдви! 3 усилителей 3, 4, при и Ilo,тьзоваиии в качестве элементов 1, 2 полупроводниковых структур с полевым эффектом, например ИС быстродействующих

МСП-клк>чей (например, 590КН8). При

l)(.påxoëå из режимов выборки в режим

x1)3 f I(II Il » э, )(> ы (II I>l 1, 2 . )3 ры Ваются и из их цепей уflj)3k),tåíèsf иа первый вывод элеxI(.IIT3 6 и первый вывоl элемента 7 посту!)и T заряд через паразитные емкости, величины которых близки для ключей 1, 2, так как itoT(.HIIII3лы на выводах элементов 1, 2 сохраняются практически равными в обоих режи I

При выбор» коэффициента усилителя 5

p;If)fit>fxf о! иоц((. )!ию вег)ичин емкостс и элементов 6, 7 приращение напряжен»» на обкладках ко!)денсатора 6 от заряда переклю2 чения элемента 1 будет равно и противоположно по знаку приращению напряжения на выходе усилителя 5, которое вызывается соответствующим изменением напряжения на элементе 7 от заряда переключения элемента 2. Таким образом, на входе и выходе усилителя 4 при переходе в режим хранения напряжение не изменится. Аналогично будут взаимокомпенсироваться помехи и невыбираемые сигналы, проходящие через закрытые элементы 1, 2 в режиме хранения устройства.

При выборе усилителей 4, 5 в качестве входных приборов с полевым эффектом точность устройства в режиме хранения будет фактически определяться разностью токов утечки элементов 1, 2 благодаря действию компенсирующей цепочки: элемент 7, усилитель 5, элемент 6. Для полной компенсации при заданной температуре источников погрешности емкость элемента 7 или коэффициенT передачи усилителя 5 могут быть подрегулировацы оез ущерба для работы устройства.

Использование в качестве элементов 1, 2

ИС с согласованными МОП-ключами позволяет иаибо.це Ilo. !HO реализовать достоинства устройства. например значительно одноврем Hll() с повышением точности увеличить быстродействие за счет снижения емкостей элементов 6, 7 ири заданной погрешности обработки си. нала.

Устройство выборки-х ра))ени», со.((рж3ц(ее !)ервый, второй и третий буферные у«и1lIT(ëè, первый и второ» накопительные элементы на ко)!денсаторах. Ilcðâûé II второй ключевые элементы, управляющие входы коTopbtx являются управляющим входом устройства, вход первого буферного усилителя является информационным входом устройства, а выход подключен к входу первого ключевого элемента, первые обкладки конденсаторов первого и второго накопительных элементов подключены соответственно к входам второго и третьего буферных усилителей, вторая обкладка конденсатора второго накоп)fòå fьного элемента подклko÷(. ffа к шине нулевого потенциала устройства. отличающееся тем, что, с целью повышени»i точности и упро(цения устройства, вход второго ключевого элемента подключеH к входу первого ключевого элемента, выходы первого и BTopot ключевых элементов tto3.клк>чены соответственно к входам второго и третьего буферных усилителей, вторая обк f;fat<;f конденсатора первого накопительного элемента подключена к выходу третьего буферного усилителя, выход второго буферного усилителя является информационным выходом устройства.