Устройство для вычисления симметрических булевых функций

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения быстродействующих арифметических устройств матричного типа. Цель изобретения 1 прощение конструкции за счет уменьшения числа внешних входов. Цель достигается тем, что устройство дЛя вычисления симметрических булевых функций трех переменных содержит три элемейта НЕ 1-3, тринадцать элементов ИЖ-НЕ 4-16, три информационных 17- 19 и четыре настроечных 20-23 входа, один выход 24. На информационные входы устройства подаются двоичные переменные х,х, на настроечные входы - сигналы настройки If , (Г, /Г , JT , значения которых принадлежат множеству 0, на выходе устройства реализуется симметрическая булева функция F F (х,х-,хр, определяемая вектором настройки 17(F) (fTj , IT,, fTj, ). ,1 ил., 1 табл. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИН (19) Ц11 (51)4 G 06 F 7/00

К . &я ) щ „.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

: (21 ) 4225652/24-24 (22) 07.04.87 (46) 23. 10.88. Бюл. Р 39 (72) Л.S.Авгуль и В,П.Супрун (53) 681.3 (088.8) (56) Авторское свидетельство СССР

У 1119003,.кл. G 06 F 7/00, 1984.

Интегральные микросхемы./Под ред.

Б.В,Тарабрина. — М.: Энергоатомиэдат, 1985 с.66. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ (57) Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения быстродействующих арифметических устройств матричного типа. Цель изобретения— упрощение конструкции за счет уменьшения числа внешних входов. Цель дос-тигается тем, что устройство дЛя вычисления симметрических булевых функций трех переменных содержит три элемента НЕ 1-3, тринадцать элементов

ИЛИ-НЕ 4-t6, три информационных 1719 и четыре настроечных 20-23 входа, один выход 24. На информационные входы устройства подаются двоичные переменные x1ôхт.х у на настроечные входы — сигналы настройки и, 811 и, rf3i значения которых принадлежат множеству (0,1); на выходе устройства реализуется симметрическая булева функция

F = F (х,,х,х ), определяемая векто- g ром настройки 7с (Р) = (rr,, ф>,, с -, 7к )., 1 ил., 1 табл. l432S00

Изобретение относится к вьгчислительной технике и микроэлектронике и предназначено для построения быстродействующих арифметических устройств матричного типа..

Цель изобретения — упрощение устройства за счет уменьшения числа внешних входов.

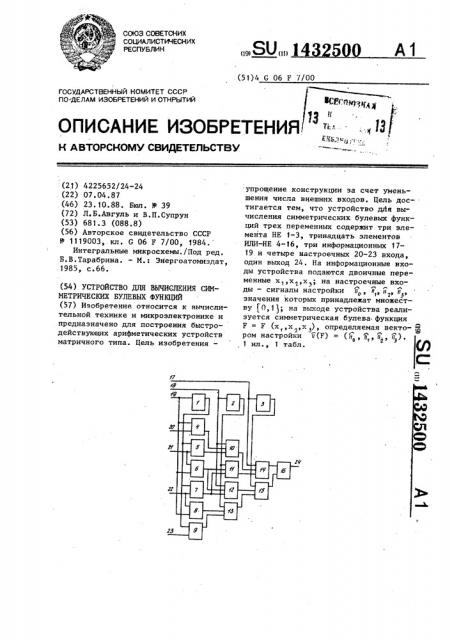

На чертеже представлена схема 10 предлагаемого устройства, Устройство содержит три элемента

Е 1-3, тринадцать элементов ИЛИ-НЕ

-16, три информационньгх входа 17-19, четыре настроечньгх входа 20-23 и выход 24.

Устройство работает следующим об,разом. !

На информационные входы 17-19 по1 лаются двоичные переменные х, х и 2О

1г соответственно, на настроечные 3 ходы 20-23 — сигналы настройки сортветственно /!, й, Г и il>, значе1 о

° ° ия которых принадлежат множеству ,(0,1, На вьгходе 24 реализуется сим- 25 етрическая булевая функция Р = Р(х,, 1 х ), определяемая вектором на строики II (F) = (й, II, II<, Il ) .

Значения компонент вектора II (F) 3O .и соответствующие ему реализуемые функции приведены в таблице, :Формула изобретения

Устройство для вычисления симметрических булевых функций„ содержащее три элемента НЕ, вход i-r"o (х=1,2,3) из которых соединен с i-м информационным входом устройства, о т л и ч а-4п ю щ е е с я тем, что, с целью упрощения за счет уменьшения числа внешних входов., оно содержит тринадцать элементов ИЛИ-НЕ, первый вход первого из которых соединен с первым настроечным входом устройства, второй настроечньгй вход которого соединен с первым входом второго и первым входом третьего элементов ИЛИ-НЕ, третий настроечный вход соединен с первым входом четвертого и первым входом пятого элементов ИЛИ-НЕ, четвертый настроечный вход соединен с первым входом шестого элемента ИЛИ-НЕ, второй вход которого соединен с вторым входом второго и вторым входом четвертого элементов ИЛИ-HE и выходом первого элемента НЕ, вход которого соединен с вторым входом первого, вторым входом третьего и вторым входом пятого элементов ИЛИ-НЕ, выход которого соединен с первым входом седьмого элемента ИЛИ-НЕ, второй вход которого соединен с выходом шестого элемента ИЛИ-НЕ, третий вход соединен с выходом второго элемента НЕ и первым входом восьмого элемента ИЛИ-НЕ, второй вход которого соединен с выходом третьего элемента ИЛИ-НЕ и первым входом девятого элемента ИЛИ-НЕ, второй вход которого соединен с выходом четвертого элемента ИЛИ-НЕ и третьим входом восьмого элемента ИЛИ-НЕ, третий вход соединен с входом второго

I элемента НЕ и первым входом десятого элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента ИЛИ-НЕ, третий вход соединен с выходом второго элемента ИЛИ-НЕ, а выход соединен с первым входом одиннад- цатого элемента KIN-НЕ, второй вход которого соединен с выходом восьмого элемента ИЛИ-НЕ, третий вход соединен с входом третьего элемента HE выход которого соединен с первым входом двенадцатого элемента ИЛИ-НЕ, второй вход которого соединен с выходом седьмого элемента ИЛИ-НЕ, третий вход соединен с выходом девятого элемента

ИЛИ-НЕ, а выход соединен с первым входом тринадцатого элемента KIN-НЕ, второй вход которого соединен с выходом одиннадцатого элемента ИЛИ-НЕ, а выход соединен с выходом устройства.

1432500

Сигналы настройки

Реализуемая функция на выходе 24

" 1 1

0 0

0 0

0

2 Э 1 3 2

0

1 3 1 2 2 9

0 х. vx v xg х„х х

0

0

Х1Х2Ч Х1ХЗ Ч Х2Х

R,x1Ч 1хь v x2x3Ч 1х2ХЗ

0 х чх чх

Составитель В.Сорокин

Редактор И.Горная Техред Л.Сердюкова Корректор М.Пожо

Заказ 5441/41 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

0 0 0

0 0 0

Х1Х2Х З

1хлх

Х Х2 Ч Х Х Ч Х2Х

Х Х2ХЗ Ч Х Х2Х Ч Х1Х2ХЗ

Х 1Х 2Х Ч Х Х2ХЗ х,х х ч х,х х ч х,х2Х, ч Х, 2Х

Х,Х Х Ч Х,Х2 . Ч Х1х Ч "2 Х q