Устройство для сравнения чисел

Иллюстрации

Показать всеРеферат

Устройство относится к вычислительной технике и ножет быть использовано в системах передачи информации со сжатием данных, а также в устройствах цифровой обработки сигналов. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности сравнения чисел с допуском. Устройство для сравнения чисел содержит две матрицы суммирующих ячеек 1, 2, регистр допуска 3, блок 5 буферной памяти, регистр 6 опорного числа, группы суммирующих ячеек 7, 8. Устройство осуществляет сравнение чисел с допуском, реализуя соотношение /ai -b/ r сР. Вычислительные операции и операции сравнения чисел с допуском в предлагаемом устройстве выполняются в параллель но-конвейерном режимео 2 ил. I (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (19) (11) (51)4 С 06 Р 7 0

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ сис ц, 1 rОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ! (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ (57) Устройство относится к вычислительной технике и может быть использовано в системах передачи ино (21) 4205997/24-24 (22) 04.03.87 (46) 23.10.88. Бюл. У 39 (71} .физико-механический институт им.Г.В.Карпенко (72) B.Â.Грицык, А.Ю,Луцык, И.Г.Любецкая; P.M.Ïàëåíè÷êà;, и Г.Т.Черчык (53) 681.325 (088.8) (56) Авторское свидетельство СССР

11 1254466, кл. С Об F 7/04, 1985.

Авторское свидетельство СССР

Р 1067499, кл. С 06 F 7/50, 1981. формации со сжатием данньм, а также в устройствах цифровой обработки сигналов. Цель изобретения — расширение функциональных возможностей устройства за счет обеспечения возможности сравнения чисел с допуском.

Устройство для сравнения чисел содержит две матрицы суммирующих ячеек

1, 2, регистр допуска 3, блок 5 буферной памяти, регистр 6 опорного числа, группы суммирующих ячеек 7, 8. Устройство осуществляет сравнение чисел с допуском, реализуя соотношение /а1-Ь/ (d, Вычислительные операции и операции сравнения чисел с допуском в предлагаемом устройстве выполняются в параллельно-конвейерном режиме. 2 ил.

1432502

Изобретение относится, к вычислительной технике и может быть использовано в системах передачи телеметрической информации со сжатием данных, а также в устройствах цифровой обработки сигналов.

Цель изобретения — расширение функциональных возможностей устройства за счет сравнения чисел с допус- 1Q ком.

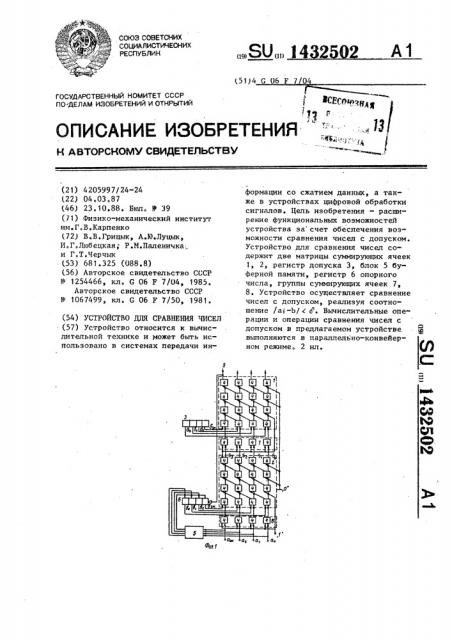

На фиг.1 представлена схема устройства для сравнения чисел для n=4 на фиг. 2 — функциональная схема ,. суммирующей ячейки. 15

Устройство для сравнения содержит матрицы 1 и 2 суммирующих ячеек, регистр 3 допуска, суммирующую ячейку 4, блок 5 буферной памяти, ре:гистр б опорного числа, группы 7 и 8 20 суммирующих ячеек, выход 9 знакового разряда устройства.

Суммирук щая ячейка 4 содержит элемент И 10, элемент ИСКЛ10ЧАЮЩЕЕ ИХП4

11 и два триггера 12 и l3. 25

Устройство для сравнения чисел с допуском реализует соотношение

/а — b/ (д .

Устройство работает следующим ÇÎ образом.

Вторая матрица 2 осуществляет суммирование числа а; с числом Ь. и-разряцное число а, поступившее по группе входов. и преобразованное в дополнительный код в группе 8 суммирующих ячеек 0-й строки и (2, n)-й ячейки шины логической единицы, подается на первые входы ячеек 4 первой строки первой матрицы. Вторые АО входы суммирующих ячеек первой строки соединены с выходами регистра.

Триггеры 12 и 13, входящие в ячеики

4„ запоминают на время одного такта результат суммирования и переноса.

С приходом каждого очередного тактового импульса на входную шину заносятся новые коды входных чисел, а (i„ j)-е ячейки, где i=2„...n,,1 = 1,...,п, производят суммирование суммы, полученной в предыдущем такте

50 в ячейке тэго же столбца, (i-1)-й строки с переносом из ячейки (j+1)го столбца, (i-1)-й строки. Таким образом, операция суммирования выполняется в параллельно-конвейерном

55 режиме.

Результат суммирования числа Ь с числом а; — число S поступает на первые входы суммирующих ячеек группы 7, на вторые входы которых, а также на второй вход (2,п)-й ячейки первой матрицы подается сигнал с инверсного выхода (п,1)-й суммирующей ячейки второй матрицы, С выхода суммирующих ячеек группы 7 число S записанное в дополнительном коде, поступает на первые входы первой строки ячеек первой матрицы. Вторые входы первой строки матрицы 1 соединены с выходом регистра 3 допуска °

Первая матрица 1 осуществляет операцию сложения допуска S и результата суммирования опорного числа Ь с а . Работа первой матрицы аналогичйа работе второй матрицы.

Когда на выходе 9 знакового разряда, который является выходом устройства для сравнения чисел, сигнал

"1", и, следовательно /а;-Ь(o d, на вход управления записью регистра б подается сигнал "1", который переключает регистр на запись числа а., I поступающего с блока 5.

Формула изобретения

Устройство для сравнения чисел, содержащее первую матрицу из п суммирующих ячеек, где n — разрядность выход cуммы (:, 1 ) -и суммирующей ячейки матрицы (z. — номер строки матрицы, i=l,... п-1;

j — номер столбца матрицы, j=1...,n), соединен с первым входом (х+1, j)-й суммирующей ячейки матрицы, выход переноса (i,g)-й суммирующей ячейки матрицы, где я = 2,...„n, соединен с вторым входом соответствующей (i+1, р-1)-й суммируюшей ячейки матрицы„ вторые входы (k,ï)-х сумьырующих ячеек матрицы, где k =З,...,n, соединены с входом логического нуля устройства, выход (n 1)-й суммирующей ячейки матрицы является выходом знакового разряда устройства, о т л и ч а ю ш е е с я тем„ что, с целью расширения функциональных воз-. можностей устройства за счет сравнения чисел с допуском, в него введены первая и вторая группы суммирующих ячеек, вторая матрица из п сум" мирующнх ячеек, блок буферной памяти, регистр опорного числа, регистр допуска, выходы разрядов которого соединены с первыми входами суммирующих ячеек первой группы, вторые входы коВБЦЮ

УУРРГУЮЯ

ЯюИ

СфюР9/

Составитель В.Козлов

Техред П.Сердюкова Корректор С.Черни

Редактор И.Горная

Заказ 5441/41 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Гаушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 торых соединены с выходами суммы соответствующих суммирую цих ячеек второй группы, первые входы всех суммирующих ячеек второй группы соединены с вторым входом (2,n)-й суммирующей ячейки первой матрицы и с инверсным выходом суммы (n,1)-й суммирующей ячейки второй матрицы, выходы суммирующих ячеек п-й строки которой соединены с вторыми входами. соответствующих суммирующих ячеек второй группы, выход суммы (i,j)-й суммирующей ячейки второй матрицы соединен с первым входом соответствующей (i+1, j)-й суммирующей ячейки этой матрицы, выход переноса (i,я)-й суммирующей ячейки второй матрицы соединен с вторым входом соответствующей i+1 g-1)-й сум432502 4 мирующей ячейки этой матрицы, вторые входы (k,n)-х суммирующих ячеек второй матрицы соединены с входом логического нуля устройства, второй вход (2,n)-й суммирующей ячейки второй матрицы и первые входы суммирующих ячеек первой группы соединены с входом логической единицы, устройства, вторые входы суммирующих ячеек второй группы являются входами числа устройства и соединены с входами соответствующих разрядов блока буферной памяти, информационные выходы которого соединены с информационными входами регистра опорного числа, вход управления записью которого соединен с выходом (п, 1)-й суммирующей ячейки первой матрицы °