Устройство для контроля цифровых блоков

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники, в частности к средствам автоматизированного контроля цифровых объектов, и может быть использовано для проверки цифровых схем, построенных с испо:пьзованием методов структурного проектирования. Цель изобретения состоит в повышении достоверности контроля за счет обеспечения возможности автоматизированного формирования заданной тестовой последовательности в произвольной точке схемы. Устройство состоит из счетчика, контролируемого цифрового блока, первого и второго блоков памяти , блока микропрограммного управления , информационного регистра, мультиплексоров, регистров сдвига, первого, второго, третьего коммутаторов , первого и второго счетчиков адреса , четвертого коммутатора, группы элементов И, группы элементов ИЛИ, с буферного регистра, первого и второ го триггеров, элемента И и схемы сравнения . Использование микропрограммной памяти в блоке управления позволяет значительно повысить эффективность и информативность результатов контроля. 3 ил. Sfi (Л С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (!9) (И) 25 0 А1 (51) 4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ е аа,е.е» ., е у, Ъ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4210251/24-24 (22) 13.03. 87 (46) 23.10.88.,Б)бп.)) 39 (71) Минский радиотехнический институт (72) И.П.Кобякр В.А.Липницкий и В.М.Галецкий (53) 681.3 (088.8) (56) Авторское свидетельство СССР

В 1174931, кл. G 06 F 11/26, 1985.

Авторское свидетельство СССР

9 1149265, кл. G 06 F 11/26, 1985. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ (57) Изобретение относится к области вычислительной техники, в частности к средствам автоматизированного контроля цифровых объектов, и может быть использовано для проверки цифровых схем, построенных с использованием методов структурного проектирования.

Цель изобретения состоит в повышении достоверности контроля за счет обеспечения возможности автоматизированного формирования заданной тестовой последовательности в произвольной точке схемы. Устройство состоит иэ счетчика, контролируемого цифрового блока, первого и второго блоков памяти, блока микропрограммного управления, информационного регистра, мультиплексоров, регистров сдвига, первого, второго, третьего коыкутаторов, первого и второго счетчиков адреса, четвертого коммутатора, группы элементов И, группы элементов ИЛИ, с буферного регистра, первого и второго триггеров, элемента И и схемы сравнения. Использование микропрограммной памяти в блана управления по- С зволяет значительно повысить эффективность и информативность результатов контроля. 3 ил.

1432536

Изобретение относится к вычисли- тельной технике, в частности к средствам автоматизированнсго контроля цифровых объектов, и может быть использовано для проверки цифровых схем, построенных с использованием методов структурного проектирования.

Цель изобретения — повьппение достоверности контроля. 10

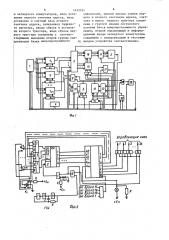

На фиг. 1 представлена блок-схема устройства на фиг. 2 — функциональ( ная схема блока управления на фиг.ЗУ, функциональная схема схемы сравнения.

Устройство (фиг. 1) содержит счет- 15 чик 1, контролируемый цифровой блок

2, блок 3 памяти, блок 4 микропрограммного управления, коммутатор 5, ре- . гистр 6 маски, К мультиплексоров 7, К регистров 8 сдвига, коммутатор 9, 20 коммутатор 10, первый счетчик 11,адреса, блок 12 памяти,, коммутатор 13, счетчик 14 адреса, группу 15 элементов И, группу 16 элементов ИЛИ, буферный регистр 17, элемент И 18, триггеры 19 и 20, схему 21 сравнения.

Устройство работает следующим образом.

В зависимости от структуры блока

2 может быть выбран необходимый ре- 30 жим работы формирователя тестов. Рассмотрим, например, тестирование схемы, реализованной с использованием

Структурных методов контролепригодного проектирования. Сущность конт- 35 роля такого устройства состоит в раздельном тестировании комбинационной и последовательной частей. Режим создания заданной тестовой последовательности в произвольной комбинацион- 10 ной части схемы укрупненно описывается следующим алгоритмом.

1) В блок 3 от внешнего носителя записывается двоичная последовательность, в которой логическая "1" присутствует только в ячейке памяти с адресом, кратным степени двойки.

2) Из блока 3 информация переписывается в один из регистров 8..

3) ПРоцедура, описанная в первом и втором шаге, повторяется столько раз, сколько входов имеет цифровой блок 2. При этом необходимо, чтобы единичный бит информации каждый раз пРисутствовал В новой ячейке памяти, адрес которой кратен степени двойки.

4) Функции счета, формируемые счетчиком 1, через мультиплексоры 7 подаются на входы коммутатора 5 и через элементы ИЛИ группы 16 и регистр

17 подаются на входы блока 2. Последовательность сигналов, снимаемая в каждый такт времени, записывается в блок 12.

5) Реакция контроля переписывается из блока 12 в один из регистров 8.

6) С помощью счетчика 1 кодовые комбинации перебираются на входах мультиплексоров 7. Последовательность символов с выхода мультиплексора, определенного в пункте 5, через коммутатор 5 записывается в блок 12.

7) Тестовая последовательность, которую необходимо сформировать в указанной вьппе точке блока 2, вводится через коммутатор 10 в блок 3.

8) Осуществляется перезапись информации из блока 3 в один из регистров 8.

9) С помощью счетчика 1 кодовые комбинации перебираются на входах мультиплексоров 7, Последовательность символов с выхода мультиплексора 7, определенного в пункте 8, через коммутатор 5 записывается в блок 3.

10) Информация из блока 3 переписывается во все регистрь1 8.

11) Блок 12 переводится в режим чтения, а триггер 20 устанавливается в единичное состояние. При считывании первого единичного бита из блока 12 триггер 19 формирует сигнал управления для блока 4, что приводит к останову счетчика 14 и записи его содержимого в регистр 6.

12) С помощью счетчика 1 кодовые комбинации перебираются на входах мультиплексоров 7. Последовательность символов с выхода произвольного мультиплексора переписывается в блок 3.

13) Вместо эталонного изделия к устройству подключается цифровой блок 2 и функции счета, преобразованные мультиплексорами 7 через коммутатор 5, группу 15, группу 16, регистр

17„ подаются на входы контролируемого цифрового блока 2.

14) Реакция контролируемого цифрового блока 2 в заданной точке в каждый такт времени через коммутатор 13 записывается в блок 12.

15) Осуществляется чтение блока 3 и блока 12 и сравнение считанной информации на схеме 21. Свечение индикатора по окончании сравнения свидетельствует о неправильномфункциониро2530

40

45 тьего и четвертого коммутаторов, вход разрешения схемы сравнения сое50

143 вании проверяемой схемы в выбранной точке. Отсутствие свечения свидетельствует об исправности контролируемого блока.

Для формирования на входах схемы необходимых тестовых последовательностей необходимо выполнить следующие шаги.

В блок 3 от внешних носителей записывается тестовая последовательность, которую необходимо сформировать на

i-м входе контролируемого блока.

Из блока 3 информация переписывается в i-й регистр 8.

Функции счета, формируемые счетчиком 1, подаются на входы мультиплексоров 7. Последовательность символов с выхода i-го мультиплексора 7 через коммутатор 5 записывается в блок 3.

Информация из блока 3 переписывается в i-й регистр 8 °

Далее данный алгоритм повторяется до тех пор, пока все регистры 8 не будут заполнены соответствующей информацией. Затем включается режим тестирования. При этом функции счета счетчика 1, преобразованные мультиплексорами 7, подаются на входы коммутатора 5, и далее через группу 16 и регистр 17 — на входы блока 2.

Формула изобретения

- Устройство для контроля цифровых блоков, содержащее счетчик, первый блок памяти, блок микропрограммного управления, регистр маски, причем счетный вход счетчика и синхровход регистра маски соединены с. первым и вторым выходами первой группы синхI ровыходов блока микропрограммного управления, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, в него введены К .мультиплексоров, где К вЂ” число входов контролируемого цифрового блока, К регистров сдвига, четыре коммутатора, первый и второй счетчики адреса, второй блок памяти, группа элементов

И, группа элементов ИЛИ, буферный регистр, первый и второй триггеры, элемент И и схема сравнения, причем разрядные выходы счетчика соединены с группой управляющих входов i-го мультиплексора (i=1,К), выходы мультиплексора группы соединены с информационными входами первого коммутатора, группа разрядных выходов К реги5

25 стров сдвига соединена с группой информационных входов соответствующих мультиплексоров группы, информационные входы К регистров сдвига соединены с выходами второго коммутатора, первая и вторая группы информационных входов которого соединены с группой выходов первого и второго блоков памяти соответственно и с первой и второй группами информационных входов схемы сравнения, адресные входы первого и второго блоков памяти соединены с разрядными выходами первого и второго счетчиков адреса соот6етственно, информационный вход и вход записи второго блока памяти соединены с первым и вторым выходами третьего коммутатора соответственно, информационный вход и вход записи первого блока памяти соединены с первым и вторым выходами четвертого коммутатора соответственно, третий выход которого соединен со счетным входом первого счетчика адреса, первая группа выходов первого коммутато- ра соединена с первыми входами элементов ИЛИ группы, вторая группа выходов первого коммутатора соединена с первыми входами элементов И группы, вторые входы которых соединены с соответствующими выходами регистра маски, выходы элементов И группы соединены с вторыми входами элементов ИЛИ группы, выходы которых соединены с информационными входами буферного регистра, выходы которого явля-. ются выходами устройства для подключения к входам контролируемого цифроваго блока, разрядные выходы второго счетчика адреса соединены с информационными входами регистра маски, выход первого коммутатора соединен с первыми информационными входами тре динен со стробирующим выходом блока микропрограммного управления, информационный вход третьего коммутатора является входом устройства для подключения к выходам контролируемого,цифрового блока, первый вход элемента И соединен с выходом второго блока памяти, второй вход элемента И соединен с выходом второго триггера, выход элемента И соединен с входом установки первого триггера, синхровходы К регистров сдвига, входы управления первого, второго, третьего

143253 ) и четвертого коммутаторов, вход установки первого счетчика адреса, вход установки и счетный вход второго счетчика адреса, синхровход буферно го регистра, входы сброса и установки второго триггера, вход сброса первого триггера соединены с соответствующими выходами второй группы син хровходов блока микропрограммного

1 управления, причем выходы заемов первого и второго счетчиков адреса, счетчика и выход первого триггера соединены с группой входов логического условия блока микропрограммного управления, второй управляющий и информационные входы четвертого коммутатора. соединены с синхровходами и тестовым входом устройства соответственно.

1432533

Ь@ &o)1 Ю

Ап для 12

Ам Йюки 4

Составитель В.Леоненко

Редактор Е.Папп Техред М.Дидык Корректор С.Шекмар

Заказ 5442/42 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4