Устройство для отображения информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении устройств отображения с телевизионным методом построения изображения. Цель изобретения - повышение точности устройства . Устройство содержит с перво

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„Л(, 14 24 (51) 4 G 09 G 1/16

ОПИСАНИЕ ИЗОБРЕТЕНИИ « . Ф»»»

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4160872/24-24 (22) 15.12.86 (46) 23. 10.88. Бюл. Р 39 (72) В.А.Шайда (53) 681 ° 327.11(088.8) (56) Патент США Р 4128838, кл. G 01 S 7/06, опублик. 1978.

Патент Великобритании Р 2073988, кл. Н 04 К 5/122, опублик. 1981. (54) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРИЛЦИИ (57) Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении устройств отображения с телевизионным методом построения изображения. Цель изобретения — повышейие точности устройства. Устройство содержит с перво1432594 го по четвертый блоки 1 — 4 оперативной памяти, датчик 5 кодов яркости, формирователи адреса записи по координатам Y 6 и Х 7, формирователь 8 телевизионной развертки, блок 9 буферной памяти, блок 10 индикации, с первого по четвертый умножители 11 — 14, первый 15 и второй 19 распределители импульсов, первый коммутатор 16, элемент НЕ 17, сумматор 18, второй комИзобретение относится к вычислительной технике и автоматике и может быть использовано при построении устройств отображения с телевизионным методом формирования изображения.

Цель изобретения — повышение точности устройства.

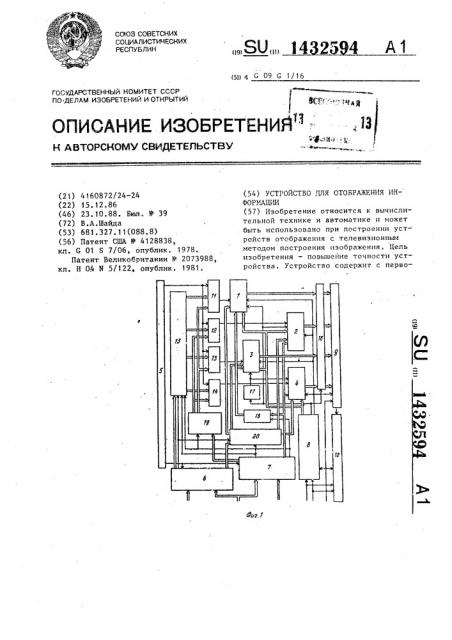

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — структурная схема второго коммутатора; на фиг.3 блок-схема второго распределителя импульсов; на фиг, 4 — блок-схема пер-. вого распределителя импульсов.

Устройство содержит первый 1, вто- 155 рой 2, третий 3 и четвертый 4 блоки оперативной памяти, датчик 5 кодов яркости, формирователи 6 и 7 адреса записи координаты Y и координаты Х соответственно, формирователь 8 теле- 2р визионной развертки, блок 9 буферной памяти, блок 10 индикации, первый 11, второй 12, третий 13 и четвертый 14 умн,æèòåëè, первый распределитель 15

1 импульсов, первый коммутатор 16, элемент НЕ 17, сумматор 18, второй распределитель 19 импульсов, второй коммутатор 20, первь ;.21, гторой 22, третий 23 и четвертый 24 сумматоры, дешифратор 25, первый 26 и второй 27 блоки управляемых инверторов, элемент

НЕ 28, третий 29, четвертый 30, пягый 31:I:I."I:òîé 32 блоки управляемых инвертор1 н, первый 33, второй 34, третий 3 1 и четверт11й 36 элементы 35 !

ПИ, д."IIII(ритор 17, управляемый иняерт >г 1, 1ройеl:. раб11тает следующим об40 ()аэ:. -1. мутатор 20 с соответствующими связями. Повышение точности отображения достигается за счет раздельной записи взвешенных кодов яркости точек в блоки 1 — 4 оперативной памяти, таким образом, что отсутствуют потери информации, возникающие при дискретизации математических координат отсчетов при формировании растрового массива.

4 ил.

Блоки 1-4 оперативной памяти имеют матричную структуру и предназначены для хранения кодов яркости элементов lзображения. Общее число ячеек блоков памяти равно числу элементов иэображения, а число разрядов, храняшихся в отдельной ячейке, — разряд" ности кода яркости. Определенный блок оперативной памяти содержит четвертую часть ячеек, требующихся для хранения всего объема изображения.

Запись осуществляется в одну иэ ячеек блоков 1-4 оперативной памяти, считывание — одновременно из группы ячеек блоков памяти. Адрес ячейки для записи определяется по кодам на входах адресов записи блоков 1-4 оперативной памяти, адрес считывания по кодам на входах адресов считывания. Особенность блоков оперативной памяти 1-4 заключается в том, что они осуществляют накопление информации: перед записью в выбранную ячейку пришедший на вход блока оперативной памяти код яркости складывается с кодом, считанным из выбранной ячейки.

Этим устраняются потери полезного сигнала, поскольку один отсчет полезного сигнала может распределяться по четырем ячейкам разных блоков 1

4 памяти.

Датчик 5 кодов яркости на первом выходе формирует последовательно, один за другим, коды уровня яркости для каждого отсчета входного иэображения, а на втором выходе — импульсы начала развертки записи, например зондирующие импульсы РЛС и тактовые импульсы РЛС по временному положению, связанные с отсчетами кода яркости. з

Формирователи 6 и 7 адреса записи координат Y и Х соответственно формируют коды адреса записи отсчетов входного изображения, приходящих с

6 датчика кодов яркости, а также коды коррекции, численно представляющие собой смещение точного положения отсчета входного изображения относительно точек дискретного телевизион- 1ц ного растра, формируемого на экране блока индикации.

На управляющий вход формирователей 6 и 7 поступают тактовые импульсы РЛС и импульсы начала развертки 15 записи. На первый информационный вход формирователей 6 и 7 поступает код угла наклона линии, а на второй информационный вход — координаты начала линии 20

На первом выходе формирователей Ь и 7 формируются старшие разряды кода адреса записи, на втором выходе— младший разряд кода адреса, на третьем — коды коррекции. 25

Формирователь 8 телевизионной развертки по приходящим на его входы кадровым и строчным синхроимпульсам и тактовым импульсам, формирует на первом и втором выходах коды разверт- 30 ки по строке и по кадру, а на третьем управляющем выходе — сигнал переключения режимов записи-считывания.

Блок 9 буферной памяти регистрового типа преобразует поступающие на входы параллельные коды амплитуды в последовательно следующие группы отсчетов телевизионного иэображения.

На вход синхронизации блока буферной памяти поступают тактовые импульсы, 4р а на управляющий вход — импульсы записи параллельного кода, поступающего на информационные входы сумматора 18.

Блок 10 индикации является теле- 45 визионным видеоконтрольным устройством (ВКУ) и преобразует коды яркости элементов изображения, поступающие на его вход в строчно-кадровом режиме, в яркость соответствующих элемен- 50 тов изображения. Синхронизация работы блока 10 с процессом считывания ин.— формации осуществляется с помощью строчных, каДровых синхроимлульсов и тактовых импульсов, поступающих с входов устройства.

Умножители 11-14 производят перемножение между собой кодов, поступающих на их входы. Первый распредели94 тель 15 импульсов коррекции координаты Y распределяет коды коррекции, поступавшие на его второй информационный вход по четырем выходам. Это распределение осуществляется с учетом расположения ячеек блоков 1-3 оперативной памяти в выбранной группе.

Первый коммутатор 16 имеет четыре информационных входа и четыре выхода, а также вход управления. В зависимости от потенциала на входе управления коммутатор 16 производит соединение определенных входов с соответствующими выходами. Например, при логическом нуле на входе управления первыйчетвертый информационный входы комму,татора связаны с одноименными выходами коммутатора 16, а при логической единице на входе управления первый и второй информационные входы связаны соответственно с третьим и четвертым выходами, а третий и четвертый информационные входы связаны с, первым и вторым выходами коммутатора 16.

Сумматор 18 производит сложение старших разрядов кода адреса по координате Х с младшими разрядами кода адреса rio этой же координате.

Второй распределитель 19 импульсов коррекции координаты Х распределяет коды коррекции, поступившие на информационный вход, на два выхода.

Это распределение производится с учетом расположения ячеек блоков 1-4 оперативной памяти в выбранной группе, что задается кодом, поступающим на управляющий вход распределителя 19.

Второй коммутатор 20 производит распределение кодов адреса координаты У по четырем выходам. Код адреса записи поступает на третий информационный вход второго коммутатора 20.

На первый, второй и четвертый входы поступают соответственно первый и второй разряды кода адреса записи координаты Х и младший разряд кода адреса записи координаты Y. С помощью кодов на первом, втором и четвертом входах коммутатора 20 учитывается изменение порядка распределения адреса записи в зависимости от расположения ячеек блоков оперативной памяти

1-4 в выбранной группе.

При записи в блоки 1-4 оперативной памяти линии с наклоном 8, состоящей иэ совокупности равностоящих отсчетов,,коды яркости отсчет . последова143?594 тельно, отсчет за отсчетом, подаются на первые входы умножителей 11-14, с выходов которых поступают на входы видеосигнала соответствующих блоков

1-4 памяти. Одновременно с второго выхода датчика -5 кодов яркости на первые входы формирователей б и 7 поступают импульсы начала развертки записи и тактовые импульсы. Каждому от- 10 счету с первого выхода датчика 5 соответствует определенное количество (например, один) тактовых импульсов.

По коду угла 6 наклона линии на . вторых входах формирователей б и 7 для каждого отсчета формирователи 6 и 7 вырабатывают коды положения отсчета по координатам Y и Х соответственно, которые можно представить в виде У+ У и У+АХ, где Y и Х вЂ” целые час-20 ти кодов; 5У и ЬХ вЂ” дробные части, При этом старшие разряды кода положения Х и У (целые .части) определяют ячейку блоков памяти с таким адресом и соответствующий элемент изображения 25 на экране блока 10, а младшие разряды кода положения поступившего отсчета относительно элемента изображения с координатами Х, Целая часть кода положения отсчета по координатам Х и У, представляющая собой адрес записи по соответствующей координате Х и У, с первых выходов формирователей 6 и 7 поступает на соответствующие адресные входы

35 блоков 1-4 оперативной памяти и используется для адресования одной ячейки в каждом блоке 1-4. При этом коды адреса по координате Х поступают на первые адресные входы блоков 2 и 4 непосредственно, а на первые адресные входы блоков 1 и 3 — через сумматор 18, на второй вход которого поступает младший разряд кода адреса по координате Х. По координате Y ко45 ды адреса поступают на четвертые адресные входы блоков 1-4 через второй коммутатор 20. Совокупность кодов адреса записи на входах блоков 1-4 определяет выбор четырех ячеек (по од50 ной из каждого блока) с координатами (Х,Y), (X+1, Y),(Х+1, У+1), (Х,У+1), окружающими точное положение отсчета.

Дробная часть кодов положения отсчета ЬХ, ЬУ, определяющая смещение 55 отсчета относительно положения элемента изображеш я с координами Х, Y поступает с выходов формирователей 6 и 7 на распределители 19 и 15 импульсов и определяет, какая часть кода яркости в отсчете попадает в каждую иэ выбранных ячеек. Код, попадающий на вход видеосигнала отдельного блока 1-4 оперативной памяти, определяется перемножением кода яркости В с одним из коэффициентов коррекции b», Ь„ 1 координаты Х и Ьч, Ьч+» координаты Y в умножителях 11-14.

Значения коэффициентов Ь„, byes поступают на входы умножителей 11-14 с распределителя 19 кодов коррекции координаты Х, а коэффициенты Ъ,bq+g поступают на входы умножителей 11-14 с выходов распределителя 15 импульсов. Какие именно коэффициенты (Ь или Ь„., Ь или Ь (поступают на входы конкретного умножителя 11-14, определяется тем, какое положение

B выбранном квадрате из 2х2 ячеек занимает ячейка блока памяти, связанная с этим умножителем. Для блока оперативной. памяти, ячейка которого занимает левый нижний угол в выбранном квадрате, умножение кода яркости

В производится на коэффициенты Ь» и

Ьу, для блока памяти, ячейка которого занимает правый верхний угол, — Ь| и b >,„ а для блока памяти, ячейка которого занимает правый нижний угол, — Ь,q и Ь . Значения коэффициентов Ь„ и Ь .,1 определяются положением отсчета относительно узлов координатной сетки $ X. Чем ближе голожение отсчета к ячейке, тем больше коэффициент, соответствующий этой ячейке и тем меньше второй коэффициент, определяющий часть кода яркости, попадающую в противоположные ячейки выбранного квадрата.

При совпадении координат ячейки с координатами отсчета (Х=О, Y=O) весь код яркости поступает в эту ячейку (поскольку соответствующие коэффициенты для нее равны 1), а во все остальные ячейки записывается код яркоети, равный нулю, поскольку один либо оба коэффициента для них равны О. В случае, если лишь одна координата отсчета совпадает с координатой ячеек (например, координата Х, ЬХ=О), код яркости В распределяется лишь между двумя ячейками (поскольку один из коэффициентов Ь„ или Ь„ r равен нулю, а другой — единице). Эти ячейки расположены в выбранном квадрате одна над другой. Сумма всех коэффициентов Ь„+Ь,,» +bq+b9e< =1, чем

143259ф обеспечивается суммарная яркость четырех ячеек, формирующих данный отсчет, равная яркости отсчета B c датчика 5, независимо ат смещения от- 5 счета относительно координат ячеек.

Сумма коэффициентов Ь» и b»« равна единице независимо от значения координаты Х.

Аналогичное распределение имеют и коэффициенты Ьо и Ьу.» . Коэффициент

Ь»,» численно представляет собой кад смещения Х по координате Х положения входного отсчета относительно ячейки с координатой Х, а коэффициент Ъ„ код смещения относительно ячейки с координатой Х+1. Соответственно Ьч+» представляет собой расстояние по координате Y положения отсчета относительно ячейки с координатой У, а by — 20 относительно ячейки с координатой Y+1, Коэффициенты Ъ|,» и Ь»i» равны 6У и ДХ соответственно, а Ь =1-6У, Ь»=

=1-6Х., 1ля отсчета, находящегося на рав- 25 ном расстоянии от каждой из четырех окружающих его ячеек, Ь»=Ь»i»= =Ь =

=b> =Д =0,5 и в каждую ячейку адресуются коды яркости, составляющие 0,25 В.

Для отсчета, положение которого совпадает с центром элемента отображения на экране, 6 X=6Y=O и b„=b =O, а Ь».»

Ь,» =1. Наконец, для отсчета, занимающего промежуточное положение относительно окружающих его ячеек, Ь»=Ьч=

=0,25, а Ь„,» =Ьч,» =0,75 и код яркости, 35 попадающий в верхнюю правую ячейку, составляет примерно 0,56 В, в верхнюю левую ячейку и нижнюю правую — по

0,19 В, в нижнюю левую ячейку 0,06 В. 40

При этом в отдельных ячейках блоков памяти коды яркости от разных отсчетов суммируются.

Распределение информации между ячейками блоков 1-4 памяти обеспечи45 вает для любых координат Х и Y возможность одновременной записи в четыре ячейки, расположенные квадратом

2х2 ячейки, с привязкой координаты

X Y к левой нижней ячейке квадрата, . а также считывание информации с максимально возможным быстродействием следования отсчетов на входе блока 10 индикации, в четыре раза превышающим быстродействие отдельного блока 1-4 памяти.

Формула изобретения

Устройство для отображения информации, содержащее первый, второй, третий и четвертый блоки оперативной памяти, датчик кодов яркости, формирователь адреса записи координаты У, формирователь адреса записи координаты Х, формирователь телевизионной развертки, блок буферной па»»яти и блок индикации, информационный вход которого подключен к выходу блока буферной памяти, тактовый вход которого и тактовые входы блока индикации и формирователя телевизионной развертки являются тактовым входом устройства, входом кадровой синхронизации которого являются входы кадровой синхронизации блока индикации и формирователя телевизионной развертки, входы строчной синхронизации которых являются входом строчной синхронизации устройства, первым информационным входом которого являются первые информационные входы формирователей адресов записи координат Х и Y первый выход формирователя адреса записи координаты Х соединен с первыми адресными входами второго и четвертого бланков оперативной памяти, вторые адресные входы которых и первые адресные входы первого и третьего блоков оперативной памяти подключены к первому выходу формирователя телевизионной развертки, второй выход которого соединен с вторым адресным входом первого и третьим адресным входом второго блоков оперативной памяти, управляющие входы первого, второго, третьего и четвертого блоков оперативной памяти и управляющий вход блока буферной памяти подключены к третьему выходу формирователя телевизионной развертки, третий адресный вход первого блока оперативной памяти соединен с вторым адресным входом третьего блока оперативной памяти, третий адресный вход которого соединен с третьим адресным входом четвертого блока оперативной памяти, первый выход датчика кодов яркости соединен с управляющими входами формирователей адресов записи координат Х и У, о т л и ч а ю щ е е с я тем, что, с целью повышения точности устройства, оно дополнительно содержит первый, второй, третий и четвертый умножители, управляющие входы которых подключены к второму выходу датчика кодов яркости, первый распределитель импульсов, выходы которого подключены к первым информационным входам первого, второго, третьего и четвертого

1432594

10 умножителей, выходы которых соединены соответственно с информационными входами первого, второго, третьего и четвертого блоков оперативной памяти, второй распределитель импульсов, пер5 вый выход которого соединен с вторы;ми информационными входами первого и третьего умножителей, вторые информационные входы второго и четвертого

: умножителей соединены с вторым выходом второго распределителя импульсов, элемент НЕ, сумматор и первый и второй коммутаторы, информационные входы первого коммутатора подключены со- g ответственно к выходам первого, вто, рого, третьего и четвертого блоков

: ;оперативной памяти, выходы первого, .коммутатора соединены с информационными входами блока буферной памяти, 20 управляющий вход первого коммутатора и вход элемента НЕ соединены с вторым выходом формирователя телевизионной развертки, выход элемента НЕ подключен к третьим адресным входам третье- 25 го и четвертого блоков оперативной памяти, третий адресный вход первого и второй адресный вход третьего блоков оперативной памяти соединены с выходом сумматора, первый информационный вход которого подключен к первому выходу формирователя адреса записи координаты Х, второй выход которого подключен к второму информационному входу сумматора, первому информационному входу второго коммутатора, управляющему входу второго распределителя импульсов и первому информационному входу первого распределителя импульсов, второй информационный вход которого подключен к первому выходу фор мирователя адреса записи координаты У, второй информационный вход которого является вторым информационным входом устройства, третьим информационным входом которого является второй информационный вход формирователя адреса записи координаты Х, третий выход которого соединен с вторым информационным входом второго коммутатора, первым управляющим входом первого распределителя импульсов, второй управляющий вход которого и первый управляющий вход второго коммутатора подключены к второму выходу формирователя адреса записи координаты У, третий выход которого соединен с третьим информационным входом второго коммутатора, первый, второй, третий и четвертый выходы которого подключены соответственно к четвертым адресным входам первого, второго, третьего и четвертого блоков оперативной памяти, информационный вход второго распределителя импульсов соединен с четвертым выходом формирователя адреса записи координаты Х.

1432594

Составитель О.Цапко

Редактор Б.Пс траш Техред Л.Олийнык Корректор О.Кравцо-.а .Зака..» 448!45 Тираж 459 Подписное

ВНИИЛИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4