Многоканальное оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к запоминвнщим устройствам, и может быть использовано в многопроцессорных и многомашинных вычислительных системах в качестве общей оперативной памяти. Целью изобретения является расширение области применения .устройства за счет обеспечения одновременного чтения по

А1 ае (и) 4с» с1/Оо

ГОСУДМРСТОЕННЬЮ HOMHTKT СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТМЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ц,.",,, ц

Ц ф З;ТА»;, (.

Н АВТОВСНОНУ СВНВВТВОВСТВУ

21) 4213881/24-24

° ° °

22) 23 А3.87 (46) 23.10.88. Ввп. Р 39 (72) В.Н.Чуркин, С.З.Куракин .и А.И.Сысоев (53) 681..327(088.8) (5Ь) Авторское свидетельство СССР

Ф 1280453, «л. 0 11 С 11/00, С 11 С 19/00, 1985 °

Авторское свидетельство СССР

Ф 1236551, кл. 0 11 С 11/00, 1984. (54) МНОГОКАНАЛЬНОЕ ОПЕРАТИВНОЕ ЗА- .

ПОМИНАКЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике, в частности к запоминаюа им устройствам, и может быть использовано в многопроцессорных и многомашинных вычислительных системах в качестве общей оперативной памяти.

Целью изобретения является расширение области применения .устройства за счет обеспечения одновременного чтения по .

1432606 произвольному числу несовГ1адающих яд ресов и ювьш,ение быстролейс тяня устройства в режиме чтения. Устройство содержит регистры t -1„ адреса, блок

2 коммутации ацресов, блок 3 анализа адресов, блок 4 сброса обслуженных запросов, дешифраторы 5„-5„ адреса, формирователи 6„-Ь» адресных сигна" лов, накопители 7, -7„, усилители 8„8„ чтения, формирователи 9, -9„ информационных сигналов, коммутатор 10 считанных данных, коммутатор 11 записываемых данных, регистры 12, -12„ слова, адресные входы 13, -13„, информационные выходы 14< -14 », информациИзобретение относится к вычисли" тельной технике, в частности к запоминающим устройствам, и может быть использовано в многопроцессорных и многомашинных вычислительных системах в качестве общей оперативной памяти.

Цель изобретения — расширение области применения устройства пу ем обеспечения одновременного чтения по 1п произвольному числу несовпадающих адресов и повышение быстродействия в режиме чтения.

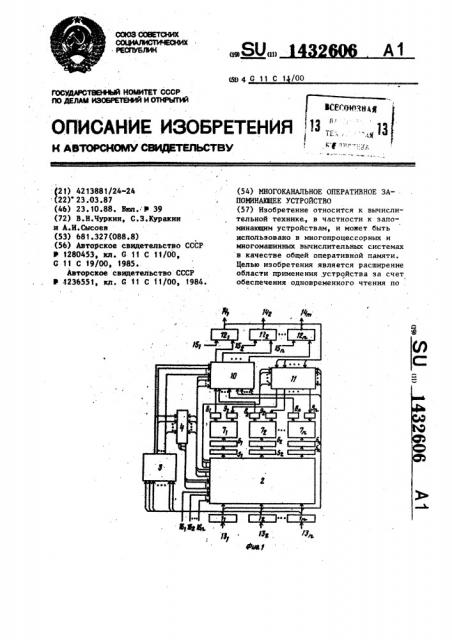

На фиг.1 изображена функциональная схема устройства; на фиг.2-4 функциональные схемы соответственно блока анализа адресов, блока сброса обслуженных запросов и блока коммутации адресов, на фиг.5 и 6 — функциональные схемы соответственно коммутатора 20 записываемых данных и коммутатора считанных данных.

Устройство содержит (фиг.1) регистры 1, -1„ адреса, блок 2 коммутации адресов, блок 3 анализа адресов, блок

4 сброса обслуженных запросов, дешифраторы 5,-5„ адреса, формирователи

6,-6, адресных сигналов, накопители усилители 8 8» чтения AopNH 30 рователи 9 -9„ информационных сигналов, коммутатор 10 считанных данных, коммутатор 11 записываемых данных, регистры 12, -12,„ слова, адресные входы 13, -13„, информационные выходы онные входы 15 -15„16,-16Ä обращения. Устройство работает в режиме записи информационных слов, чтения одновременно по произвольному числу поступающих по и каналам как несовпадающих, так и совпадающих адресов, а также в режиме одновременной обработки обращений для записи и чтения, поступающих по разным п каналам.

Во всех режимах обработки обращений происходит в соответствии с приоритетом: запрос, поступающий по каналу с меньшим номером, имеет больший приоритет при обращении к одному накопителю 7. 3 з.п. ф-лы, 6 ил.

14,-14„, информационные входы 15,—

15„, входы 16, -16„обращения.

Блок 3 анализа адресов (фиг.2) со" держит схемы 171., -17(,(» !) ь 172,1

7 2!.-.1 и 171,, сран ения групп

17„— t7tп-; и элементы И 18,, t8,tq)t "", 18 (» 21 и,18(л- ) групп 18 -18t„,).

Блок 4 сброса обслуженных запросов (фиг.3) содержит элементы ИЛИ 19,-19„ и элементы 20, -20„задержки.

Блок 2 коммутации адресов (фиг.4) содержит триггеры ? 1, -21„, дешифраторы 22 -22 „, гРУппы 23,-23„, элементов И и группы 24„-?4» элементов

И-KIH.

Коммутатор 1 записываемых данных (фиг ° 5) содержит группы элементов

И-ИЛИ 25 -25„.

Коммутатор 10 считанных данных (фиг.Ь) содержит элементы ИЛИ 26„-26„, группы элементов И 27, -27„ и 28,—

28 „, . В целях упрощения функциональной схемы устройства и понимания принципа его работы цепи установки в исходное состояние и синхронизации не показаны.

Устройство работает следующим образом.

Устройство работает в режимах записи и чтения, возможен также случай смешанного режима, когда часть потребителей обращается для записи, а часть — для чтения слов, при этом об1432606 работка обращений происходит в двух режимах одновременно в соответствии с приоритетами потребителей.

Адрес обращения, поступающий по одному или нескольким каналам íà вхо5 ды 13, -13 „(фиг. 1), содержит двухраз— рядный признак режима (т.е ° код операции) чтения или записи, номер канала, совпадающий с номером накопителя 7, -7„, и адрес ячейки памяти в накопителе 7. В регистрах 1 — 1 выдеh ляются два разряда признака режима, причем наличие "1" в одном из разрядов соответствует режиму записи, я наличие "1" в другом — режиму считывания.

Рассмотрим работу устройства в режиме чтения для случая, когда число

n = 4 каналам, причем коды номеров накопителей 7 в первом и втором адресах обращения равны трем и совпадают адреса ячеек памяти (т.е. по двум каналам обращение к накопителю 7э), а коды номеров накопителей в третьем и четвертом адресах обращения равны двум (т.е. обращение к накопителю 7 ) и адреса ячеек памяти в накопителе 7 не совпадают.

Работа устройства начинается с поступления сигналов запроса обращения от потребителей на входы, например, 16< †1 в начале каждого такта обработки. По этим сигналам на входы

13<-13< подаются адреса обращения от четырех потребителей. По этим же сигналам устанавливаются в состояние " 1" триггеры 21<-214 (фиг.4). Обработка запросов происходит в соответствии с их приоритетом: потребит ль с меньшим номером имеет больший приоритет.

С выходов регистров 1<-1< коды номеров накопителей, например, 7 и 7> поступают на входы дешифраторов 22,—

22<, коды адресов обращения (в том числе и оба разряда признака режима обработки) — ня входы блока 3, признаки режима записи (сигналы нулевого уровня) — на входы элементов И-ИЛИ

25<-25 < (фиг.5) и запрещает выдачу слов с реги ров 12,-1?4 через ко у- 50 татор 11.

Единичное состояние триггеров 21<—

214 разрешает дешифрацию кода номера накопителя 7 в дешифраторях 22„-22, на выходе каждого из которых формируется сигнал номера някопителя 7 (сигнал единичного уровня на соответствующем выходе), к которому обращяется соответствующий потребитель ) (в рассматриваемом примере — накопигелей 7 и 7<) .

Сигнал единичного уровня, например, с третьего выхода дешифратора

22< поступает ня второй вход элемента

И-ИЛИ группы 24> и разрешает передачу адреса ячейки памяти, поступающего на первый вход элемента И-ИЛ4

24> с выхода регистра 1,. Сигнал с третьего выхода дешифраторя 22, поступает также на третий вход элемента

ИЛИ 19 блока 4, на первый инверсный вход третьего элемента И групп 23,—

23, с выходов которых сигналы нулевого уровня поступают на входы второго, третьего и четвертого элементов

И-ИЛИ группы 24< и запрещают передачу адресов ячеек памяти, поступающих на входы второго, третьего и четвертого элементов И-ИЛИ группы 24> с выходов регистров 1 -14.

Сигнал единичного уровня с второго выхода дешифраторя ?? поступает ня инверсный вход третьего элемента И группы 23 4 и на прямой вход второго элемента И группы 23, с выхода которого сигнал единичного уровня поступает на вход элемента ИЛИ 19 и на

9 вход третьего элемента И-ИЛИ группы

24 и разрешает передачу адреса ячейки памяти, поступающего на вход третьего элемента И-ИЛИ группы 24„ с выхода регистра 1 . Сигнал нулевого уровня с выхода второго элемента И группы 23 < поступает ня вход четвертого элемента И-ИЛИ группы 24 и запрещает передачу адреса ячейки памяти, поступающего на вход четвертого элемента И-ИЛИ группы 24 с выхода регистра 1 .

В результате адреса ячеек памяти с выходов регис тров 1, и 1 через соответствующие элементы И-Ж1И групп

24 > и 24,, поступают ня входн дешифраторов 5< и 5, с выходов которых расшифрованный адрес поступает ня входы формирователей Ь > и Ь для возбуждения координатных обмоток накопителей 7 и 7, на соответствующих координатных обмотках которых внбряны ячейки памяти, и ня входы усилителей

8 > и 8 поступают слова, считанные по адресам, принятым соответственно на входы 13, и 131.

Сигналы единичного уровня с трегьего выхода дешифряторя 22< и выхода неги<тра 1 (признак режима счптывя32606 6

С выходов элементов ИЛИ 26,-26 считанные слова поступают на входы регистров 12 -12 и далее на выхопы

14,, — 14 устройства. 0 выходов элементов ИЛИ 19 -19 сигнал единичного уровня, эд,ержанные элементами 20 20; задержки на время, необходимое для считывания слова,, устанавливают триггеры 21,,-21> в нулевое состояние.

При этом сбрасываются обработанные обращения (на выходах дешифраторов

22,-22 появляются сигналы нулевого. уровня) и разрешается поступление сигналов обращения от первого„ второго и третьего каналов в следующем такте. Если этих сигналов установки не поступило, то сигнал единичного уровня с второго выхода дешифратора

22 поступает на прямой вход второго элемента И группы 23> с выхода которого сигнал единичного уровня поступает на вход элемента ИЛИ 19, на; вход четвертого элемента И-ИЛИ группы

5 14 ния) поступают соответственно на входы элементов И 27, и разрешают передачу слова, поступающего на вход третьего элемента И 27, с выхода усили..теля 8 > и далее на выход элемента

ИЛИ 26, .

Сигналы единичного уровня с выхода второго элемента И группы 23 и выхода регистра i (признак режима считывания) поступают соответственно на входы элементов И 271 и разрешают передачу слова, поступающего на вход соответствующего элемента И 27з с

abv;opa усилителя 8 и далее на выход элемента ИЛИ 26 .

Для рассматриваемого случая (совпадение адресов обращенич по первому и второму каналам) на выходе схемы

17 (фиг.2) появляется ".;õ;ãíàë единичного уровня, который поступит на вход элемента И 18,> на другой вход которого поступает признак режима считывания ) сигнал единичного уровня) с регистра ) .

Сигнал единичного уровня с выхода элемента И 18,, блока 3, свидетельствующий о совпадении адресов обращения первого и второго каналов в режиме чтения, поступает на вход элемента 20 и на вход элемента И 28< н разрешает передачу слова, поступающего с выхода элемента ИЛИ 26, через элемент И 28, на выход элемента ИЛИ

26я

24 и разрешает передачу адреса ячейки памяти, поступающего на вход четвертого элемента И-ИЛИ группы 24 б с выхода регистр" 1 .

В результате адрес ячейки памяти с выхода элемента И-ИЛИ группы 24 поступает на вход дешифратора 5, с . выходя которого сигналы поступают на вход формирователя 6,2 для возбуждения координатных обмоток накопителя 7, в котором будет выбрана ячейка памяти, и на вход усилителя 8 поступает слово, считанное по адресу, принятому на вход 13

Сигналы с единичного уровня с выхода второго элемента И группы 23> и с выхода регистра 1 .признак режима считывания) поступают соответст20 венно на входы элементов И 27 (фиг.6) и разрешают передачу слова, поступающего на вход соответствующего элемента И 27 с выхода усипителя

8, на выход элемента ИЛИ 26 и далее

2В на вход регистра 124, с выхода которого поступает на выход 14 .

В режиме записи слова, предназначенные для записи, поступают на входы

15„-15„ регистров 12 — 12„, с выходов

@; (orlop epe3 Ко аТар 1 по сигналам признака режима записи (сигналы единичного уровня), поступающим с выв ходов регистров 1<--1„на входы коммутатора 11, и сигналам, поступающим с

35, выходов блока 2 на входы коммутатора поступают ня соответствующие усилители 8„-8 „, с выходов которых — на входы накопителей 7, -7„. В режиме записи блок 3 не работает, так как на его входы с выходов регистров 1„ -f> поступают сигналы нулевого уровня (признаки режима считывания). Признаки режима считывания поступают также на входы коммутатора 10 и запрещают выдачу слов с усилителей 8„-8д. Выбор ячеек памяти в накопителях 7 -7„ для записи слов осуществляется аналогично режиму чтения.

Формула изобретения

f Многоканальное оперативное запоминающее устройство, содержащее первый накопитель, блок коммутации адресов, первый дешифратор адреса, первый формирователь адресных сигналов, первый усилитель чтения, коммутатор считанных данных, коммутатор записываемых данных, первый и второй

7 14 регистры слова, первый формирователь информационных сигналов, первый и второй регистры адреса, информационные входы которых являются соответственно адресными входами первого и второго каналов устройства, информационными выходами первого и второго каналов которого являются соответственно выходы первого и второго регистров слова, причем выходы первого и второго регистров адреса соединены соответственно с адресными входами первой и второй групп блока коммутации адресов, адресные выходы первой группы которого подключены к информационным входам первого дешифратора адреса, выход которого соединен с входом первого формирователя адресных сигналов, выход которого подключен к адресному входу первого накопителя, информационный выход которого соединен с входом первого усилителя чтения, выход которого подключен к первому информационному входу коммутатора считанных данных, первый и второй выходы которого соединены с первыми информационными входами первого и второго регистров слова, выходы которых подключены соответственно к первому и второму информационным входам коммутатора записываемых данных, первый выход которого соединен с информационным входом первого формирователя информационных сигналов, выход которого подключен к информационному входу первого накопителя, вторые информационные входы первого и второго регистров слова являются информационными входами первого и второго каналов устройства, о т л и ч а ю щ е ес я тем, что, с целью расширения области применения устройства путем обеспечения одновременного чтения по произвольному числу несовпадающих адресов и повышения быстродействия в режиме чтения, в него введены блок анализа адресов, блок сброса обслуженных запросов, с второго по и-й (где п 1, число каналов) накопители, с второго по и-й дешифраторы адреса, с второго по и-й формирователи адресных сигналов, с второго по и-й усилители чтения, с второго по и-й формирователи информационных сигналов, с третьего по и-й регистры адреса и с третьего по и-й регистры слова, выходы которых являются информационными выходами с третьего по и-й

32ь06 8

55 каналов устройства, адресными входами с третьего по и-й каналов которого являются информационные входы регистров адреса с третьего по п-й, выходы которых подключены к адресным входам с третьей по и-ю групп блока коммутации адресов, адресные выходы с второй по и-ю групп которого соединены с ин-. формационными входами одноименных дешифраторов адреса, выходы которых подподключены к входам одноименных формирователей адресных сигналов, выходы которых соединены с адресными входами одноименных накопителей с второго по п-й, информационные выходы которых подключены к информационным входам одноименных усилителей чтения, выходы которых соединены с информационными входами с второго по и-й коммутатора считанных данных, выходы с третьего по и-й которого подключены к первым информационным входам одноименных регистров слова, выходы которых соединены с информационными входами с третьего по и-й коммутатора записываемых данных, выходы с второго по п-й которого подключены к информационным входам одноименных формирователей информационных сигналов, выходы которых соединены с информационными входами накопителей с второго по п-й, причем выходы кода режима регистров адреса с первого по и-й подключены к управляюцим входам первой группы коммутатора записываемых данных и управляющим входам первой группы коммутатора считанных данных, управляющие входы второй группы которого соединены с выходами блока анализа адресов и входами признаков совгадения адресов блока сброса обслуженных запросов, выходы которого подключены к входам установки блока коммутации адресов, выходы кода номера накопителя, первой и второй групп которого соединены соответственно с входами установки первой и второй групп блока сброса обслуженных запросов и управляющими входами третьей группы коммутатора считанных сигналов, информационные входы блока анализа адресов подключены к выходам адреса регистров адреса с первого по п-й, управляющие входы второй группы коммутатора записываемых данных соединены с выходами кода номера накопителя третьей группы блока коммутации адресов, входы обращения которого являются входами обраще9 143 ния устройства, информационными входами с третьего по и-й какалов которого являются вторые информационные входы регистров слова с третьего по п--й.

2. Устройство по п.1, о т л и ч a" ю щ е е с я тем, что блок анализа адресов содержит К групп схем сравнеиии (гпе к.:- Г, п-t) и к групп епе" ментов И, причем калдая группа содер жнт и-К схем сравнения и n-K элементов И, при этом первые входы всех схем сравнения К-ой группы и элементов И К-й группы объединены и являются и-и информационным входом блока, выход каждой из схем сравнения К-й группы соединен с вторым входом одно именного элемента И К-й группы, выход котс рого является выходом К-й группы выходов блоха, вторые входы j-й (где

j " "I и-К) схемы сравнения K-й группы соединены с (+К)-и информационным входом блока.

3. Устройство по п.3 о т л и ч аю щ е е с я тем, что блок сброса обслуженных запросов содержит и элементов ИЛИ и и элементов задержки, входы которых соединены с выходами элементов ИЛИ, причем выходы элементов задержки являются выходами блока, входы первого элемента ИЛИ являются входами установки первой группы блока., К-е входы (К+1)-го из элементов ИЛИ с второго по и-й являются входами К-й группы входов признаков совпадения адресов блока, входы с (К+1)-ro no (n+K)-й элементов ИЛИ с второго по

2606

10 и-й являются входами установки второй группы блоха.

4. Устройство по п.I, о т л и ч а5 ю m, е е с я тем, что блок коммутации адресов содержит и триггеров,,и групп элементов И-ИЛИ, и-1 групп элементов И и и дешифраторов, информационные входы которых и первые входы элементов И-ИЛИ групп соответственно ,объединены и являются адресными входами блока, входами обращения которого являются входы установки в "1" триггеров, входы установки в "0" которых являются входами установки блока, причем прямой выход каждого триггера подключен к управлякщему входу одноименного дешифратора, i-й выход

2р (где i 1,п) К-го дешифратора соединен c K-ми инверсными входами -x элементов И групп, -й выход (К+3)-го дешифратора подкжочен к (К+1)-му прямому входу i-го элемента И К-й груп25 пы, i"é выход первого дешифратора соединен с вторым входом первого элемента И-KIN i-й группы и является выходом кода номера накопителя первой группы блока, i-й выход элементов И

Зб К-й группы подключен к второму входу

i-го элемента И-ИЛИ i-й группы и является i-м выходом кода номера накопителя второй группы блока, выходы первого дешифратора и выходы элементов И групп являются. выходами кода номера накопителя третьей группы бло" ка, выходы элементов И-ИЛИ являются адресными выходами блока.

1432606

Фиг.2

От 2

1432606

143260Ь

Ао 22у,2З) -2lf f

12, Редактор В.Петраш

Заказ 5450/4Ь

Производственно-полиграфическое предприятие г. Ужгород, ул. Проектная, 4

Ф !

° М

Составитель Т.Зайцева

Техред Л.Сердюкова Корректор Г.Решетник

Тираж 590 Подписное

BHHHHH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5