Запоминающее устройство с коррекцией ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства памяти повышенной надежности. Цель изобретения - повышение быстродействия и надежности устройства. Устройство содержит блок 1 памяти, блок 2 кодирования , регистр 3 числа, корректор 4 информации, мультиплексор 5, синхронизатор 6, блок 8 управления коррекцией и формирователь 9 сигнала ошибки, В устройстве исключена потеря времени на коррекцию информации при правильном считывании, а также имеется возможность доступа при контроле к дополнительной корректирующей информации. 3 ил. СЛ

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

<19 () 1

Ai д1} 1 G 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ! Icaceeelr4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АBTOPCHOMY СВИДЕТЕЛЬСТВУ @ 4аоуцц (21) 4118.194/24-24 (22) 10.09.86 (46) 23.10.88. Бюл.У 39 (72) В.Н.Ковалев, Л.В.Алексеев, О.В.Росницкий, А.И.Савельев, А.Д.Жучков, Б.Б.Кугутов, В.Н.Степанян и Т.Н.Барановская (53) 681.327 (088.8) (56) Авторское свидетельство СССР

Ф 987679, кл. С 11 С 11/40, 1980.

Авторское свидетельство СССР

Ф 1014042, кл. G 11 С 29/00, 1981. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК (57) Изобретение относится к вычислительной технике и может быть использовано в качестве устройства памяти повышенной надежности. Цель изобретения — повышение быстродействия и надежности устройства. Устройство содержит блок 1 памяти, блок 2 кодирования, регистр 3 числа, корректор

4 информации, мультиплексор 5, синх" ронизатор 6, блок 8 управления коррекцией и формирователь 9 сигнала ошибки ° В устройстве исключена потеря времени на коррекцию информации при правильном считывании, а также имеется воэможность доступа при контроле к дополнительной корректирующей информации. 3 ил.

1432611

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства повышенной надежности.

Дель изобретения — повышение быстродействия и надежности устройства.

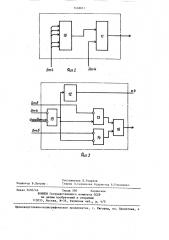

На фиг. 1 изображена структурная схема запоминающего устройства с коррекцией ошибок; на фиг. 2 — структур- 10 ная схема формирователя сигнал-: ошибки; на фиг. 3 — структурная схема блока управления коррекцией.

Устройство содержит (фиг.1) блок

1 памяти, блок 2 кодирования, регистр15

3 числа, корректор 4 информации, мультиплексор 5, синхронизатор б, состоящий из блока 7 задержки и блока

7 согласования, блок 8 управления коррекцией и формирователь 9 сигна- 20 .ла ошибки.

Формирователь 9 содержит {фиг.2) элементы И-НЕ 10 и i!.

Блок 8 управления коррекцией содержит (фиг.3) элемент НЕ 12, эле- 25 менты И 13 и 14, элемент И-НЕ 15 и элемент ИЛИ-НЕ 16.

Устройство работает следующим образом.

В режиме записи на адресные ахо- 30 ды блока 1 поступает адрес ячейки памяти, по которому производится запись кода числа, поступающего на информационные входы блока 1 и на входы блока 2 ° Блок 2 вырабатывает дополнительные, в соответствии с выбранным кодом коррекции, разряды числа (корректирующий код) и подает их на контрольные входы блока 1. На вход выборки блока 1 поступает управ- 40 ляющий сигнал с выхода блока 6Ä

В режиме считывания считанный из блока 1 код числа и корректирующий код заносятся в регистр 3. С регистра 3 код числа поступает на входы корректора 4. В результате анализа поступившей из регистра 3 информации корректор 4 может откорректировать информацию о наличии ошибки..При отсутствии ошибки коррекция информации заблокирована и информация формируется на выходах корректора 4 независимо от анализа возможного отказа, причем раньше, чем в случае 55 наличия ошибки.

С выходов корректора 4 информация падается на входы мультиплексора 5, на другие входы которого поступает корректирующий код с выходов регистра 3.

Вместе с установившейся на выходе мультиплексора 5 выходной информацией на выход Готовность информации устройства должен быть подан сигнал сопровождения, время поступления ко торого определяет время выборки устройства, т.е. быстродействие. Этот сигнал сопровождения при наличии коррекции и при ее отсутствии вырабатывается в разное время, т.е, при отсутствии ошибки в устройстве сигнал сопровождения вырабатывается раньше, чем при необходимости коррекции.

В случае отсутствия ошибки в считанной информации на вход элемента

И-HE 15 блока 8 поступает управляющий потенциал с выхода корректора 4.

На другой вход элемента. И-НЕ 15 при работе в режиме ксррекции с управляющего входа устройства поступает управляющий потенциал на коррекцию.

В результате на элемент НЕ 12 поступает высокий потенциал, который блокирует коррекцию информации, подавая на вход корректора 4 низкий потенциал. В этом случае приходит разрешающий потенциал на вход первого элемента И 13, на другой вход которого приходит сигнал с синхронизатора 6.

Сигнал с выхода элемента И 13 поступает на вход элемента ИЛИ-НЕ 16 н далее на выход устройства. Этот сигнал служит сигналом сопровождения считанной информации.

При наличии ошибки, т.е. при необходимости коррекции, управляющий потенциал с выхода корректора 4 поступает на элемент И-HK 15. 3а счет этого сигнал сопровождения от синхронизатора 6 проходит на выход устройства через элемент И 14 и элемент

ИЛИ-НЕ 16 с некоторой задержкой, которая наперед задана и определяет ся необходимым временем на коррекцию.

С целью сохранения способности обнаружения двойных ошибок формирование признака неисправности s устройстве организовано следующим образом.

На входы элемента И-НЕ 10 с выходов корректора 4 подается синдром коррекции в обратном коде. При отсутствии ошибки в считанной информации с выхода элемента И-НЕ 10 на вход элемента И-НЕ 11 поступает запрещающий, а при наличии одиночной или двойной ошибки — разрешающий потенциал. Если

14326 при этом на вход второго элемента

И-НЕ 11 с выхода корректора 4 поступает сигнал, с выхода элемента И-НЕ

11 на выход устройства выдается сигнал Наличие ошибки — признак не11 13 .5 исправности.

Для обеспечения диагностики и повышения надежности в устройстве обеспечивается доступ к дополнительной 1О корректирующей информации, хранимой в блоке 1, без использования дополнительных выходных связей. Для этого с управляющего входа устройства поступает сигнал блокировки выдачи 15 информации на мультиплексор 5,. по которому блокируется выдача основной информации из мультиплексора 5 и разрешается выдача корректирующего кода, поступающего на входы мультиплексора

5 с выходов регистра 3. формула изобретения

Запоминающее устройство с коррек- 25 цией ошибок, содержащее блок памяти, блок кодирования, регистр числа, корректор информации, причем информационные входы блока памяти и.входы блока кодирования объединены поразрядно и являются, информационными входами устройства, выходы блока кодирования подключены к контрольным входам блока памяти, адресные входы и вход записи-чтения блока памяти являются

35 соответственно адресными входами и входом задания режима работы устройства, информационные и контрольные выходы блока памяти подключены соответственно к входам информационных и контрольных разрядов регистра числа, выходы информационных и контрольных разрядов которого соединены соответственно с информационными и

11

4 контрольными входами корректора информации, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и надежности устройства, в него введены синхронизатор, мультиплексор, блок управления коррекцией и формирователь сигнала ошибки, выход которого является выходом наличия ошибки устройства, причем информационные входы первой и второй групч мультиплексора подключены соответственно к выходам контрольных разрядов регистра числа и к информационным выходам корректора информации, управляющий вход и выходы мультиплексора являются соответственно входом разрешения считывания и информационными выходами устройства, вход синхронизатора является входом обращения устройства, с первого по четвертый выходы синхронизатора подключены соответственно к входу выборки блока памяти, к входу приема регистра числа, к первому и второму управляющим входам блока управления коррекцией, вход "Разрешение коррекции" блока управления коррекцией является соответствующим входом устройства, вход

"Блокировка коррекции" блока управления коррекцией и вход формирователя сигнала ошибки соединены с выходом "Отсутствие ошибки" корректора информации, контрольные выходы корректора соединены с входами группь. формирователя сигнала ошибки, вход синхронизации корректора информации является тактовым входом устройства, первый вход блока управления коррекцией соединен с входом

"Блокировка коррекции" корректора информации, второй выход блока управления коррекцией является выходом

"Готовность информации" устройства.

1432611

Составитель Б.Рудаков

Техред Л.Сердюкова Корректор В,Романенко

Редактор В.ПетрашЗаказ 5450/46 Тираж 590 Подписное

ВБИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, ужгород, ул. Проектная, 4