Устройство для контроля полупроводниковой памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть применено для контроля блоков полупроводниковой памяти. Целью изобретения является повышение надежности устройства . Устройство содержит синхронизаV::

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

2612 А 2 (19) (11) (.51) 4 G 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ВСЕЖН ЗЮМ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ЮлнотеИ

Ю.В.АноСССР

1982

Г 1

1Ф

Фиг.1 (61) 1051585 (21) 4170338/24-24 (22) 30. 1 2. 86 (46) 23. 10. 88. Вюл. N- 39 (72) В.И.Лешукович, А.Д.Шац, хин и Ю.М.Дробышевский (53, 681.327 (088.8) (56) Авторское свидетельство

У 1051585, кл. G 11 С 29/00 (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОЛУПРОводниковой пАмяти (57) Изобретение относится к вычислительной технике и может быть применено для контроля блоков полупроводниковой памяти. Целью изобретения является повышение надежности устройства. Устройство содержит синхрониза1432612 тор 1, блок 2 управления, блок 3 задания тестов, первый 4 и второй 6 счетчики адреса, коммутаторы 5, 10, 11, 13, 20, формирователь 7 тестовых сигналов, блок 8 сопряжения уровней напряжения, регистр 9 адреса ошибки, первый блок 12 сравнения, группу триггеров, блок свертки по модулю два, триггер, блок памяти эталонных сигнатур, сигнатурный анализатор, вто" рой блок сравнения и элемент И. Надежность устройства повышается за счеч введения самоконтроля устройства. В режиме. самоконтроля блокируется обращение к контролируемой памяти, а тестовые,цанные, адреса и код команды подаются на вход блока свертки по модулю два, где свертываются по

Изобретение относится к вычислительной технике, может быть применено для кочтроля блоков полу роводниковой памяти, и является усовершенст- 5 вованием устройства по авт.св.

Ф 1051585.

Цель изобретения — повьппение надежности устройства.

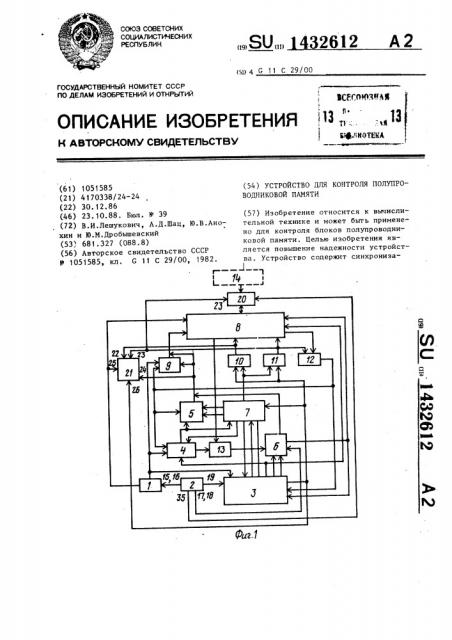

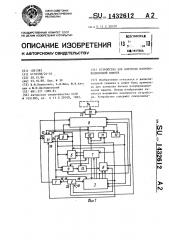

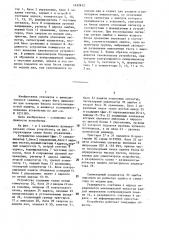

На фиг. 1 и 2 изображена функциональная схема устройства; на фиг. 3структурная схема блока управления.

Устройство содержит (фиг.1) синхронизатор 1,блок 2 управления, блок 3 задания тестов, первый счетчик 4 адреса пер15 вый коммутатор 5, второй счетчик 6 адреса, формирователь 7 тестовых сигналов, блок 8 сопряжения уровней напряжения, регистр 9 адреса ошибки, второй коммутатор 10, третий коммутатор 1 1 первый блок 12 сравнения, четвертый коммутатор 13. Блок контролируемой памяти обозначен позицией 14, Блок 2 управления, имеет с первого по пятый выходы 15-19.

Устройство содержи г также пятый коммутатор 20, блок 21 с входом 22 кора команды, входами 23 контрольного слова, входами 24 адреса„ входами 25 синхронизации и установочными входами 26, содержащий группу триггеров, 27.с выходами 28, блок 29 свертки по модулю два, элемент И 30, триггер 31„ модулю два и служат для анализа в сигнатурном анализаторе, по окончании теста сигнатура с выходов которого сравнивается с эталонной, считанной из блока памяти эталонных сигнатур в соответствии с формируемым в устройстве тестом. При несовпадении сигнатур сигнал ошибки с выхода второго блока сравнения переводит в состояние, соответствующее ошибке, один из триггеров группы, выбранный сигналами разрешения выполнения теста с выходов блока 3. Таким образом осуществляется самоконтроль устройства, при котором контролируются синхронизатор

1, блок 3, счетчики 4, 6, формирователь 7 и коммутаторы 5, 10, 11 и 13.

3 ил. блок 32 памяти эталонных сигнатур, сигнатурный анализатор 33 ошибок и второй блок 34 сравнения. Блок 2 управления имеет также шестой выход 35 и содержит (фиг.3) переключатеяи 36-4 1, выводы 15-19 и 35 подвижных контактов которых являются выходами с первого по шестой блока 2 управления, на вход

42 которого подается уровень нулевого потенциала, а на вход 43 — уровень логической единицы.

Триггеры 27 и 31 являются Р-триггерами ИС серии К155ТМ2. Блок 32 памяти эталонных сигнатур выполнен иэ микросхем ПЗУ К 155 РЕ3, причем число используемых ячеек памяти блока 32 определяется числом тестов, используемых для самоконтроля устройства, а разрядность слова — разрядностью регистра сдвига сигнатурного анализатора 33.

Сигнатурный анализатор 33 ошибок выполнен из регистра сдвига и сумматора по модулю два.

Разрядность счетчика 4 адреса определяется максимальной емкостью каждой микросхемы контролируемой памяти 14, а разрядность счетчика 6 ад-. реса — ее информационной емкостью.

Устройство работает следующим образом.

1432612

При включении питания устанавливаются в исходное нулевое состояние счетчики 4 и 6, блок 3.,(фиг.1), формирователь 7, блок 12, сигнатурный анализатор 33, триггеры 27. По выходу 15 блока 2 устанавливается частота обращения к проверяемому блоку 14 памяти, по выходам 17 и 18 — объем проверяемой памяти, по выходам 19 — 10 режим контроля, по выходу 35 — режим работы: контроль памяти 14 или самоконтроль устройства.

По сигналу пуска с выхода 16 блока

2 включается синхронизатор 1, с выхо- 15 да которого поступает на вход счетчика 4 счетный сигнал с периодом, равным циклу обращения. Адрес контролируемой памяти .14 формируется счетчиками 4 и 6. Счетчик 4 изменяет свое 20 состояние по счетному сигналу, поступающему с выхода синхронизатора 1, вырабатывая при этом сигналы переноса, соответствующие емкости применяемых в памяти 14 микросхем памяти. 25

Управление счетчиком 6 осуществляется через коммутатор 13, на информационные входы которого поступают сигналы переносов с выхода счетчика 4, а на управляющий вход — сигналы с выхо- 30 да блока 8, которые разрешают передачу сигнала переноса на выход коммутатора 13.

По выходам 17 и 18 блока 2 задается объем памяти 14 путем блокировки части разрядов счетчика 6. При исключении иэ счетного режима всех разрядов счетчика б обращение осуществляется к одной микросхеме памяти, определяемой состоянием выходов 17 и 18 бло-40 ка 2. По подключенным к выходам блока 3 входам счетчика 6 задается режим его работы в зависимости от формируемого теста. По заполнении счетчика 6 вырабатывается сигнал переноса, кото.рый, поступая в блок 3, участвует в формировании сигнала окончания контроля .

По выходу 19 блока 2 задается необходимый набор тестов для контроля памяти 14. Сигнал с выхода блока 3, поступая на вход формирователя 7 и управляющие входы коммутаторов 10и

11, разрешает формирование тестовьм последовательностей выбранного теста.

По сигналу окончания теста, поступаю- 55 щему с выхода формирователя 7, блок 3 разрешает формирование следующего выбранного теста. Сигнал с выхода блока 3, поступающий на входы блока 8 и счетчика 4, блокирует прохождение счетного сигнала на вход счетчика 4 и обращение к памяти 14 на входе блока 8 на время поиска очередного выбранного теста. По сигналу окончания теста блок 3 разрешает запись в память 14 фоновой информации. Сигнал переноса на входе блока 3 переводит последний в состояние, соответствую-, щее разрешению выполнения собственно тестовой программы.

На входы коммутатора 5 поступают управляющие сигналы с выходов формирователя 7, причем в зависимости от выполняемого теста на выход коммутатора 5 проходит прямой или инверсный код адреса, поступающий на информационные входы коммутатора 5 с выхода счетчика 4, либо фоновый или тестовый адрес, поступающий с выхода формирователя 7. В зависимости от алгоритма выполняемого теста с выхода фор" мирователя 7 поступает сигнал, блокирующий счетный сигнал в счетчике.

На информационные входы коммутаторов 10 и 11 поступает с выхода формирователя 7 код операции и контрольное информационное слово. Сигналы с выходов коммутаторов 10 и 11 через блок 8 и коммутатор 20 поступают на проверяемую память 14. В блоке 12 выполняется сравнение считанной иэ памяти 14 информации с контрольной.

Регистр 9 содержит адрес, сформированный в предыдущем обращении к памяти. При отсутствии ошибки выход регистра 9 блокирован и в память 14 поступает адрес с выхода коммутатора 5.

Параллельно с обращением по следующему адресу в блоке 12 осуществляется оценка информации, считанной по предыдущему адресу. При несовпадении информации блок 12 вырабатывает сигнал ошибки, который блокирует счетный сигнал счетчика 4, формирование следующего теста в блоке 3 и выходы коммутатора 5, а регистр 9 переводит в рабочее состояние. Происходит останов по адресу с ошибкой. На блоке сигнализации (не показан} высвечивается адрес ошибки, информационное слово, режим проверки.

В режиме самоконтроля сигнал с выхода 35 блока 2, поступая на вход коммутатора 20, запрещает обмен информацией между блоком 8 и проверяемой памятью 14 и разрешает прохождение сиг1432612 налов входа 23 коммутатора 20 на вход блока 8. По сигналу пуска устройство вырабатывает адреса, информационные . слова и команды, которые подвются на входы 24, 23, 22 соответственно, а, контрольное слово через вход 23 коммутатора 20 - на блок 8. Информация с входов 22, 23, 24 свертывается в блоке 29 (фиг .2}, подается на вход триггера 31, а с его выхода — на вход анализатора 33.

Сигналы, вырабатываемые синхронизатором 1, поступают на входы 25, собираются на элементе И 30 и подаются на вход триггера 31. В анализаторе

33 сигналы с выходов разрядов обратной связи сднигового регистра суммируются по модулю два с двоичной последовательностью сигналов, поступаю.щей с выхода триггера 31. Результат суммирования по модулю два поступает на сдвигоный вход регистра сднига, и по синхроимпульсу в каждом такте обращения к проверяемой памяти происходит занесение результата суммирования и одновременно сдвиг информации по разрядам в регистре сдвига. Такие операции продолжаются в течение выполнения теста, после чего прекращается поступление синхроимпульсон н входной последовательности и осуществляется анализ кода, остающегося н регистре сдвига. Этот код представляет собой определенным образом преобразованную и сжатую двоичную информацию и называется сигнатурой.

Анализатор 33 позволяет выявить динамические ошибки, которые не способны обнаружить другие методы локализации неисправностей. Используемый метод позволяет с достоверностью

99,998Х выявлять ошибочную двоичную последовательность независимо от ее длины или сложности ошибок.

Сигналы разрешения формирования тестов с выхода блока 3,. поступая на входы 26, выбирают из памяти блока 32 сигнатуру, соответствующую формируемому тесту, и разрешают работу одного из триггеров 27. Выбранная сигнатура сравнивается в блоке 34 с. полученной на выходе анализатора 33 по окончании формирования теста. В случае их несовпадения сигнал ошибки с выхода блока 34 поступает на входы триггеров

27 и переводит один из них, выбранный сигналами с входов 26, н состояние, соответствующее ошибке.

Таким образом контролируется правильность работы синхронизатора 1, блока 3, счетчиков 4 и 6, формирователя 7, коммутаторов 5, 10, 11 и 13, за счет чего повышается надежность устройства. о

Формула изобретения

1Î i

Устройство для контроля полупроводниковой памяти по авт.сн.

Ф 1051585, о т л и ч a N щ е е с я. тем, что, с целью повышения надежнос« ти устройства, в него введены пятый коммутатор, блок свертки по модулю два, триггер, блок памяти эталонных сигнатур, группа триггеров, второй. блок сравнения, сигиатурный анализатор

20 и элемент И., выход которого соединен с входом синхронизации триггера, информационный вход и выход которого подключены соответственно к выходу. блока свертки по модулю дна и к так25 тоному входу сигнатурного анализатора,ньжоды которого "îåäèíåíû с информационными входами перной группы второго блока сравнения, информационные входы второй группы и выходы котороЗО го подключены соответственно к выходам блока памяти эталонных сигнатур и к

0-входам триггерон группы, входы устанонки которых и адресные входы блока памяти эталонных сигнатур соедине35 ны с четвертым выходом блока задания тестов, причем входы контрольного слова блока свертки по модулю два подключены к выходам третьего коммутатора и информационным входам первой

4 группы пятого коммутатора, информационные входы второй группы и выходы первой группы которого соединены с информационными выходами и информационными входами блока сопряжения уровней напряжения, управляющий вход пятого коммутатора подключен к шестому выходу блока управления, входы элемента

И соединены с выходами группы синхронизатора, первый и второй информациснные входы блока свертки по модулюдва подключены соответственно к выходу второго коммутатора и к выходам второго счетчика адреса, выходы триггеров группы являются индикаторными выходами устройства, информационные входы третьей группы и выходы второй группы пятого коммутатора являются контрольными входами и контрольными выходами устройстна.

1432612

Подписное

Тираж 590

ВПИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятием г, Ужгород, ул. Проектная, 4

Редактор В.Петраш

Заказ 5450/46

92 (Риг. 3

Составитель Т.Зайцева

Техред Л.Сердюкова КорректорА Обручар