Формирователь прямоугольных импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и предназначено для использования в контрольно-измерительном оборудовании, в частности в системах контроля интегральных схем. Цель изобретения - повьшение быстродействия посредством уменьшения времени включения режима Третье состояние. Логический сигнал тестовой последовательности поступает на клемму 5 блока 1 управления, посредством которого управляет работой блока 2 формирования амплитуды. Сформированный сигнал с заданными значениями верхнего и нижнего уровней через повторитель 3 напряжения поступает на выходную клемму 7 устройства. Введение в формирователь пря моугольных импульсов повторителя 3 напряжения и блока 4 задания режимов позволяет подавать с клеммы 6 сигнал блокировки через блок 1 управления на транзисторы дифференциального каскада и тем самым с высокой скоростью переключать рабочий ток повторителя 3 напряжения, что обеспечивает малое время включения pe raiMa Третье состояние. В формирователе использованы элементы ИЛИ 8 и 9, транзисторы 10-18, резисторы 19-21, источники 24 . и 25 опорных напряжений, клеммы 22, 23 и 26. 2 з.п. ф-лы, 2 ил. S СЛ

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (58 4 Н 03 К 5/01

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ч

ОПИСАНИЕ ИЗОБРЕТЕНИЯ @

H А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4209583/24-21 (22) 16. 03. 87 (46) 23. 10.88. Бюл. ¹- 39 (72) А.И.Панов и А.И.Лепехин (53) 621.373 (088.8) (56) Авторское свидетельство СССР № 1221721, кл. Н 03 .К 5/01, 1984.

Эйдукас Д.IO., Орлов Б.В., Попель Л.М. и др. Измерение параметров цифровых интегральных микросхем.

М.: Радио и связь, 1982, с.267, рис.6.21. (54) ФОРМИРОВАТЕЛЬ ПРЯМОУГОЛЬНЫХ ИМПУЛЬСОВ (57) Изобретение относится к импульсной технике и предназначено для использования в контрольно-измерительном оборудовании, в частности в системах контроля интегральных схем. Цель изобретения — повышение быстродейст— вия посредством уменьшения времени включения режима "Третье состояние".

„„Я0„„1432748 А 1

Логический сигнал тестовой последовательности поступает на клемму 5 блока 1 управления, посредством которого управляет работой блока 2 формирования амплитуды. Сформированный сигнал с заданными значениями верхнего и нижнего уровней через повторитель 3 напряжения поступает на выходную клемму 7 устройства. Введение в формироI ватель прямоугольных импульсов повторителя 3 напряжения и блока 4 задания режимов позволяет подавать с клеммы 6 сигнал блокировки через блок 1 управ— ления на транзисторы дифференциальногO K K H TeM Mb c B i K H CKO ростью переключать рабочий ток повторителя 3 напряжения, что обеспечивает малое время включения режима "Третье состояние". В формирователе использованы элементы ИЛИ 8 и 9, транзисторы

10-18, резисторы 19-21, источники 24 и 25 опорных напряжений, клеммы 22, 23 и 26. 2 з.п. ф- лы, 2 ил.

1432748

Изобретение относится к импульсной технике и предназначено для использо.вания в контрольно-измерительном оборудовании, в частности в системах кон«5 троля интегральных схем (ИС) различной степени интеграции, и: ожет быть применено в качестве драйвера-задатчика напряжений (входных воздействий) на выводы контролируемых схем. 10

Цель изобретения — повышение быстродействия посредством уменьшения времени включения режима "Третье состояние".

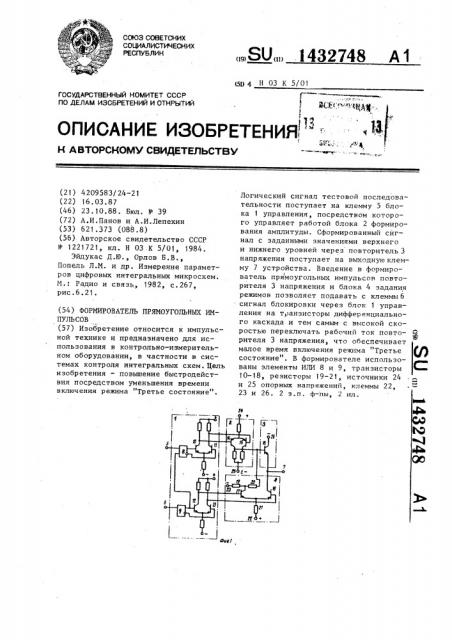

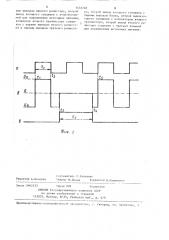

На фиг. изображена электрическая 15 схема формирователя прямоугольных им,пульсов, на фиг. 2 — временные диаг раммы его работы.

Формирователь прямоугольных импуль,,сов содержит блок 1 управления, блок 20 .,2 формирования амплитуды, повторитель ! 3 напряжения, блок 4 задания режимов

1 две входные 5 и 6 и выходную 7 шины.

Блок 1 управления состоит из двух элементов ИЛИ 8 и 9 и двух дифферен- 25 циальных усилителей на транзисторах

10 и 11 и !2 и 13 соответственно.

Блок 2 формирования амплитуды прец-. ставляет собой дифференциальный уси литель на транзисторах 14 и 15, пов- 30

:торитель 3 напряжения — эмиттерный пов торитель на транзисторе 16,а блок 4 задания р ежимов — диффер енциал ьный усилитель на транзисторах 17 и 18 с ре зисторами 19-21 и клеммами 22 и 23.

Формирователь прямоугольных импульсов содержит также разнополярные источники 24 и 25 опорных напряжений, а повторитель 3 напряжения — клемму

26. Первый вход элемента ИЛИ 8, яв40 ляющийся первым входом блока 1 управления, соединен с входной шиной 5, второй вход — с прямым выходом элемента ИЛИ 9, вход которого„ являющийся вторым входом блока 1 управления, 45 подключен к входной шине 6. Прямые выходы элементов ИЛИ 8 и 9 раздельно соединены с базами транзисторов 10и .12 соответственно, а инверсные выходы — с базами транзисторов 11 и 13.

Коллекторы транзисторов 10 и 11, 50 образующие первый и второй выходы блока 1 управления, раздельно соединены с базами транзисторов 14 и 15, образующими первый и второй входы блока

2 формирования амплитуды.

Коллекторы транзисторов 12 и 13, образующие третий и четвертый выходы блока управления,,раздельно слединевы с базами транзисторов 17 и 18 соответственно, образующими первый и второй входы блока 4 задания режима.

Коллектор транзистора 17 через резистор 20, один вывод которого образует первый выход блока 4 задания режима, соединен с коллектором транзистора 14, являющимся выходом блока 2 формирования амплитуды, и с базой транзистора 16, являющейся входом повторителя 3 напряжения, а через резистор 19 — с клеммой ? 3.

Коллектор транзистора 18, образующий второй выход блока 4 задания режимов, соединен с эмиттером транзистора 16, являюшимся выходом повторителя 3 напряжения, и выходной шиной

7. Эмиттеры транзисторов 17 и 18 через резистор 2! соединены с клеммой

22. Источник 24 опорного напряжения положительной полярности чере" резистор соединен с эмиттерами транзисторов 14 и 15 блока 2 формирования амf

:плитуды, а источник 25 опорного напряженив — с коллекторами этих же тран1 зисторов (через соответствующие резисторы) .

Формирователь прямоугольных импульсов работает следующим образом.

Пусть необходимо сформировать на выходной шине 7 импульсы, длительность которых равна длительности входных импульсов, поступающих на входную шину 5, причем в процессе формирования заданных импульсов необходимо реализовать возможность переключения формирователя в режим "Третье состояние" по приходу на входную шину 6 управляющего сигнала.

В момент времени t„ на первый вход элемента ИЛИ 8 блока 1 управления с входной шины 5 поступает сигнал уровня "1" (фиг.2а). С прямого и инверсного выходов элемента ИЛИ 8 сигналы

"!" и "0" соответственно поступают на базы транзисторов 10 и 11. При этом транзистор 10 открывается, обеспечивая открывание транзистора 14 блока 2 формирования амплитуды и формирование переднего фронта выходного импульса (фиг.2б). В течение длительности 7, на базу транзистора 16 повторителя 3 напряжения через открытый транзистор

14 поступает высокий уровень напряжения, определяемый протекающим током, задаваемым источником 24 опорного напряжения. При этом, поскол ку на входной шине 6 установпен "0", травзисто-. описано выше с момента времеви

Таким образом, происходит формирс вание прямоуг !PIE..ных импульсов на выходе устроиства с переключением его в режим Третье cc ñòoÿíèå на время действия управляющего импульса, поступающего на входную шину б.

Ф о р м ул а и з о б р е т е н и я

Формирователь прямоугольных импульсов, содержащий блок управления, блок формирования амплитуды, источник положительного опорного напряжения, источник отрицательного опорного на— пряжения, первую и вторую входные шины, выходную шину, первая и вторая входные шины соединены соответственно с первым и вторым входами блока управления, первый и второй выходы которого соединены соответственно с первым и нторым входами блока формирования амплитуды, третий и четвертый входы кото— рого соединены соответственно с источниками положительного и отрицательного опорных напряжений, о т л и ч аю шийся тем, что, с целью понышения быс7родействия за счет уменьшения времени включения режима "Третье состояние", в него ннедены повторитель напряжения и блок задания режимов, причем первый и второй входы блока задания режимов соединены соответственно с третьим и четвертым выходами блока управления, первый выход блока задания режимов соединен с входом.повторителя напряжения и выходом блока формирования амплитуды, а второй выход соединен с выходом повторителя напряжения и выходной шиной.

2. Формирователь по п.1, о т л и ч а ю шийся тем, что повторитель напряжения содержит транзистор, клемму для подключения источника питания, входом повторителя напряжения, эмиттер соединен с выходом повторителя напряжения, а коллектор соединен с клеммой для подключения источника питания.

3.. Формирователь по п.1, о т л и ч а ю шийся тем, что блок задания режимов содержит первый и второй транзисторы, первый, второй и третий резисторы, первую и вторую клеммы для подключения источников питания, причем первый и второй входы блока сое— динены с базами соотнетственно первого и второго транзисторов, эмиттеры которых соединены между собой и слер3 1432748 4 ры 13 и 18 открыты, * результате чего работа транзистора 16 осуществляется в линейном режиме за счет задания через него тока транзистором 18 бло5 ка 4 задания режима. Высокий уровень напряжения проходит на выходную шину

7, формируя требуемый высокий уровень выходного импульса (фиг. 2б) .

В момент времени t на входную. шину 5 поступает сигнал "0",.приводя.— щий к закрыванию транзисторов 10и 14, в результате чего напряжение с источника 25 опорного напряжения поступает на базу транзистора 16 повторителя 3 напряжения, и на выходной шине 7 форМируется низкий уровень напряжения выходного импульса (фиг.2б,момент времени t < ) . переключение формирователя н режим 20 нТретье состояние" осуществляется в. момент времени t EEo приходу на нходз ную шину 6 управляющего импульса длительностью i< (фиг.2в, момент време-. ни t ). Сигнал "1." .с шины 6 поступает25 на вход элемента ИЛИ 9, с прямого выхода которого сигнал "1" проходит на второй вход элемента ИЛИ 8,.в резуль-. тате чего на инверсном выходе.элемента HJIH 8 устанавливается сигнал "0",. обеспечивая закрывание транзисторов и 15. При этом. транзисторы 10 и 14

1открываются. Сигналы "1", "0"; с прямо.%

ro и инверсного выходов элемента ИЛИ 9: поступают на базы транзисторов 12 и .

13 соответственно, в результате чего транзистор 12 открывается, обеспечивая открывание транзистора 17 блока 4 задания режима, а транзистор 13 закрывается, обеспечивая закрывание транзистора 18. Открытый транзистор

17 обеспечивает протекание дополнительного тока через токоограничивающий резистор 20, включенный в коллекторные цепи транзисторов 14 и 17, в 4 . причем база транзистора соединена с результате чего на базе транзистора

16 формируется напряжение вольтодобавки, являющееся дополнительным запирающим напряжением для этого транзистора.

Таким образом, до момента времени

t, т.е. на время длительности управляющего импульса, транзисторы

16 и 18 закрыты, их токи утечки минимальны, а выходное сопротивление максимально, чем обеспечивается режим "Третье состояние".

С момента времени t процесс формирования импульсов повторяется, как

748

Составитель С, Радзеви

Т ехр ед Г1. Дидык Корректор В,Романенко

Редактор А.Козориз

Заказ 5462/53

Тираж 929

Подписное

ВНИИЛИ Государственного комитета СССР по делам изобретений и открытий

)i3Î35, Г1осква,, )К-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятия, г. Ужгород, уп, Проектна .„ 4

5 1432 вым выводом первого резистора, второй вывод которого соединен с второй клеммой для подключения источника питания, коллектор второго транзистора соеди5 нен с первым выводом второго резистопа и первым выводом третьего резисто— ра, второй вывод которого соединен с первым выходом блока, второй выход которого соединен с коллектором второго транзистора., второй вывод RToDQI pp— зистора соединен с третьей клеммой для подключения источника питания .