Декодирующее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи цифровых данных позволяет повысить точность декодирования. Декодирующее устройство содерткит селектор 1 импульсов, блок 2 регулируемой задержки и регистр 4 сдвига. Благодаря введению триггера 3, регистров 4-7 сдвига, элементов ИЛИ 8-10 и элементов ИЛИ-НЕ 11-14 в устройстве обеспечивается обнаружение всех нарушений алгоритма кодирования передаваемого кода, 2 шт. W S Фиг.1

СОЮЗ СОВЕТСНИХ

СОЫИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (!9) (11) А1 (с11 i1 Н 03 И 5/1 2, 1 3/00

Ц

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСИОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (2!) 4150907/24-24 (22) 24,11.86 (46) 23.10.88, Вюл. Ó 39 (72) А.А.Каяцкас, В.В,Кацман и А.А.Зенкус (53) 681.325 (088 ° 8) (56) Техника средств связи. Сер.

Радиоизмерительная техника, 1983, 11 4, с. 114 12!

Авторское свидетельство СССР

У 1290532, кл. Н 03 М 5/12, 1984. (54) ОЕКОЛИРУ!ОЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и технике связи.

Его использование в системах передачи цифровых данных позволяет ловысить точность декодирования. Декодирующее устройство содержит селектор

1 импульсов, блок 2 регулируемой задержки и регистр 4 сдвига. Благодаря введению триггера 3, регистров

4-7 сдвига, элементов ИЛИ 8-10 и элементов ИЛИ-НЕ 11-14 в устройстве обеспечивается обнаружение всех нарушений алгоритма кодирования передаваемого кода, 2 ил.

1432781

Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах передачи цифровых данных.

Цель изобретения — повышение точности декодирования.

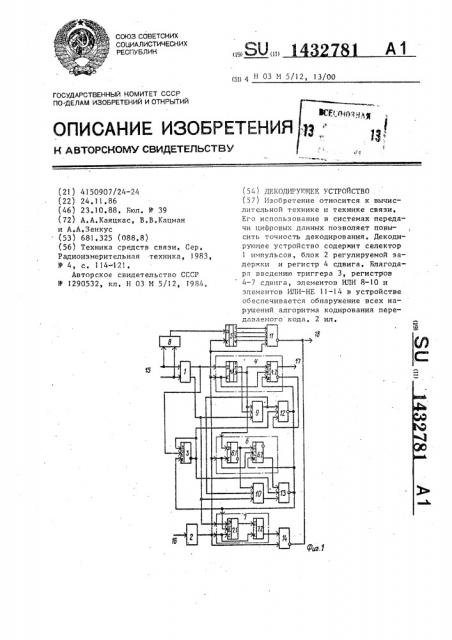

На фиг.l приведена функциональная схема декодирующего устройства; на фиг. 2 — временные диаграммы его ра- 10 ,боты.

Декодирующее устройство содержит !, селектор 1 импульсов, блок 2 регули, руемой задержки, триггер 3, первый,четвертый регистры 4-7 сдвига, пер- !5 вый — третий элементы ИЛИ 8-10 и пер. вый — четвертый элементы ИЛИ-HF 11-14, На фиг.l обозначены информационные входы 15, тактовый вход 16, информационный 17 н контрольный 18 выходы, 20

Селектор l импульсов и блок регулируемой задержки выполнены так же, как и прототипе.

Первый регистр 4 включает в себя трехразрядный регистр 4.1 и триг 2 гер 4.2.

Третий и четвертый регистры 6 и 7 содержат по два триггера (6.1, 6.2 и .7.1, 7.2)..

Прямой выход триггера 4.2 являет- 30 ся первым выходом регистра 4, выходы второго и третьего разрядов регистра

4.1 являются соответственно вторым ,и третьим выходами регистра 4, инверс-, ный выход триггера 4,2 — четвертый выход регистра 4.

Выходы триггеров 6,1 и 6.2 являются соответственно первым и вторым вы.ходами регистра 6.

Алгоритм образования HDB-З кода состоит в том, что последовательность из четырех нулей подряд (О О О О) заменяется на последовательность

О О 0 V или B 0 О Ч таким образом, чтобы между двумя V-вставками было нечетное число импульсов В или В и

В, Допустим, что кодовая последовательность проходит следующие состояния по тактовым интервалам:

1 0 0 Î 0 0 1 О О О 0 О

1 О О 0 0 О . ° .ф

После кодирования в линию переда ется последовательность биполярных импульсов:

+ - О 0 - О + 0 О 0 + 0 - О 0 0

+ О О вее в

ВВООЧОВОООЧ

OB0O0V BO0V . Ошибочным будем считать каждый импульс, не соответствующий алгоритму кодирования.

Декодирующее устройство функционирует следующим образом.

Допустим, что исходная информация (фиг.2a), закодированная в коде

НРВ-3 (фиг.2б), формируется с ошибками -на входах селектора 1 импульсов (фиг,2 à, r) Задержка блока 2 регулируемой задержки устанавливается таким образом, чтобы срез (фронт) тактового сигнала был задержан относительно фронта информационного на величину задержки, ориентировочно равную 2-3 по (фиг.2д), В результате логического суммирования на выходе элемента ИЛИ 8 формируется униполярная последовательность импульсов

HDB-3 кода (фиг,2е). Этот сигнал поступает на вход второго регистра 5 сдвига, на выходах которого формируется сигнал с уровнем логического нуля в случае, когда число нулей подряд во входной последовательности будет больше трех (фиг.2ж).

На выходе элемента ИЛИ-НЕ 11 будет формироваться последовательность импульсов ошибок (фиг.2з), свидетельствующих о нарушении алгоритма кодирования при пропаданиях или "замираниях" входного сигнала. Селектор 1 импульсов формирует на своих выходах последовательности первых и вторых импульсов в модах одной полярности сигналов в коде HDB-3 (фиг.2и,к).Последовательность первых импульсов (фиг.2и) поступает на информационный вход первого регистра 4 сдвига ° Сигнал с инверсного выхода четвертого разряда регистра 4 сдвига, проходя элемент ИЛИ-НЕ 12, идентифицирует состояние ВОО. Состояние ООЧ идентифицируется элементом ИЛИ 9. На выходе элемента ИЛИ-НЕ 12 (фиг, 2м) будут сформированы импульсы, соответствующие импульсам V в моде BOOV, а на выходе элемента ИЛИ-НЕ 13 — BOOOV.

Сигнал с выхода второго разряда третьего регистра 6, проходя через элемент ИЛИ-НЕ 13, идентифицирует состояние 1000 (BOOO).

Состояние триггера 3 (фиг. 2н) изменяется с приходом каждого В (В ) 1432781 импульса, а каждый Ч-импульс с выхода элементов ИЛИ-НЕ 12, 13 переводит триггер 3 в единичное состояние (фиг.2о), обеспечивая формирование импульсов V на выходах элементов

ИЛИ-HF. 12, 13 только в том случае, когда между двумя V-вставками, будет Ф нечетное число импульсов В (В ).

Четвертый регистр 7 сдвига обеспечивает у себя на выходе Ч-вставки, которые не соответствуют алгоритму кодирования. На выходе элементов

ИЛИ-НЕ 12 13 будут сформированы Ч15 вставки иэ мод ВОООЧ или BOOV при условии нечетности количества импульсов В между двумя Ч-вставками, Все вторые импульсы поступают на вход первого разряда регистра 7 сдвига.

Одновременно на R вход этого разряда 7.1 поступают импульсы из мод

ВООЧ и BOOOV, обнуляя правильные Увставки. Таким образом, на выходе элемента ИЛИ-HF. 14 будет сформирована последовательность ошибочных V-импульсов (фиг;2п), не соответствующая алгоритму кодирования. На фиг.2р показаны декодированные сигналы.

Таким образом благодаря выявлению всех ошибочных V-вставок, а также пропаданий входного сигнала точность декодирования у предлагаемого устройства выше, чем у известного.

Формула и з о б р е т е н и я

Декодирующее устройство, содержащее селектор импульсов, первый и второй входы которого являются одноименными информационными входами устройства, первый выход соединен с информационным входом первого регистра . сдвига, тактовый вход которого через блок регулируемой задержки подключен к тактовому входу устройства,первый выход первого регистра сдвига является информационным выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности деко,дирования, в устройство введены второй — четвертый регистры сдвига, первый — третий элементы ИЛИ, первый— четвертый элементы ИЛИ-НЕ и триггер, тактовый вход которого подключен к первому выходу селектора импульсов, второй выход которого соединен с первыми входами второго и третьего элементов ИЛИ и информационным входом четвертого регистра сдвига, выход которого соединен с первым входом четвертого элемента ИЛИ-НЕ, второй вход которого объединен с первым входом первого элемента ИЛИ-HF. и тактовыми входами второго — четвертого регистров сдвига и подключен к выходу блока регулируемой задержки, первый и второй входы первого элемента ИЛИ подключены к соответствующим информационным входам устройства, выход первого элемента ИЛИ соединен с информационным входом второго регистра сдвига, выходы разрядов которого соединены с вторыми входами первого элемента ИЛИ-НЕ, выход которого объединен с выходом четвертого элемента ИЛИ-HF и является контрольным выходом устройства, второй выход первого регистра сдвига соединен с вторым входом второго элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ-НЕ и второму входу третьего элемента ИЛИ, выход которого соединен с первым входом третьего элемента ИЛИ-НЕ, выход которого и вы ход второго элемента ИЛИ-HE подключены к входам обнуления первого, третьего и четвертого регистров сдвига и триггера, инверсный выход которого соединен с его информационным входом и" вторым входом второго и третьего элементов ИЛИ-НЕ, третий выход первого регистра сдвига соединен с третьим входом второго элемента ИЛИ и информационным входом третьего регистра сдвига, четвертый выход первого и первый и второй выходы третьего регистров сдвига подключены к третьим входам соответственно второго элемента ИЛИ-НЕ и третьих элементов ИЛИ и ИЛИ-НЕ.

1432781

Составитель О.Ревинский

Техред И.Верес

Корректор В. Бутяг а

Редактор С.Пекарь

Заказ 54б4/55

Тираж 929

Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

1t3035, Москва, Ж-35, Раутская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4